一种基于MOS管的正负压控制电路的制作方法

一种基于mos管的正负压控制电路

技术领域

[0001]

本发明属于集成电路设计与制造技术领域,具体涉及一种mos管电路改造技术。

背景技术:

[0002]

随着通讯系统的迅速发展,射频系统对射频开关芯片的要求越来越高。绝缘体上硅工艺soi在插损、隔离度、耐功率等方面有着显著的优势,在近几年的射频开关产品设计中得到了广泛的使用。随着集成电路soi制造工艺的不断发展,晶体管的尺寸越来越小,其工作电压也随之越来越低。在开关设计中,+3.3/-3控制显著提升开关的线性度、1db压缩点以及隔离度。在先进soi工艺中,如图1所示,射频开关管的栅极需要+3.3/-3v控制,体端口需要0/-3v控制。在仅有工作电压为2.5v的mos管的情况下,实现+3.3/-3v和0/-3v控制,是先进soi工艺下射频开关设计的难点之一。

技术实现要素:

[0003]

本发明为了解决现有技术存在的问题,提出了一种基于mos管的正负压控制电路,为了实现上述目的,本发明采用了以下技术方案。

[0004]

电路包括第一反相器、第二反相器、正压域电压变换模块、负压域电压变换模块、第一输出级、第二输出级,输入正压低电平信号,采用正负压供电,提高信号电平值,输出正负压高电平信号。

[0005]

第一反相器的的输入端作为电路的输入,第一反相器的输出端连接第二反相器的输入端、正压域电压变换模块的第一输入端和负压域电压变换模块的第一输入端,第二反相器的输出端连接正压域电压变换模块第二输入端和负压域电压变换模块的第二输入端。

[0006]

正压域电压变换模块的第一、第二、第三、第四输出端连接第一输出级的第一、第二、第三、第四输入端,负压域电压变换模块的第一、第二、第三、第四输出端连接第一输出级的第七、第八、第九、第十输入端。

[0007]

正压域电压变换模块的第五输出端和负压域电压变换模块的第五输出端经两个电阻r1串联,中间抽头连接第一输出级的的第五输入端,正压域电压变换模块的第六输出端和负压域电压变换模块的第六输出端经另外两个电阻r1串联,中间抽头连接第一输出级的的第六输入端。

[0008]

第一输出级的第一、第二输出端作为电路的第一、第二输出,连接第二输出级的第一、第二输入端,负压域电压变换模块的第一、第二输出端连接第二输出级的第四、第三输入端,第二输出级的第一、第二输出端作为电路的第三、第四输出。

[0009]

正压域电压变换模块采用左右对称设计,包括八个电阻r4、四个电阻r3、四个电阻r2和四个pmos管、八个nmos管。

[0010]

左一、左二、左三、左四电阻r4串联,左一、左二电阻r4的中间抽头作为第二输出端,左三、左四电阻r4的中间抽头作为第三输出端,左一电阻r4连接左六pmos管的源极,左四电阻r4连接左三nmos管的源极。

[0011]

左四nmos管和左五pmos管共漏连接左二、左三电阻r4的中间抽头作为第五输出端,左四nmos管的源极连接左三nmos管的漏极。

[0012]

左二nmos管的源极连接左一nmos管的漏极,左一nmos管和左三nmos管共栅、共源连接,共栅极经左一电阻r2作为第一输入端,左二电阻r2并联共栅极和共源极。

[0013]

右一、右二、右三、右四电阻r4串联,右一、右二电阻r4的中间抽头作为第一输出端,右三、右四电阻r4的中间抽头作为第四输出端,右一电阻r4连接右六pmos管的源极,右四电阻r4连接右三nmos管的源极。

[0014]

右四nmos管和右五pmos管共漏连接右二、右三电阻r4的中间抽头作为第六输出端,右四nmos管的源极连接右三nmos管的漏极。

[0015]

右二nmos管的源极连接右一nmos管的漏极,右一nmos管和右三nmos管共栅、共源连接,共栅极经右一电阻r2作为第二输入端,右二电阻r2并联共栅极和共源极。

[0016]

左一电阻r3并联右六pmos管的栅极和源极,右一电阻r3并联左六pmos管的栅极和源极,左二nmos管的漏极经左二电阻r3连接右六pmos管的栅极,右二nmos管的漏极经右二电阻r3连接左六pmos管的栅极。

[0017]

左六pmos管和右六pmos管共源作为正供电端,左三nmos管和右三nmos管共源作为负供电端。

[0018]

负压域电压变换模块采用左右对称设计,包括八个电阻r8、四个电阻r7、两个电阻r5、两个电阻r6和四个nmos管、八个pmos管。

[0019]

左一、左二、左三、左四电阻r8串联,左一、左二电阻r8的中间抽头作为第二输出端,左三、左四电阻r8的中间抽头作为第三输出端,左一电阻r8连接左九pmos管的源极,左四电阻r8连接左十二nmos管的源极。

[0020]

左十pmos管和左十一nmos管共漏连接左二、左三电阻r8的中间抽头作为第六输出端,左十pmos管的源极连接左九pmos管的漏极,左十一nmos管的源极连接左十二nmos管的漏极。

[0021]

左二电阻r7并联左十二nmos管的的栅极和源极,栅极经左一电阻r7连接左八pmos管的漏极,源极经左一电阻r6连接左七pmos管的栅极,左八pmos管的源极连接左七pmos管的漏极。

[0022]

右一、右二、右三、右四电阻r8串联,右一、右二电阻r8的中间抽头作为第一输出端,右三、右四电阻r8的中间抽头作为第四输出端,右一电阻r8连接右九pmos管的源极,右四电阻r8连接右十二nmos管的源极。

[0023]

右十pmos管和右十一nmos管共漏连接右二、右三电阻r8的中间抽头作为第五输出端,右十pmos管的源极连接右九pmos管的漏极,右十一nmos管的源极连接右十二nmos管的漏极。

[0024]

右二电阻r7并联右十二nmos管的的栅极和源极,栅极经右一电阻r7连接右八pmos管的漏极,源极经右一电阻r6连接右七pmos管的栅极,右八pmos管的源极连接右七pmos管的漏极。

[0025]

左七pmos管和右九pmos管共栅、共源连接,共栅极经左一电阻r5作为第一输入端,共源极连接左九pmos管的源极。

[0026]

右七pmos管和左九pmos管共栅、共源连接,共栅极经右一电阻r5作为第二输入端,

共源极连接右九pmos管的源极。

[0027]

左七pmos管和右七pmos管共源作为正供电端,左十二nmos管和右十二nmos管共源作为负供电端。

[0028]

第一输出级采用左右对称设计,包括八个pmos管和八个nmos管。

[0029]

左二十nmos管和左二十一pmos管共栅作为第五输入端,共漏作为第二输出端;左二十nmos管的源极连接左十九nmos管的漏极,左二十一pmos管的源极连接左二十二pmos管的漏极。

[0030]

左十九nmos管的栅极作为第七输入端,源极连接左十八nmos管的漏极;左十七nmos管的栅极作为第九输入端,漏极连接左十八nmos管的源极。

[0031]

左二十二pmos管的栅极作为第三输入端,源极连接左二十三pmos管的漏极;左二十四pmos管的栅极作为第一输入端,漏极连接左二十三pmos管的源极。

[0032]

右二十nmos管和右二十一pmos管共栅作为第六输入端,共漏作为第一输出端;右二十nmos管的源极连接右十九nmos管的漏极,右二十一pmos管的源极连接右二十二pmos管的漏极。

[0033]

右十九nmos管的栅极作为第八输入端,源极连接右十八nmos管的漏极;右十七nmos管的栅极作为第十输入端,漏极连接右十八nmos管的源极。

[0034]

右二十二pmos管的栅极作为第四输入端,源极连接右二十三pmos管的漏极;右二十四pmos管的栅极作为第二输入端,漏极连接右二十三pmos管的源极。

[0035]

左二十四pmos管和右二十四pmos管共源作为正供电端,左十七nmos管和右十七nmos管共源作为负供电端。

[0036]

第二输出级采用左右对称设计,包括四个pmos管、四个nmos管和两个电阻r9、两个电阻r10以及两个二极管组。

[0037]

左十五pmos管和左十四nmos管共漏作为第一输出端,左十五pmos管的源极连接左十六pmos管的漏极,左十六pmos管的栅极作为第四输入端。

[0038]

左十四nmos管的源极连接左十三nmos管的漏极,左一电阻r10并联左十三nmos管的栅极和源极,左二极管组的正极作为第一输入端,负极经左一电阻r9连接左十三nmos管的栅极。

[0039]

右十五pmos管和右十四nmos管共漏作为第二输出端,右十五pmos管的源极连接右十六pmos管的漏极,右十六pmos管的栅极作为第三输入端。

[0040]

右十四nmos管的源极连接右十三nmos管的漏极,右一电阻r10并联右十三nmos管的栅极和源极,右二极管组的正极作为第二输入端,负极经右一电阻r9连接右十三nmos管的栅极。

[0041]

左十六pmos管和右十六pmos管共源作为正供电端,左十三nmos管和右十三nmos管共源作为负供电端。

[0042]

mos管采用2.5v工艺,电阻r1、r2、r3、r4、r5、r6、r7、r8、r9、r10采用数千欧姆,其中r5/r6=25/33,r9/r10=23/33,二极管组d15采用5个0.7v二极管串联。

[0043]

第一、第二反相器采用2.5v供电,正压域电压变换模块的正供电端采用3.3v供电,负供电端接地,负压域电压变换模块的正供电端接地,负供电端采用-3.3v供电,第一输出级的正供电端采用3.3v供电,负供电端采用-3.3v供电,第二输出级的正供电端接地,负供

电端采用-3.3v供电。

[0044]

左二、左四、左五、左二十三、右二、右四、右五、右二十三mos管的栅极采用1.65v供电,左八、左十、左十一、左十四、左十五、左十八、右八、右十、右十一、右十四、右十五、右十八mos管的栅极采用-1.65v供电。

[0045]

分别输入控制信号的高低电平0/2.5v,第一反相器101输出2.5v/0,第二反相器输出0/2.5v,各mos管相应的导通或关断,各节点呈现高低电平。

[0046]

正压域电压变换模块输入输出电平:

[0047]

第一输入端2.5v/0,第五输出端0/3.3v,第三输出端0/1.65v,第二输出端1.65v/3.3v,第二输入端0/2.5v,第六输出端3.3v/0,第一输出端3.3v/1.65v,第四输出端1.65v/0。

[0048]

负压域电压变换模块输入输出电平:

[0049]

第一输入端2.5v/0,第五输出端-3.3v/0,第一输出端-1.65v/0,第四输出端-3.3v/-1.65v,第二输入端0/2.5v,第六输出端0/-3.3v,第三输出端-1.65v/-3.3v,第二输出端0/-1.65v。

[0050]

第一输出级输入输出电平:

[0051]

第一输入端3.3v/1.65v,第二输入端1.65v/3.3v,第三输入端0/1.65v,第四输入端1.65v/0,第五输入端-1.65v/1.65v,第六输入端1.65v/-1.65v,第七输入端-1.65v/0,第八输入端0/-1.65v,第九输入端-1.65v/-3.3v,第十输入端-3.3v/-1.65v,第一输出端3.3v/-3v,第二输出端-3v/3.3v。

[0052]

第二输出级输入输出电平:

[0053]

第一输入端3.3v/-3v,第二输入端-3v/3.3v,第三输入端0/-1.65v,第四输入端-1.65v/0,第一输出端0/-3v,第二输出端-3v/0。

[0054]

输入信号从-3v上升至0.5v,二极管组未导通,mos管的栅极电平保持-3v;输入信号超过0.5v,二极管组导通,压降为0.7v乘以5,mos管的栅极电平为输入信号减去3.5v。

[0055]

各mos管任意两端口压差小于等于2.5v,处于安全工作的电压范围。

[0056]

本发明在仅有较低工作电压mos管的情况下,输出较高电压值的正负电压控制信号,使开关mos管正常工作,解决了栅极与体端口控制的时序问题,避免栅极与体端口压差过大击穿开关mos管,实现了射频开关管的负压控制。

附图说明

[0057]

图1是mos管导通关断原理图,图2是电路结构原理图,图3是正压域电压变换模块电路原理图,图4是负压域电压变换模块电路原理图,图5是第一输出级电路原理图,图6是第二输出级电路原理图,图7是正压域电压变换模块各节点电平示意图,图8是负压域电压变换模块各节点电平示意图,图9是第一输出级各节点电平示意图,图10是第二输出级各节点电平示意图,图11是未采用二极管组的开关mos管端口电平波形图,图12是采用二极管组的开关mos管端口电平波形图。

[0058]

附图标记:101-反相器、102-正压域电压变换模块、103-负压域电压变换模块、104-第一输出级、105-第二输出级、m1l

……

m24l-左一mos管

……

左二十四mos管、m1r

……

m24r-右一mos管

……

右二十四mos管、v2l-左十三mos管的栅极电平、v2r-右十三mos管的栅

极电平。

具体实施方式

[0059]

以下结合附图,以2.5v工艺mos管为例,对本发明的技术方案做具体的说明。

[0060]

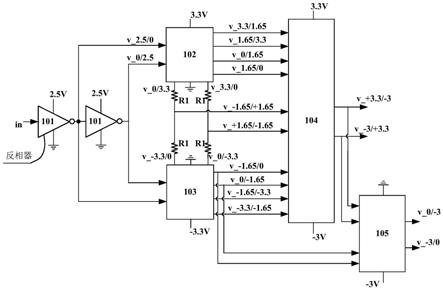

电路包括第一反相器101、第二反相器101、正压域电压变换模块102、负压域电压变换模块103、第一输出级104、第二输出级105,原理如图2所示:

[0061]

第一反相器101的的输入端作为电路的输入,第一反相器101的输出端连接第二反相器101的输入端、正压域电压变换模块102的第一输入端和负压域电压变换模块103的第一输入端,第二反相器101的输出端连接正压域电压变换模块102第二输入端和负压域电压变换模块103的第二输入端。

[0062]

正压域电压变换模块102的第一、第二、第三、第四输出端连接第一输出级104的第一、第二、第三、第四输入端,负压域电压变换模块103的第一、第二、第三、第四输出端连接第一输出级104的第七、第八、第九、第十输入端。

[0063]

正压域电压变换模块102的第五输出端和负压域电压变换模块103的第五输出端经两个电阻r1连接,中间抽头连接第一输出级104的的第五输入端,正压域电压变换模块102的第六输出端和负压域电压变换模块103的第六输出端经两个电阻r1连接,中间抽头连接第一输出级104的的第六输入端。

[0064]

第一输出级104的第一、第二输出端作为电路的第一、第二输出,连接第二输出级105的第一、第二输入端,负压域电压变换模块103的第一、第二输出端连接第二输出级105的第四、第三输入端,第二输出级105的第一、第二输出端作为电路的第三、第四输出。

[0065]

正压域电压变换模块102采用左右对称设计,原理如图3所示:

[0066]

左一、左二、左三、左四电阻r4串联,左一、左二电阻r4的中间抽头作为第二输出端,左三、左四电阻r4的中间抽头作为第三输出端,左一电阻r4连接左六pmos管m6l的源极,左四电阻r4连接左三nmos管m3l的源极。

[0067]

左四nmos管m4l和左五pmos管m5l共漏连接左二、左三电阻r4的中间抽头作为第五输出端,左四nmos管m4l的源极连接左三nmos管m3l的漏极。

[0068]

左二nmos管m2l的源极连接左一nmos管m1l的漏极,左一nmos管m1l和左三nmos管m3l共栅、共源连接,共栅极经左一电阻r2作为第一输入端,左二电阻r2并联共栅极和共源极。

[0069]

右一、右二、右三、右四电阻r4串联,右一、右二电阻r4的中间抽头作为第一输出端,右三、右四电阻r4的中间抽头作为第四输出端,右一电阻r4连接右六pmos管m6r的源极,右四电阻r4连接右三nmos管m3r的源极。

[0070]

右四nmos管m4r和右五pmos管m5r共漏连接右二、右三电阻r4的中间抽头作为第六输出端,右四nmos管m4r的源极连接右三nmos管m3r的漏极。

[0071]

右二nmos管m2r的源极连接右一nmos管m1r的漏极,右一nmos管m1r和右三nmos管m3r共栅、共源连接,共栅极经右一电阻r2作为第二输入端,右二电阻r2并联共栅极和共源极。

[0072]

左一电阻r3并联右六pmos管m6r的栅极和源极,右一电阻r3并联左六pmos管m6l的栅极和源极,左二nmos管m2l的漏极经左二电阻r3连接右六pmos管的栅极,右二nmos管m2r

的漏极经右二电阻r3连接左六pmos管的栅极。

[0073]

左六pmos管m6l和右六pmos管m6r共源作为正供电端,左三nmos管m3l和右三nmos管m3r共源作为负供电端。

[0074]

负压域电压变换模块103采用左右对称设计,原理如图4所示:

[0075]

左一、左二、左三、左四电阻r8串联,左一、左二电阻r8的中间抽头作为第二输出端,左三、左四电阻r8的中间抽头作为第三输出端,左一电阻r8连接左九pmos管m9l的源极,左四电阻r8连接左十二nmos管m12l的源极。

[0076]

左十pmos管m10l和左十一nmos管m11l共漏连接左二、左三电阻r8的中间抽头作为第六输出端,左十pmos管m10l的源极连接左九pmos管m9l的漏极,左十一nmos管m11l的源极连接左十二nmos管m12l的漏极。

[0077]

左二电阻r7并联左十二nmos管m12l的的栅极和源极,栅极经左一电阻r7连接左八pmos管m8l的漏极,源极经左一电阻r6连接左七pmos管m7l的栅极,左八pmos管m8l的源极连接左七pmos管m7l的漏极。

[0078]

右一、右二、右三、右四电阻r8串联,右一、右二电阻r8的中间抽头作为第一输出端,右三、右四电阻r8的中间抽头作为第四输出端,右一电阻r8连接右九pmos管m9r的源极,右四电阻r8连接右十二nmos管m12r的源极。

[0079]

右十pmos管m10r和右十一nmos管m11r共漏连接右二、右三电阻r8的中间抽头作为第五输出端,右十pmos管m10r的源极连接右九pmos管m9r的漏极,右十一nmos管m11r的源极连接右十二nmos管m12r的漏极。

[0080]

右二电阻r7并联右十二nmos管m12r的的栅极和源极,栅极经右一电阻r7连接右八pmos管m8r的漏极,源极经右一电阻r6连接右七pmos管m7r的栅极,右八pmos管m8r的源极连接右七pmos管m7r的漏极。

[0081]

左七pmos管m7l和右九pmos管m9r共栅、共源连接,共栅极经左一电阻r5作为第一输入端,共源极连接左九pmos管m9l的源极。

[0082]

右七pmos管m7r和左九pmos管m9l共栅、共源连接,共栅极经右一电阻r5作为第二输入端,共源极连接右九pmos管m9r的源极。

[0083]

左七pmos管m7l和右七pmos管m7r共源作为正供电端,左十二nmos管m12l和右十二nmos管m12r共源作为负供电端。

[0084]

第一输出级104采用左右对称设计,原理如图5所示:

[0085]

左二十nmos管m20l和左二十一pmos管m21l共栅作为第五输入端,共漏作为第二输出端;左二十nmos管m20l的源极连接左十九nmos管m19l的漏极,左二十一pmos管m21l的源极连接左二十二pmos管m22l的漏极。

[0086]

左十九nmos管m19l的栅极作为第七输入端,源极连接左十八nmos管m18l的漏极;左十七nmos管m17l的栅极作为第九输入端,漏极连接左十八nmos管m18l的源极。

[0087]

左二十二pmos管m22l的栅极作为第三输入端,源极连接左二十三pmos管m23l的漏极;左二十四pmos管m24l的栅极作为第一输入端,漏极连接左二十三pmos管m23l的源极。

[0088]

右二十nmos管m20r和右二十一pmos管m21r共栅作为第六输入端,共漏作为第一输出端;右二十nmos管m20r的源极连接右十九nmos管m19r的漏极,右二十一pmos管m21r的源极连接右二十二pmos管m22r的漏极。

[0089]

右十九nmos管m19r的栅极作为第八输入端,源极连接右十八nmos管的漏极;右十七nmos管m17r的栅极作为第十输入端,漏极连接右十八nmos管的源极。

[0090]

右二十二pmos管m22r的栅极作为第四输入端,源极连接右二十三pmos管m23r的漏极;右二十四pmos管m24r的栅极作为第二输入端,漏极连接右二十三pmos管m23r的源极。

[0091]

左二十四pmos管m24l和右二十四pmos管m24r共源作为正供电端,左十七nmos管m17l和右十七nmos管m17r共源作为负供电端。

[0092]

第二输出级105采用左右对称设计,原理如图6所示:

[0093]

左十五pmos管m15l和左十四nmos管m14l共漏作为第一输出端,左十五pmos管m15l的源极连接左十六pmos管m16l的漏极,左十六pmos管m16l的栅极作为第四输入端。

[0094]

左十四nmos管m14l的源极连接左十三nmos管m13l的漏极,左一电阻r10并联左十三nmos管m13l的栅极和源极,左二极管组d15的正极作为第一输入端,负极经左一电阻r9连接左十三nmos管m13l的栅极。

[0095]

右十五pmos管m15r和右十四nmos管m14r共漏作为第二输出端,右十五pmos管m15r的源极连接右十六pmos管m16r的漏极,右十六pmos管m16r的栅极作为第三输入端。

[0096]

右十四nmos管m14r的源极连接右十三nmos管m13r的漏极,右一电阻r10并联右十三nmos管m13r的栅极和源极,右二极管组d15的正极作为第二输入端,负极经右一电阻r9连接右十三nmos管m13r的栅极。

[0097]

左十六pmos管m16l和右十六pmos管m16r共源作为正供电端,左十三nmos管m13l和右十三nmos管m13r共源作为负供电端。

[0098]

第一、第二反相器101采用2.5v供电,正压域电压变换模块102的正供电端采用3.3v供电,负供电端接地,负压域电压变换模块103的正供电端接地,负供电端采用-3.3v供电,第一输出级104的正供电端采用3.3v供电,负供电端采用-3.3v供电,第二输出级105的正供电端接地,负供电端采用-3.3v供电。

[0099]

左二mos管m2l、左四mos管m4l、左五mos管m5l、左二十三mos管m23l、右二mos管m2r、右四mos管m4r、右五mos管m5r、右二十三mos管m23r的栅极采用1.65v供电,左八mos管m8l、左十mos管m10l、左十一mos管m11l、左十四mos管m14l、左十五mos管m15l、左十八mos管m18l、右八mos管m8r、右十mos管m10r、右十一mos管m11r、右十四mos管m14r、右十五mos管m15r、右十八mos管m18r的栅极采用-1.65v供电。

[0100]

电阻r1、r2、r3、r4为20千欧,r5为25千欧,r6为33千欧,r7、r8为20千欧,r9为23千欧,r10为33千欧,其中r5/r6=25/33,r9/r10=23/33,二极管组d15采用5个0.7v二极管串联。

[0101]

分别输入控制信号的高低电平0/2.5v,第一反相器101输出2.5v/0,第二反相器输出0/2.5v,各mos管相应的导通或关断,各节点呈现高低电平。

[0102]

正压域电压变换模块102各节点电平如图7所示:

[0103]

第一输入端2.5v/0,m1l和m3l的共栅极1.25v/0,m2l和m4l的源极0/1.65v;m2l的漏极0/3.3v,m6r的栅极1.65v/3.3v,漏极3.3v/1.65v;第五输出端0/3.3v,第三输出端0/1.65v,第二输出端1.65v/3.3v。

[0104]

第二输入端0/2.5v,m1r和m3r的共栅极0/1.25v,m2r和m4r的源极1.65v/0;m2r的漏极3.3v/0,m6l的栅极3.3v/1.65v,漏极1.65v/3.3v;第六输出端3.3v/0,第一输出端

3.3v/1.65v,第四输出端1.65v/0。

[0105]

各mos管任意两端口压差小于等于2.5v,处于安全工作的电压范围。

[0106]

负压域电压变换模块103各节点电平如图8所示:

[0107]

第一输入端2.5v/0,m7l和m9r的共栅极0/-1.42v,m8l和m10r的源极-1.65v/0;m8l的漏极-3.3v/0,m12l的栅极-3.3v/-1.65v,漏极-1.65v/-3.3v;第五输出端-3.3v/0,第一输出端-1.65v/0,第四输出端-3.3v/-1.65v。

[0108]

第二输入端0/2.5v,m7r和m9l的共栅极-1.42v/0,m8r和m10l的源极0/-1.65v;m8r的漏极0/-3.3v,m12r的栅极-1.65v/-3.3v,漏极-3.3v/-1.65v;第六输出端0/-3.3v,第三输出端-1.65v/-3.3v,第二输出端0/-1.65v。

[0109]

各mos管任意两端口压差小于等于2.5v,处于安全工作的电压范围。

[0110]

第一输出级104各节点电平如图9所示:

[0111]

第一输入端3.3v/1.65v,第二输入端1.65v/3.3v,第三输入端0/1.65v,第四输入端1.65v/0,第五输入端-1.65v/1.65v,第六输入端1.65v/-1.65v,第七输入端-1.65v/0,第八输入端0/-1.65v,第九输入端-1.65v/-3.3v,第十输入端-3.3v/-1.65v。

[0112]

第一输出端3.3v/-3v,第二输出端-3v/3.3v。

[0113]

各mos管任意两端口压差小于等于2.5v,处于安全工作的电压范围。

[0114]

第二输出级105各节点电平如图10所示:

[0115]

第一输入端3.3v/-3v,第二输入端-3v/3.3v,第三输入端0/-1.65v,第四输入端-1.65v/0。

[0116]

第一输出端0/-3v,第二输出端-3v/0。

[0117]

输入信号从-3v上升至0.5v,二极管组未导通,使m13l的栅极电平v2l或m13r的栅极电平v2r保持-3v;输入信号超过0.5v,二极管组导通,压降为0.7v乘以5,使m13l的栅极电平v2l和m13r的栅极电平v2r为输入信号减去3.5v。

[0118]

未采用二极管组d15的开关mos管端口电平的波形如图11所示,采用二极管组d15的开关mos管端口电平的波形如图12所示,二极管组d15解决了开关mos管栅极与体端口控制的时序问题,避免了栅极与体端口压差过大击穿mos管。

[0119]

各mos管任意两端口压差小于等于2.5v,处于安全工作的电压范围。

[0120]

上述作为本发明的实施例,并不限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1