一种自动分配设备地址编号的电路结构的制作方法

1.本实用新型涉及现场控制器技术领域,特别是能自动分配设备地址编号的电路结构。

背景技术:

2.在现场控制器系统中,通常包含一个主控制器模块以及依次连接的多个i/o控制器模块,需要对同一条通讯总线中各个i/o控制器模块分配不同地址。现有技术中,通常使用拨码开关人为设置。这种地址分配方法的特点是实现简单、运行可靠,但是也存在着现场操作不方便,容易地址设置重复且没有对地址重复处理机制等问题。

技术实现要素:

3.针对上述现有技术中存在的不足,本实用新型的目的是提供一种自动分配设备地址编号的电路结构。它可以实现地址的自动分配,避免人为操作的错误,极大简化现场工作流程。

4.为了达到上述发明目的,本实用新型的技术方案以如下方式实现:

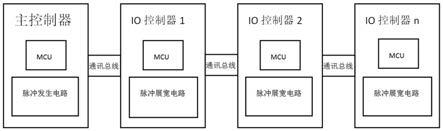

5.一种自动分配设备地址编号的电路结构,它包括由通讯总线连接的一个主控制器模块以及与多个i/o控制器模块。其结构特点是,所述主控制器模块和各i/o控制器模块中均置有单片机,所述主控制器模块内置脉冲发生电路,所述i/o控制器模块内置脉冲展宽电路。

6.在上述电路结构中,所述脉冲发生电路采用cd4060芯片二u5构成一个多级2分频器。一路电源给有源晶振二y2供电,有源晶振二y2连接到cd4060芯片二u5提供脉冲信号,另一路电源经由电阻和两个开关二极管组成的与门输入到cd4060芯片二u5,cd4060芯片二u5的vdd脚经去耦电容一c1接地。

7.在上述电路结构中,所述脉冲展宽电路包括cd4060芯片一u1,电源经有源晶振一y1输入给cd4060芯片一u1,cd4060芯片一u1的vdd脚经去耦电容三c3接地。主控制器模块的输出或者上一个i/o控制器模块的输出作为脉冲输入pulse_in,经由或非门二u2b、或非门一u2a组成的rs触发器输出得到扩展宽度后的脉冲输出,cd4060芯片一u1的引脚4连接到或非门一u2a的输入上。脉冲输入还依次经或非门四u2d、或非门三u2c回到cd4060芯片一u1的reset引脚。

8.本实用新型由于采用了上述结构,由主控制器模块发出脉冲,每一个i/o控制器依次对收到的脉冲进行展宽,得到不同的地址编码。同现有技术相比,本实用新型可以实现地址的自动分配,具有操作简便、编码无重复的特点。

9.下面结合附图和具体实施方式对本实用新型做进一步说明。

附图说明

10.图1为本实用新型的结构示意图;

11.图2为本实用新型中脉冲发生电路的示意图;

12.图3为图2的输出波形图;

13.图4本实用新型中脉冲展宽电路的示意图;

14.图5为图4中脉冲输入和脉冲输出波形图。

具体实施方式

15.参看图1、图2和图4,本实用新型自动分配设备地址编号的电路结构,包括由通讯总线连接的一个主控制器模块以及与多个i/o控制器模块,主控制器模块和i/o控制器模块中均置有单片机mcu。主控制器模块包括脉冲发生电路,脉冲发生电路采用cd4060芯片二u5构成一个多级2分频器,一路电源给有源晶振二y2供电,有源晶振二y2连接到cd4060芯片二u5提供脉冲信号,另一路电源经由电阻r7和两个开关二极管组成的与门输入到cd4060芯片二u5。cd4060芯片二u5的vdd脚经去耦电容一c1接地。每个i/o控制器模块均内置脉冲展宽电路,脉冲展宽电路包括cd4060芯片一u1,电源经有源晶振一y1输入给cd4060芯片一u1,cd4060芯片一u1的vdd脚经去耦电容三c3接地。主控制器模块的输出或者上一个i/o控制器模块的输出作为脉冲输入pulse_in,经由或非门二u2b、或非门一u2a组成的rs触发器输出得到扩展宽度后的脉冲输出pulse_out,cd4060芯片一u1的引脚4连接到或非门一u2a的输入上。脉冲输入pulse_in还依次经或非门四u2d、或非门三u2c回到cd4060芯片一u1的reset引脚。

16.本实用新型电路结构工作时,其原理为:

17.1、主控制器模块的核心是一个由cd4060芯片二u5构成的多级2分频器。通过分频器的2hz输出产生一个大约1/4秒(实际1/4秒+1/1024秒)周期的正脉冲,利用1024hz的脉冲产生一个1/2048秒的正脉冲(1024hz方波的正半周)。具体流程为:

18.1)电路中电阻r7和两个开关二极管组成与门。电路刚上电时,cd4060芯片二u5的各个输出均为低电平, 所以与门的输出也为低,因此cd4060芯片二u5的reset引脚为低电平,cd4060芯片二u5可以正常工作开始计时。

19.2)当q14引脚输出电平为低的时候, q4引脚的电平并不影响reset上面的电平。cd4060芯片二u5继续计时。

20.3)cd4060芯片二u5持续工作,经过一段时间t1后, q14引脚输出从低电平变为高电平,此时q4引脚必定为低电平, reset引脚为低,cd4060芯片二u5仍继续计时。

21.4)cd4060芯片二u5持续工作, q14引脚输出持续高电平。经过固定的时间t2后, q4引脚由低变高, reset引脚电平随之由低变高,cd4060芯片二u5被复位。然后重复第1)步刚上电时的情况。

22.5)最终输出采用cd4060芯片二u5的q14引脚,整个地址脉冲的周期由q4引脚和q14引脚共同确定,地址脉冲的高电平宽度由q4引脚确定。合理的选择cd4060芯片二u5输出管脚就可以灵活地控制各部分时间宽度。

23.6)参看图3,t1为q14引脚正常分频周期的一半,t2为q4引脚正常分频周期的一半,这样q14引脚输出的实际波形周期为t1+t2(细点线表示cd4060芯片二u5复位)。

24.2、每一个i/o控制器模块依次收到脉冲后对其接收的脉冲宽度增加1/2048秒,这样第一个i/o控制器模块收到脉冲宽度为1/2048秒,第二个i/o控制器模块收到的脉冲宽度

为2/2048秒,第三个i/o控制器模块收到的为3/2048秒

……

。这样每个i/o控制器模块就获得了不同宽度的地址脉冲,再由mcu识别脉冲宽度,就可以得到不同的地址编码。

25.脉冲展宽电路中,pulse_in为脉冲输入(主控制器模块输出或者上一个i/o控制器模块的输出pulse_out),pulse_out为扩展宽度后的脉冲输出。或非门u2a和或非门u2b组成了一个rs触发器。初始状态,cd4060芯片一u1所有输出均为低电平,上一级输入的脉冲来之前也是低电平,而rs触发器输出状态随机。具体流程为:

26.1)当cd4060芯片一u1刚上电时,假设rs触发器输出为上低下高,则cd4060芯片一u1处于复位状态,不计时。或非门一u2a输出低。

27.2)当输入脉冲来到时,或非门二u2b下输入变高,rs触发器翻转成输出上高下低,但是或非门四u2d下输入为高因此输出不变,cd4060芯片一u1仍处于复位状态,不计时。或非门一u2a输出高。

28.3)参看图5,经过时间t1当输入脉冲结束,rs触发器维持输出上高下低。或非门四u2d两个输入均变成低,或非门三u2c输出低,cd4060芯片一u1复位结束开始计时。或非门一u2a输出仍为高。

29.4)当cd4060芯片一u1计时时间到时,连接或非门一u2a的输出脚变高。rs触发器翻转为上低下高状态,reset引脚变高被复位,计时结束。cd4060芯片一u1所有的输出恢复全低,回到步骤3)状态。或非门一u2a输出低。脉冲被展宽了一个计时周期t3-t2,就是增加的1/2048秒。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1