基于ASI总线的IO模块的制作方法

基于asi总线的io模块

技术领域

[0001]

本实用新型涉及通信技术领域,具体涉及基于asi总线的io模块。

背景技术:

[0002]

asi(actuator-sensor-interface)是执行器-传感器-接口的英文缩写,它是一种用在控制器(主站)和传感器/执行器(从站)之间双向交换信息的总线网络,其具有接线简单,维护便利等特点,在工业应用中有很好的推广前景。

[0003]

asi总线下的传感器和执行器,即io控制点,通过基于asi总线的io模块能连接至asi网络,将离散的数字量输入信号,通过asi总线传输给主站,同时将来自主站的控制信号传输到输出点。

[0004]

如今,越来越多的分布式io设备已用于自动化控制现场区域,特别是为数众多的分散的传感器和执行器,作为直接在现场的智能前哨。因此,对asi总线的io容量提出了更高的要求,但是市场常见的产品以4点io以下模块为主。在asi3.0及以下标准中,每条asi总线最多可以挂载62个从站模块,其总的io容量是有限的,即4

×

62=248个io点,asi从站设备的容量受到了限制。

[0005]

另外,市面上也存在8个输入和8个输出的从站,但其实现的方法是把两个4i4o模块集成组装在一个外壳中,其本质还是通过两个4i4o从站来实现8i8o,一个模块占用两个asi从站地址,其总的io容量和通用4i4o从站是一样的,即4x62=248个io点位,难以满足现在自动化领域的需求。

技术实现要素:

[0006]

本实用新型为了解决现有技术存在的上述问题,提供了一种基于asi总线的io模块,扩大总线io容量,满足了自动化控制现场的扩充要求。

[0007]

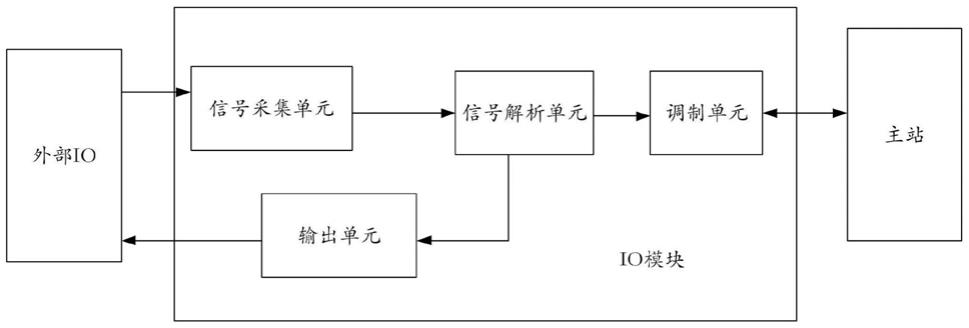

为实现上述目的,本实用新型提出了一种基于asi总线的io模块,包括信号采集单元、信号解析单元、调制单元以及输出单元,其中:

[0008]

当io模块接收从外部io输入进来的信号时:

[0009]

所述的信号采集单元将输入的信号发送至信号解析单元;

[0010]

所述信号解析单元按照asi协议对信号采集单元发送的信号进行解析与打包后,将打包的信号发送至调制单元;

[0011]

调制单元对信号解析单元发送的信号进行调制之后,将调制得到的信号发送至主站,

[0012]

当io模块接收从主站输出进来的信号时:

[0013]

所述调制单元对主站输出的信号进行解调,并将解调得到的信号发送至所述信号解析单元;

[0014]

所述信号解析单元按照asi协议对调制单元发出的解调信号进行解析后,选择将解析得到的信号发送至输出单元,并通过输出单元发送至外部io。

[0015]

进一步地,所述调制单元为具有asi总线调制功能的专用芯片。

[0016]

进一步地,所述专用芯片为asi4u。

[0017]

进一步地,所述信号解析单元为mcu。

[0018]

进一步地,所述asi协议定义的输入输出点位为8点位。

[0019]

进一步地,所述输出单元的传输协议为i2c协议。

[0020]

本实用新型可以使得每个从站模块接入8点io点位时,总线的io容量提高了一倍,具有极高的性价比推广价值。

附图说明

[0021]

下面结合附图和具体实施方式对本实用新型作进一步详细的说明。

[0022]

图1为本实用新型基于asi总线的io模块结构示意图。

[0023]

图2为本实用新型核心电气原理图;

[0024]

图3为本申请实施例输入时的信号流向连接示意图;

[0025]

图4为本申请实施例输出时的信号流向连接示意图。

[0026]

本实用新型目的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

[0027]

应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

[0028]

请参阅图1,图1为本申请基于asi总线的io模块结构示意图,包括调制单元,信号解析单元,信号采集单元以及输出单元。

[0029]

请参阅图2,图2为本申请io模块结构的具体实施例的电路原理图。

[0030]

本实施例中,所述调制单元为具有asi总线调制功能的专用芯片,优选地,信号调制单元采用具有asi总线调制功能的专用芯片asi4u。asi总线通过交变脉冲调制模式(apm)来实现调制,以曼彻斯特ⅱ方式并且以sin2形式的信号波形来传输信息。

[0031]

本实施例中,所述信号解析单元为mcu,优选地采用当前主流mcu芯片stm32f103单片机,根据asi3.0标准,对总线上的信号进行解析,对主站的请求按要求进行应答,完成8点io模块的主要功能。

[0032]

asi协议专用芯片asi4u芯片的端口工作电压为5v,单片机stm32f103的工作电压为3.3v,并且部分引脚可接受5v电压,当asi4u芯片给stm32f103传输信号时,在单片机侧选用5v兼容的引脚,直接连接;

[0033]

当stm32f103给asi4u芯片传输信号时,采用单片机开漏输出,外部上拉5v电平的方式,以满足协议芯片5v的要求。

[0034]

本实用新型所述输出单元基于i2c协议,通过对scl和sda线高低电平时序的控制,来所需要的信号进行信号的传递。

[0035]

本申请中,将从外部io发送过来的信号,经过本申请的io模块,最后发送至主站定义为“输入”,将从主站发送过来的信号,经过本申请的io模块,最后发送至外部io定义为“输出”。

[0036]

请参阅图3,图3为本申请实施例输入时的信号流向连接示意图,其信号流的方向

如图中的虚线所示,本申请实施例的输入信号通过光耦隔离后,直接进入单片机。

[0037]

所述信号采集单元的输入端口(input1

--

input8)接收从站输入的信号,并通过输出端口(pa7、pb0、pb1、pb1、pb2、pa3-pa6)将从站输入的信号发送至信号解析单元对应的输入端口(pa7、pb0、pb1、pb1、pb2、pa3-pa6);

[0038]

所述信号解析单元按照asi协议对信号采集单元发送的信号进行解析与打包后,将打包得到的信号通过其输出端口(pb8-pb15)发送至调制单元对应的端口(pb8-pb15);

[0039]

调制单元对信号解析单元发送的信号进行调制之后,将调制得到的信号通过asi总线(asi+/asi-)发送至主站。

[0040]

请参阅图4,图4为本申请实施例输出时的信号流向连接示意图,其信号流的方向如图中的虚线所示。

[0041]

主站通过asi总线(asi+/asi-)输出信号,所述调制单元对主站输出的信号进行解调,并将解调得到的信号通过端口(pb8-pb15)发送至所述信号解析单元;

[0042]

所述信号解析单元按照asi协议对调制单元发出的解调信号进行解析后,选择将解析得到的信号通过端口(p6、p7)发送至输出单元的端口(端口14、15),并通过输出单元的输出端口(output1至output8)发送至外部io。

[0043]

由此可见,本申请实施例的输入信号通过光耦隔离后,直接进入单片机stm32f103,输出信号采用了可扩展模式(以out_clk和out_dat两个信号,连接到输出单元上并以i2c的方式传递输出信息)。

[0044]

当用户只需要输入信号时,只提供8点输入功能,从而可以进一步减小模块的占用空间。

[0045]

当用户需要8点输出功能时,我们给通过扩展模式扩展为8i加8o的8点io模块。

[0046]

由此可见,本申请取得的技术效果为:

[0047]

本实用新型能够接入8点io点位,将总线的io容量提高了一倍,达到8

×

62=496个io点位,扩充了asi总线的地址范围。也就是说,和现有技术对比,一个8i8o模块只占用一个从站地址,一条总线上完全可以挂载62个从站模块,总线的io容量比市场上的产品扩大了一倍,即8x62=496个io点位。

[0048]

虽然以上描述了本实用新型的具体实施方式,但是本领域熟练技术人员应当理解,这些仅是举例说明,可以对本实施方式做出多种变更或修改,而不背离本实用新型的原理和实质,本实用新型的保护范围仅由所附权利要求书限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1