电压缓冲电路的制作方法

1.本发明涉及图像传感器技术领域,尤其涉及一种电压缓冲电路。

背景技术:

2.cmos图像传感器芯片在近年来不断得到发展,已逐渐取代ccd并广泛应用于各类便携式成像电子设备、安防监控设备、车载电子等。高帧率作为一个重要性能指标,直接影响到动态成像质量,成为设计者最关心的问题之一。

3.在cmos影像传感器中的诸多电路模块,用于实现不同的功能。在电路模块中的各个功能模块中,正常工作时需要基准电压源模块提供一个参考电压,大部分输出的参考电压都是供给到mos管的栅极。而在静态工作下mos管的栅极一般认为近似一个电容负载,是不通过电流的,因此作为参考电压输入输出使用的电压缓冲电路可以采用常规结构的双端输入单端输出的误差放大器,但是如果一些功能需求中,参考电压需要根据工作时序进行切换时,也就是说作为接收端的mos管的栅极电位在时域上是变化的,那么在栅极上就会产生充放电流,从而参考电压的电位就会有需要一个稳定过程。如果接收参考电压的mos器件数量较少,常规的电压缓冲电路还是能够满足应用需求的,但是如果有大量mos器件栅极同时连接到一个电压缓冲电路的输出端,传输的电压在不停切换时,电压缓冲电路就会产生驱动不足,电压稳定时间过长而达不到工作时序的要求,这样就限制工作时序的时间长度。

4.由于高频高帧率的性能需求,在以后的设计方向上cmos影像传感器的工作频率必定会逐渐增大,时序时间宽度也会降低,因此在模拟电路中,随时序切换的参考电压如果要驱动较大容性负载时,比如全阵列的adc功能电路,就需要转换速率高的电压缓冲电路来驱动。同时,电压缓冲电路输入输出范围还要足够大,以满足灵活的设计需求。高转换速率的电压缓冲电路主要特点就是输出能够快速响应输入的变化,在连接较大容性负载时,也就意味着当输入电压变化时,输出端可以提供较大的瞬时电流来让负载进行充电和放电。响应越快,瞬时电流越大,输出端电压的稳定时间就越短,这样就可以满足高频下模拟电路中时变参考电压的应用需求。

技术实现要素:

5.本发明的目的在于提供一种电压缓冲电路,能够提供较大的瞬时电流来让负载进行充电和放电,具有转换速率高,输入输出范围大的优点。

6.为了达到上述目的,本发明提供了一种电压缓冲电路,包括输入模块和输出模块。

7.输入模块包括第一差分放大器和第二差分放大器,所述第一差分放大器的反向输入端接于所述第二差分放大器的反向输入端,作为所述电压缓冲电路的输入端vin,用于接收输入电压,所述第一差分放大器的输出端和所述第二差分放大器的输出端分别输出第一电位信号和第二电位信号;

8.输出模块,包括驱动输出单元,所述驱动输出单元具有第一驱动mos管和第二驱动mos管,所述第一驱动mos管的源极接于电源vdd,栅极接于所述第二差分放大器的输出端,

漏极接于所述第一差分放大器的正向输入端、所述第二差分放大器的正向输入端和所述第二驱动mos管的漏极,作为所述电压缓冲电路的输出端vout,所述第二驱动mos管的栅极接于所述第一差分放大器的输出端,源极接于地端vss;

9.所述输出模块根据所述第一电位信号和所述第二电位信号,调节所述第一驱动mos管和所述第二驱动mos管的驱动电流,以使所述电压缓冲电路的输出端vout的电压跟随所述输入电压vin。

10.可选的,所述第一驱动mos管为pmos管,所述第二驱动mos管为nmos管。

11.可选的,所述输出模块还包括快速响应输出单元,所述快速响应输出单元用于接收所述第一电位信号和所述第二电位信号,并根据所述第一电位信号和所述第二电位信号的电压的变化产生充电电流、第三电位信号和第四电位信号,所述第一驱动mos管和所述第二驱动mos管接收所述第三电位信号和所述第四电位信号,并根据所述第三电位信号和所述第四电位信号的电压的变化调节所述驱动电流。

12.可选的,所述第一差分放大器为nmos输入对管的结构,所述第二差分放大器为pmos输入对管的结构。

13.可选的,所述电压缓冲电路中具有第一nmos管至第十一nmos管、第一pmos管至第十一pmos管、第一线性电容及第二线性电容;其中,所述第一驱动mos管为所述第十pmos管,所述第二驱动mos管为所述第十nmos管;所述输入模块为所述第一pmos管至所述第五pmos管及所述第一nmos管至所述第五nmos管;所述快速响应输出单元为所述第六pmos管至所述第七pmos管及所述第六nmos管至所述第七nmos管;所述驱动输出单元为所述第八pmos管、所述第九pmos管、所述第十一pmos管、所述第八nmos管、所述第九nmos管及所述第十一nmos管;

14.所述第一nmos管至第十一nmos管的衬底均接于所述地端vss,所述第一pmos管至第十一pmos管的衬底均接于所述电源vdd;

15.其中,所述第一nmos管的栅极接于所述输入端vin,所述第一nmos管的源极和所述第二nmos管的源极接于所述第三nmos管的漏极;所述第三nmos管的栅极接于第一偏置电压vbias1,源极接于所述地端vss;所述第一pmos管的栅极和所述第二pmos管的栅极接于所述第二pmos管的漏极,源极均接于所述电源vdd;所述第一pmos管的漏极接于所述第一nmos管的漏极,所述第二pmos管的漏极接于所述第二nmos管的漏极;所述第四pmos管的栅极接于所述输入端vin,所述第四pmos管的源极和所述第五pmos管的源极接于所述第三pmos管的漏极;所述第三pmos管的栅极接于第二偏置电压vbias2,源极接于所述电源vdd;所述第四nmos管的栅极和所述第五nmos管的栅极接于所述第五nmos管的漏极;所述第四nmos管的漏极接于所述第四pmos管的漏极,所述第五nmos管的漏极接于所述第五pmos管的漏极,源极接于所述地端vss;所述第六pmos管的栅极接于第三偏置电压vbias3,源极接于电源vdd;所述第七pmos管的栅极接于所述第一nmos管的漏极和所述第一线性电容的一端,漏极接于所述第一线性电容的另一端和所述第六nmos管的漏极;所述第七nmos管的栅极接于第四偏置电压vbias4,源极接于所述地端vss;所述第六nmos管的栅极接于所述第四nmos管的漏极和所述第二线性电容的一端,漏极接于所述第二线性电容的另一端;所述第八pmos管的栅极接于所述第七pmos管的栅极,源极接于所述电源vdd;所述第十一nmos管的源极接于所述地端vss,漏极接于所述第九pmos管的栅极和漏极,栅极接于所述第八pmos管的漏极;所述第

十pmos管的栅极接于所述第九pmos管的栅极,源极接于所述电源vdd;所述第十一pmos管的源极接于所述电源vdd,栅极接于所述第八nmos管的漏极和所述第八pmos管的漏极;所述第八nmos管的栅极接于所述第六nmos管的栅极,源极接于所述地端vss;所述第九nmos管与所述第十nmos管的栅极接于所述第九nmos管的漏极和所述第十一pmos管的漏极,源极接于所述地端vss;所述第十nmos管的漏极、所述第十pmos管的漏极、所述第二nmos管的栅极、所述第五pmos管的栅极、所述第七pmos管的漏极和所述第六nmos管的漏极相接后作为所述输出端vout。

16.可选的,所述输出模块和所述输入模块之间还设置有反馈单元。

17.可选的,所述快速响应输出单元还设置有上镜像电流支路及下镜像电流支路。

18.可选的,所述电压缓冲电路中具有第一nmos管至第十三nmos管、第一pmos管至第十三pmos管、第一线性电容及第二线性电容;其中,所述第一驱动mos管为所述第十pmos管,所述第二驱动mos管为所述第十nmos管;所述输入模块为所述第一pmos管至所述第五pmos管及所述第一nmos管至所述第五nmos管;所述快速响应输出单元为所述第六pmos管至所述第七pmos管及所述第六nmos管至所述第七nmos管;所述驱动输出单元为所述第八pmos管、所述第九pmos管、所述第十一pmos管、所述第八nmos管、所述第九nmos管及所述第十一nmos管;所述上下镜像电流支路为所述第十三pmos管及所述第十三nmos管;所述反馈单元为所述第十二pmos管及所述第十二nmos管;

19.所述第一nmos管至第十三nmos管的衬底均接于所述地端vss,所述第一pmos管至第十三pmos管的衬底均接于所述电源vdd;

20.其中,所述第一nmos管的栅极接于所述输入端vin,所述第一nmos管的源极和所述第二nmos管的源极接于所述第三nmos管的漏极;所述第三nmos管的栅极接于第一偏置电压vbias1,其源极接于所述地端vss;所述第一pmos管的栅极和所述第二pmos管的栅极接于所述第二pmos管的漏极,源极均接于所述电源vdd;所述第一pmos管的漏极接于所述第一nmos管的漏极,所述第二pmos管的漏极接于所述第二nmos管的漏极;所述输入端vin同时也接于所述第四pmos管的栅极,所述第四pmos管的源极和所述第五pmos管的源极接于所述第三pmos管的漏极;所述第三pmos管的栅极接于第二偏置电压vbias2,源极接于所述电源vdd;所述第四nmos管的栅极和所述第五nmos管的栅极接于所述第五nmos管的漏极;所述第四nmos管的漏极接于所述第四pmos管的漏极,所述第五nmos管的漏极接于所述第五pmos管的漏极,源极都接于所述地端vss;所述第六pmos管的栅极和所述第十三pmos管的栅极接于所述第六pmos管的漏极同时接于所述第七pmos管的源极;所述第七pmos管的栅极接于所述第一nmos管的漏极和所述第一线性电容的一端,漏极接于所述第一线性电容的另一端和所述第六nmos管的漏极;所述第七nmos管的栅极和所述第十三nmos管的栅极接于所述第七nmos管的漏极和所述第六nmos管的源极,源极均接于所述地端vss;所述第六nmos管的栅极接于所述第四nmos管的漏极和所述第二线性电容的一端,漏极接于所述第二线性电容的另一端;所述第八pmos管的栅极接于所述第七pmos管的栅极,源极接于所述电源vdd,漏极接于所述第十三pmos管的漏极和所述第十一nmos管的栅极;所述第十一nmos管的源极接于所述地端vss,漏极接于所述第九pmos管的栅极和漏极;所述第十pmos管的栅极接于所述第九pmos管的栅极,源极接于所述电源vdd;所述第十一pmos管的源极接于所述电源vdd,栅极接于所述第八nmos管的漏极和所述第十三nmos管的漏极;所述第八nmos管的栅极接于所述第

六nmos管的栅极,源极接地;所述第九nmos管的栅极与所述第十nmos管的栅极接于所述第九nmos管的漏极和所述第十一pmos管的漏极,源极接于所述地端vss;所述第十nmos管的漏极和所述第十pmos管的漏极接于作为所述输出端vout,同时接于所述第二nmos管的栅极和所述第五pmos管的栅极,所述第七pmos管的漏极和所述第六nmos管的漏极;所述第十二nmos管的栅极接于所述第十一nmos管的栅极,漏极接于所述第一nmos管的源极,源极接于所述地端vss;所述第十二pmos管的栅极接于所述第十一pmos管的栅极,漏极接于所述第四pmos管的源极,源极接于所述电源vdd。

21.可选的,所述第八pmos管和所述第八nmos管的栅极的面积大于所述第一nmos管至第七nmos管、所述第九nmos管至第十三nmos管、所述第一pmos管至第七pmos管和所述第九pmos管至第十三pmos管的栅极的面积。

22.可选的,所述第十pmos管和所述第十nmos管的器件尺寸大于所述第一nmos管至第九nmos管、所述第一nmos管至第十三nmos管、所述第一pmos管至第九pmos管和所述第十一pmos管至第十三pmos管的器件尺寸。

23.在本发明提供的电压缓冲电路中,输入模块包括第一差分放大器和第二差分放大器,所述第一差分放大器的反向输入端接于所述第二差分放大器的反向输入端,作为所述电压缓冲电路的输入端vin,用于接收输入电压,所述第一差分放大器的输出端和所述第二差分放大器的输出端分别输出第一电位信号和第二电位信号。在本发明中,所述第一差分放大器用于接收较高范围输入电压,所述第二差分放大器用于接收较低范围输入电压,使得电压缓冲电路能够接收全范围的输入电压。

24.输出模块包括驱动输出单元,所述驱动输出单元具有第一驱动mos管和第二驱动mos管,所述第一驱动mos管的源极接于电源vdd,栅极接于所述第二差分放大器的输出端,漏极接于所述第一差分放大器的正向输入端、所述第二差分放大器的正向输入端和所述第二驱动mos管的漏极,作为所述电压缓冲电路的输出端vout,所述第二驱动mos管的栅极接于所述第一差分放大器的输出端,源极接于地端vss。所述输出模块根据所述第一电位信号和所述第二电位信号,调节所述第一驱动mos管和所述第二驱动mos管的驱动电流,以使所述电压缓冲电路的输出端vout的电压跟随所述输入电压vin。

25.此外,所述输出模块还包括快速响应输出单元,所述快速响应输出单元用于接收所述第一电位信号和所述第二电位信号,并根据所述第一电位信号和所述第二电位信号的电压的变化产生充电电流、第三电位信号和第四电位信号,所述第一驱动mos管和所述第二驱动mos管接收所述第三电位信号和所述第四电位信号,并根据所述第三电位信号和所述第四电位信号的电压的变化调节所述驱动电流。让输出模块能够提供较大的瞬时电流来让负载进行充电和放电,快速调节输出电压以跟随输入电压,使得所述电压缓冲电路具有转换速率高的优点。

附图说明

26.图1为本发明实施例中的一种cmos图像传感器系统中参考电压的应用环境的示意图;

27.图2为本发明实施例中的一种常规的电压输出缓冲电路的原理图;

28.图3为本发明实施例中的两种类型差分放大器的电路图;

29.图4为本发明实施例中的大电容负载下常规电压输出缓冲电路和高转换速率电压输出缓冲电路的输入输出电压的波形示意图;

30.图5为本发明实施例中的电压输出缓冲电路的原理图;

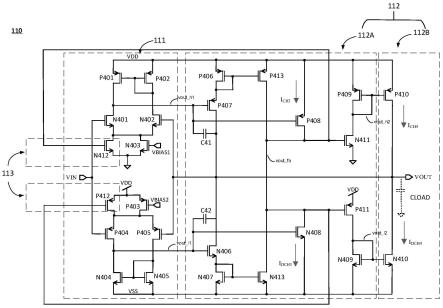

31.图6为本发明实施例中的电压输出缓冲电路的第一电路图;

32.图7为本发明实施例中的电压输出缓冲电路的第二电路图;

33.图8为本实施例中的第一现有的电压输出缓冲电路的电路图;

34.图9为本实施例中的第二现有的电压输出缓冲电路的电路图;

35.图10为本实施例中的第三现有的电压输出缓冲电路的电路图;

36.图11为本发明实施例中的第一仿真对比图;

37.图12为本发明实施例中的第二仿真对比图;

38.其中,附图标记如下:

39.100-基准电压源;110-电压输出缓冲电路;111-输入模块;112-输出模块;112a-快速响应输出单元;112b-驱动输出单元;113-反馈单元;

40.n401-第一nmos管;n402-第二nmos管;n403-第三nmos管;n404-第四nmos管;n405-第五nmos管;n406-第六nmos管;n407-第七nmos管;n408-第八nmos管;n409-第九nmos管;n410-第十nmos管;n411-第十一nmos管;n412-第十二nmos管;n413-第十三nmos管;

41.p401-第一pmos管;p402-第二pmos管;p403-第三pmos管;p404-第四pmos管;p405-第五pmos管;p406-第六pmos管;p407-第七pmos管;p408-第八pmos管;p409-第九pmos管;p410-第十pmos管;p411-第十一pmos管;p412-第十二pmos管;p413-第十三pmos管;c41-第一线性电容;c42-第一线性电容;

42.cload-负载电容。

具体实施方式

43.下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

44.图1为一种cmos图像传感器系统中参考电压的应用环境的示意图。如图1所示,基准电压源100为其它各个电路模块提供参考电压,所述参考电压的电压值通常需要稳定,不随外环境变化而变化。所述基准电压源110的输出电压本身不具备驱动能力,如果直接由一根导线传输到负载,该参考电压将很容易受到影响。主要原因是导线本身具有一定的寄生阻抗和容抗,而且负载端产生的噪声信号将会无损反馈回基准电压源100,继而影响所述基准电压源100。因此基准电压源100需要一个电压输出缓冲电路110用来作为电压传输的桥梁,所述电压输出缓冲电路110既可以提供一定的驱动能力和抗干扰能力给负载,又可以隔离负载端的噪声信号,保证基准电压源100稳定工作。

45.图2为一种常规的电压输出缓冲电路的原理图。

46.如图2所示,电压输出缓冲电路110的常规方式采用一个双端输入单端输出的差分放大器,所述差分放大器的反向端接于输出端,输出电压vout的电压值大小跟随输入端vin电压值。

47.图3为两种类型差分放大器的电路图。如图3所示,差分放大器包括n型输入对管

ea1和p型输入对管ea2这两种类型,图3中vin_p为正向输入端(对应图2中的符号“+”),vin_n为负向输入端(对应图2中的符号

“‑”

)。所述差分放大器的输入输出电压的范围是有限制的,因为n型输入对管ea1输入电压不能低于一个nmos管开启阈值和一个nmos管过驱动电压,同时输出电压不能低于两个nmos管的过驱动电压之和,同理,p型输入对管ea2输入输出电压也不能过高。两种类型的差分放大器不仅输入输出范围有限,更重要的是其驱动能力有限。对于图1中大部分电路模块例如dac、ldo和ts,只用来提供固定参考电压是可以满足需求。但是一些电路模块需要随时序变化的参考电压信号,例如图1中的电路模块pixel array和adc columns,由电路模块digital control输出控制信号到基准电压源110中,使得电压输出缓冲电路110的输入端电压变化,从设计上希望该变化的电压能够无差异的传输到电路模块pixel array和adc columns中。这些接收参考电压的电路模块对于电压输出缓冲电路110而言即为负载,且绝大部分都是可以等效为负载电容cload。当有电压变化时,负载电容cload需要充电流或者放电流,由电容的电气特性可知需要的充放电流i为:

[0048][0049]

其中,c为负载电容cload的电容值,dv为负载端的电压的变化量,dt为时间的变化量。

[0050]

当负载电容cload的电容值保持不变时,负载端的电压随时间的变化量(即dv/dt)的绝对值越大,因此,负载端电压稳定时间越短,这段时间给负载电容cload充电电流i应当越大,所以这就要求电压输出缓冲电路110在输入电压切换时,提供很大瞬时充放电流。这需要电压输出缓冲电路110要有足够高的转换速率,才能使负载端电压很快的稳定。不仅如此,图1中电路模块pixel array和adc columns中参考电压接收端通常是较大的等效容性负载,同时目前时序设计的工作频率越来越大,时序逻辑之前的时间非常短,一般都是微秒级。这样一来,负载端电压要达到快速稳定,电压输出缓冲电路110所需的转换速率就更快。这对于采用图3中的两种类型差分放大器的电压输出缓冲电路110而言,是达不到应用需求的。

[0051]

图4为大负载电容下常规电压输出缓冲电路和高转换速率电压输出缓冲电路的输入输出电压的波形示意图。如图4所示,图中粗实线为电压输出缓冲电路110的输入端vin的电压,图中虚线为高转换速率电压输出缓冲电路的输出曲线(图中的vout by high slewing rate buf),细实线为常规电压输出缓冲电路的输出曲线(图中的vout by normal buf)。由图4可见,输入端vin的电压变化快慢由电路模块digital control控制,而电压输出缓冲电路110将输入端vin的电压传输时,需要在每个电位脉宽时间内,稳定跟随和输入电压vin相同电压幅值才能满足使用需求,常规电压输出缓冲电路无法在短时间内稳定跟随输入端vin的电压的变化。

[0052]

在静态参考电压的电压输出缓冲电路110中,可以根据设定的电压值来选择采用哪一种差分放大器类型。当输入端vin的电压从一个较低的电压幅值跳变到较高的电压幅值时,如果电压输出缓冲电路110输入输出范围不够,也是不能达到使用需求的。

[0053]

综合上述可知,为了不让cmos图像传感器系统的设计受到限制,电压输出缓冲电路110的输入输出范围要足够大,这样才能满足相关的电路模块应用需求。

[0054]

基于此,本发明提供了一种电压缓冲电路。

[0055]

图5为本实施例中的电压输出缓冲电路的原理图。如图5所示,所述电压缓冲电路包括:输入模块111和输出模块112,所述输入模块111包括第一差分放大器和第二差分放大器,所述第一差分放大器的反向输入端接于所述第二差分放大器的反向输入端,作为所述电压缓冲电路的输入端vin,用于接收输入电压,所述第一差分放大器的输出端和所述第二差分放大器的输出端分别输出第一电位信号和第二电位信号。所述输出模块112包括驱动输出单元112b,所述驱动输出单元具有第一驱动mos管和第二驱动mos管,所述第一驱动mos管的源极接于电源vdd,栅极接于所述第二差分放大器的输出端,漏极接于所述第一差分放大器的正向输入端、所述第二差分放大器的正向输入端和所述第二驱动mos管的漏极,作为所述电压缓冲电路的输出端vout,所述第二驱动mos管的栅极接于所述第一差分放大器的输出端,源极接于地端vss。所述输出模块112根据所述第一电位信号和所述第二电位信号,调节所述第一驱动mos管和所述第二驱动mos管的驱动电流,以使所述电压缓冲电路的输出端vout的电压跟随所述输入端vin的电压。

[0056]

如图5所示的电压输出缓冲电路,输出模块112为推挽式输出,第一差分放大器和第二差分放大器的输出端分别作为第一驱动mos管和第二驱动mos管的栅极驱动,从电路极性上很容易看出第一差分放大器和第二差分放大器的正向输入端与电压输出缓冲电路110的输出端vout是成反向的,第一差分放大器和第二差分放大器的正向输入端接于电压输出缓冲电路110的输出端vout。可以扩大电压输出缓冲电路110的输入输出范围,也增强输出模块112的驱动能力。

[0057]

进一步的,所述第一驱动mos管为pmos管,所述第二驱动mos管为nmos管。

[0058]

进一步的,所述输出模块112还包括快速响应输出单元112a,所述快速响应输出单元112a用于接收所述第一电位信号和所述第二电位信号,并根据所述第一电位信号和所述第二电位信号的电压的变化产生充电电流、第三电位信号和.第四电位信号,所述第一驱动mos管和所述第二驱动mos管接收所述第三电位信号和所述第四电位信号,并根据所述第三电位信号和所述第四电位信号的电压的变化调节所述驱动电流。

[0059]

进一步的,所述第一差分放大器为nmos输入对管的结构,作为输入模块111的中段到最高输入电压的输入级,所述第二差分放大器为pmos输入对管的结构,作为输入模块111的中段到最低输入电压的输入级。如此,扩大了电压输出缓冲电路110的输入电压的范围。

[0060]

图6为本实施例中的电压输出缓冲电路的第一电路图。如图6所示,所述电压缓冲电路中具有第一nmos管n401至第十一nmos管n411、第一pmos管p401至第十一pmos管p411、第一线性电容c41及第二线性电容c42;其中,所述第一驱动mos管为所述第十pmos管p410,所述第二驱动mos管为所述第十nmos管n410;所述输入模块111为所述第一pmos管p401至所述第五pmos管p405及所述第一nmos管n401至所述第五nmos管n405;所述快速响应输出单元112a为所述第六pmos管p406至所述第七pmos管p407及所述第六nmos管n406至所述第七nmos管n407;所述驱动输出单元112b为所述第八pmos管p408、所述第九pmos管p409、所述第十一pmos管p411、所述第八nmos管n408、所述第九nmos管n409及所述第十一nmos管n411;所述第一nmos管n401至第十一nmos管n411的衬底均接于所述地端vss,所述第一pmos管p401至第十一pmos管p411的衬底均接于所述电源vdd;其中,所述第一nmos管n401的栅极接于所述输入端vin,所述第一nmos管n401的源极和所述第二nmos管n402的源极接于所述第三nmos管n403的漏极;所述第三nmos管n403的栅极接于第一偏置电压vbias1,源极接于所述

地端vss;所述第一pmos管p401的栅极和所述第二pmos管p402的栅极接于所述第二pmos管p402的漏极,源极均接于所述电源vdd;所述第一pmos管p401的漏极接于所述第一nmos管n401的漏极,所述第二pmos管p402的漏极接于所述第二nmos管n402的漏极;所述第四pmos管p404的栅极接于所述输入端vin,所述第四pmos管p404的源极和所述第五pmos管p405的源极接于所述第三pmos管p403的漏极;所述第三pmos管p403的栅极接于第二偏置电压vbias2,源极接于所述电源vdd;所述第四nmos管n404的栅极和所述第五nmos管n405的栅极接于所述第五nmos管n405的漏极;所述第四nmos管n404的漏极接于所述第四pmos管p404的漏极,所述第五nmos管n405的漏极接于所述第五pmos管p405的漏极,源极接于所述地端vss;所述第六pmos管p406的栅极接于第三偏置电压vbias3,源极接于电源vdd;所述第七pmos管p407的栅极接于所述第一nmos管n401的漏极和所述第一线性电容c41的一端,漏极接于所述第一线性电容c41的另一端和所述第六nmos管n406的漏极;所述第七nmos管n407的栅极接于第四偏置电压vbias4,源极接于所述地端vss;所述第六nmos管n406的栅极接于所述第四nmos管n404的漏极和所述第二线性电容c42的一端,漏极接于所述第二线性电容c42的另一端;所述第八pmos管p408的栅极接于所述第七pmos管p407的栅极,源极接于所述电源vdd;所述第十一nmos管n411的源极接于所述地端vss,漏极接于所述第九pmos管p409的栅极和漏极,栅极接于所述第八pmos管p408的漏极;所述第十pmos管p410的栅极接于所述第九pmos管p409的栅极,源极接于所述电源vdd;所述第十一pmos管p411的源极接于所述电源vdd,栅极接于所述第八nmos管n408的漏极和所述第八pmos管p408的漏极;所述第八nmos管n408的栅极接于所述第六nmos管n406的栅极,源极接于所述地端vss;所述第九nmos管n409与所述第十nmos管n410的栅极接于所述第九nmos管n409的漏极和所述第十一pmos管p411的漏极,源极接于所述地端vss;所述第十nmos管n410的漏极、所述第十pmos管p410的漏极、所述第二nmos管n402的栅极、所述第五pmos管p405的栅极、所述第七pmos管p407的漏极和所述第六nmos管n406的漏极相接后作为所述输出端vout。

[0061]

第一电位信号经节点vout_h1输送至第七pmos管p407,所述第二电位信号经节点vout_l1输送至第七nmos管n407。快速响应输出单元112a产生的第三电位信号经节点vout_h2输送至第十pmos管p410,第四电位信号经节点vout_l2输送至第十nmos管n410。快速响应输出单元112a的原理如下,输入端vin的电压由低电压跳变到高电压时,电压输出缓冲电路110中的节点vout_h1和节点vout_l1的电压均降低,电压输出缓冲电路110中的第六pmos管p406和第七nmos管n407作为电流源mos管接入,其栅极接固定偏置电压(第三偏置电压vbias3和第四偏置电压vbias4),但是它们实际上能流过的电流受到第七pmos管p407和第六pmos管p406限制。当第七pmos管p407栅极电压降低,它的过驱动电压增加,从器件特性可知此时从源极到漏极允许流过更大电流,同时第六pmos管p406栅极电压也降低,它能够通过的电流减小。此时通过第六pmos管p406和第七pmos管p407电流大于第六pmos管p406和第七nmos管n407电流,这部分多出来的电流就是快速响应输出单元112a产生的充电电流,所述充电电流会立即流向负载电容cload,使得输出端vout的电压抬升。

[0062]

进一步的,将第六pmos管p406和第七nmos管n407电流设置大一些,这样充电流更大,同时第七pmos管p407和第六pmos管p406尺寸不宜过大,这样节点vout_h1和节点vout_l1的电压跟随输入端vin的电压的响应才足够快。如此,快速响应输出单元112a的电压调节变化是非常迅速的,第六pmos管p406和第七nmos管n407是偏置恒定的电流源,在快速响应

输出单元112a的输出支路上,输出端vout的电压变化是该节点上下电流相对变化的直接反应。

[0063]

由于输出端vout的电压上升到一定值时,第六pmos管p406由于沟道调制效应或者进入线性区,充电流降低。这就是需要驱动输出单元112b的原因,驱动输出单元112b调节驱动电流的工作原理如下,节点vout_h1和节点vout_l1的电压变化方向通过第八pmos管p408和第八nmos管n408将会反应到驱动输出单元112b,这两个mos管尺寸也不宜过大。在电压输出缓冲电路110中,根据mos管类型可以看出节点vout_h1和节点vout_l1的电压降低也会带来节点vout_h2和节点vout_l2的电压降低,因此,通过适当调整第九pmos管p409、第九nmos管n409、第十一nmos管n411以及第十一pmos管p411的器件尺寸,可以使节点vout_h2和节点vout_l2的电压降低的幅度比节点vout_h1和节点vout_l1的电压降低的幅度更大,所以当输入端vin的电压升高时,节点vout_h2的电压降低使第十pmos管p410栅源电压增加,流过第十pmos管p410电流增大,同时节点vout_l2的电压降低又减小了第十nmos管n410栅源的电压,那么更多的驱动电流将流向负载电容cload。

[0064]

类似的工作原理,当输入端vin的电压迅速降低时,在负载电容cload上就会有通过第六nmos管n406和第十nmos管n410进行放电流过程,在此不做过多赘述。

[0065]

进一步的,在电压输出缓冲电路110中,所述第八pmos管p408和所述第八nmos管n408的栅极的面积大于所述第一nmos管n401至第七nmos管n407、所述第九nmos管n409至第十三nmos管n413、所述第一pmos管p401至第七pmos管p407和所述第九pmos管p409至第十三pmos管p413的栅极的面积。应知道,将第八pmos管p408和第八nmos管n408器件的栅极的面积设置大一些,可以避免多出一个高阻抗节点,这样整个电压输出缓冲电路110中高阻抗节点只有输出端vout、节点vout_h1和节点vout_l1。不同的输入电压会改变电压输出缓冲电路110的大信号工作节点,影响电压输出缓冲电路110的小信号特性。为了能够让电压输出缓冲电路110工作在全范围输入电压,第七pmos管p407和第六nmos管n406增加补偿电容,所述补偿电容为第一线性电容c41和第二线性电容c42。补偿电容可以将主极点和次极点距离拉远,输出端vout节点相关的极点电容量f

vout

为:

[0066][0067]rout

≈g

p406rp406rp407

||r

p410

||r

n410

;

[0068]

其中,r

out

为输出端vout节点的等效对地阻抗,c

load

为负载电容cload的电容值,g

p406

为第六pmos管的等效电导,r

p406

为第六pmos管的等效电阻,r

p407

为第七pmos管的等效电阻,r

p410

为第十pmos管的等效电阻,r

n410

为第十nmos管的等效电阻。

[0069]

由于负载电容cload的电容值一般较大,因此可以忽略其它mos管的寄生电容。通过合理设置输入模块111中的偏置电流和输入模块111中的mos管的器件尺寸就可以使主次极点距离足够远,相位裕度在稳定区间内。电路开环增益近似等于输入模块111的一个差分放大器增益和输出级增益的乘积,一般在80db左右,可以满足输出电压对输入电压的跟随精度,应知道,增益设置过大会带来稳定性的问题。

[0070]

电压输出缓冲电路110工作于稳态,输入不进行变化时,输出端vout静态电流有如下平衡关系:

[0071]ich1

+i

ch2

=i

dch1

+i

dch2

;

[0072]

其中,i

ch1

为经过第六pmos管p406的电流,i

ch2

为经过第十pmos管p410的电流,i

dch1

为经过第七nmos管n407的电流,i

dch2

为经过第十nmos管n410的电流。

[0073]

由于电压输出缓冲电路110中第六pmos管p406和第七nmos管n407能流过最大电流是固定,原因是第三偏置电压vbias3和第四偏置电压vbias4确定的,那么也就限制了输出端vout在快速响应时充放电流大小。同时,由于节点vout_h1和节点vout_l1电压摆幅限制,当输入端vin的输入电压在接于近地电压或者电源电压时,节点vout_h1和节点vout_l1不一定足够高到关闭第七pmos管p407或者低到关闭第六nmos管n406。这样,由于存在第六pmos管p406和第七nmos管n407的电流通路平衡,输出端vout节点的电压的跟随范围必定有上下限值。

[0074]

优选的,所述输出模块112和所述输入模块111之间还设置有反馈单元。

[0075]

优选的,所述快速响应输出单元112a还设置有上镜像电流支路及下镜像电流支路。

[0076]

图7为本实施例中的电压输出缓冲电路的第二电路图。如图7所示,所述电压缓冲电路110中具有第一nmos管n401至第十三nmos管n413、第一pmos管p401至第十三pmos管p413、第一线性电容c41及第二线性电容c42;其中,所述第一驱动mos管为所述第十pmos管p410,所述第二驱动mos管为所述第十nmos管n410;所述输入模块111为所述第一pmos管p401至所述第五pmos管p405及所述第一nmos管n401至所述第五nmos管n405;所述快速响应输出单元112a为所述第六pmos管p406至所述第七pmos管p407及所述第六nmos管n406至所述第七nmos管n407;所述驱动输出单元112b为所述第八pmos管p408、所述第九pmos管p409、所述第十一pmos管p411、所述第八nmos管n408、所述第九nmos管n409及所述第十一nmos管n411;所述上下镜像电流支路为所述第十三pmos管p413及所述第十三nmos管n413;所述反馈单元113为所述第十二pmos管p412及所述第十二nmos管n412;所述第一nmos管n401至第十三nmos管n413的衬底均接于所述地端vss,所述第一pmos管p401至第十三pmos管p413的衬底均接于所述电源vdd;其中,所述第一nmos管n401的栅极接于所述输入端vin,所述第一nmos管n401的源极和所述第二nmos管n402的源极接于所述第三nmos管n403的漏极;所述第三nmos管n403的栅极接于第一偏置电压vbias1,其源极接于所述地端vss;所述第一pmos管p401的栅极和所述第二pmos管p402的栅极接于所述第二pmos管p402的漏极,源极均接于所述电源vdd;所述第一pmos管p401的漏极接于所述第一nmos管n401的漏极,所述第二pmos管p402的漏极接于所述第二nmos管n402的漏极;所述输入端vin同时也接于所述第四pmos管p404的栅极,所述第四pmos管p404的源极和所述第五pmos管p405的源极接于所述第三pmos管p403的漏极;所述第三pmos管p403的栅极接于第二偏置电压vbias2,源极接于所述电源vdd;所述第四nmos管n404的栅极和所述第五nmos管n405的栅极接于所述第五nmos管n405的漏极;所述第四nmos管n404的漏极接于所述第四pmos管p404的漏极,所述第五nmos管n405的漏极接于所述第五pmos管p405的漏极,源极都接于所述地端vss;所述第六pmos管p406的栅极和所述第十三pmos管p413的栅极接于所述第六pmos管p406的漏极同时接于所述第七pmos管p407的源极;所述第七pmos管p407的栅极接于所述第一nmos管n401的漏极和所述第一线性电容c41的一端,漏极接于所述第一线性电容c41的另一端和所述第六nmos管n406的漏极;所述第七nmos管n407的栅极和所述第十三nmos管n413的栅极接于所述第七nmos管n407的漏极和所述第六nmos管n406的源极,源极均接于所述地端vss;所述第六nmos

管n406的栅极接于所述第四nmos管n404的漏极和所述第二线性电容c42的一端,漏极接于所述第二线性电容c42的另一端;所述第八pmos管p408的栅极接于所述第七pmos管p407的栅极,源极接于所述电源vdd,漏极接于所述第十三pmos管p413的漏极和所述第十一nmos管n411的栅极;所述第十一nmos管n411的源极接于所述地端vss,漏极接于所述第九pmos管p409的栅极和漏极;所述第十pmos管p410的栅极接于所述第九pmos管p409的栅极,源极接于所述电源vdd;所述第十一pmos管p411的源极接于所述电源vdd,栅极接于所述第八nmos管n408的漏极和所述第十三nmos管n413的漏极;所述第八nmos管n408的栅极接于所述第六nmos管n406的栅极,源极接地;所述第九nmos管n409的栅极与所述第十nmos管n410的栅极接于所述第九nmos管n409的漏极和所述第十一pmos管p411的漏极,源极接于所述地端vss;所述第十nmos管n410的漏极和所述第十pmos管p410的漏极接于作为所述输出端vout,同时接于所述第二nmos管n402的栅极和所述第五pmos管p405的栅极,所述第七pmos管p407的漏极和所述第六nmos管n406的漏极;所述第十二nmos管n412的栅极接于所述第十一nmos管n411的栅极,漏极接于所述第一nmos管n401的源极,源极接于所述地端vss;所述第十二pmos管p412的栅极接于所述第十一pmos管p411的栅极,漏极接于所述第四pmos管p404的源极,源极接于所述电源vdd。

[0077]

图7中的电压输出缓冲电路110是在图6中的电压输出缓冲电路110的基础上经过调整优化,本实施例提出的优选电路结构。图7中的电压输出缓冲电路110将原来作为电流源使用第六pmos管p406和第七nmos管n407更改为二极管连接方式,并且多出一个上下镜像电流支路第十三pmos管p413和第十三nmos管n413。同时增设反馈单元113第十二nmos管n412和第十二pmos管p412,栅极接节点vout_fb。

[0078]

进一步的,电压输出缓冲电路110工作于稳态,输入端vin的电压不进行变化时,输出端vout的静态电流有如下平衡关系为:

[0079]ich3

+i

ch4

=i

dch3

+i

dch4

;

[0080]

其中,i

ch3

为经过第八pmos管p408的电流,i

ch4

为经过第十pmos管p410的电流,i

dch3

为经过第八nmos管n408的电流,i

dch4

为经过第十nmos管n410的电流。

[0081]

当输入端vin电压从低变高时,节点vout_h1和节点vout_l1的电压降低,电流会经过第六pmos管p406迅速产生并通过第七pmos管p407流向输出端vout,给负载电容cload充电。当输入变化量越大,第七pmos管p407栅源电压增加使其导通电阻降低,第六pmos管p406的漏极电压被拉到更低,这样对于二极管连接的第六pmos管p406来说,栅源电压差值增加会产生更大的充电电流,流向输出端vout。这样,在快速响应时,面对变化量较大的输出电压,快速响应输出单元112a能够增加充电电流。

[0082]

优选的,所述第十pmos管p410和所述第十nmos管n410的器件尺寸大于所述第一nmos管n401至第九nmos管n409、所述第一nmos管n401至第十三nmos管n413、所述第一pmos管p401至第九pmos管p409和所述第十一pmos管p411至第十三pmos管p413的器件尺寸。可以理解的是,第十pmos管p410和第十nmos管n410的器件尺寸可以设置大一些,在同样的过驱动电压下产生更大的电流,此时的驱动电流比前文的快速响应输出级充电流(也就是充电电流)大很多,直至vout电压稳定到vin电压值。

[0083]

当输入端vin输入到接近地电压或者电源电压,由于二极管连接的第六pmos管p406和第七nmos管n407在有电流通过时具有最低电压稳压作用,第七pmos管p407和第六

nmos管n406栅源电压差值在此时会低于开启阈值,当输入端vin接近地电压甚至输入端vin电压为零时,第七pmos管p407就会彻底关闭,同理输入端vin接近电源电压时第六nmos管n406也会关闭。这样一来输出端vout的电压可以通过第六nmos管n406,第七nmos管n407拉到地电压或者通过第七pmos管p407,第六pmos管p406拉到电源电压。如此电压输出缓冲电路110便在全范围区间内实现了输出电压的跟随特性,一般的,第六pmos管p406和第七nmos管n407所在支路在静态工作时,只会流过很小的电流,只会在电压跳变时,上下镜像电流支路中会产生充电与放电流的动作。

[0084]

由于增加了反馈单元113,反馈单元113中的反馈mos管为第十二nmos管n412和第十二pmos管p412。当输入端vin的电压由低跳高时,节点vout_fb的电压升高,而输入端vin的电压由高跳低时,节点vout_fb降低。从图中可以容易观察到,当节点vout_fb电压升高时,第十二nmos管n412电流增加,就使节点vout_h1电压进一步降低,第七pmos管p407和第十pmos管p410过驱动电压增加,增大了对输出端vout充电电流(驱动电流)。同理,当节点vout_fb电压降低时会使节点vout_l1进一步升高,最终使第六nmos管n406和第十nmos管n410过驱动电压增加,增大了对输出端vout放电电流(驱动电流)。

[0085]

在本发明中,电压输出缓冲电路110的输入模块111通过采用两个互补输入对管的差分放大器作为输入级,实现满幅的输入范围。电压输出缓冲电路110的输出模块112然后通过快速响应输出单元112a和驱动输出单元112b两条输出级支路,快速响应输出单元112a快速响应,驱动输出单元112b提供大驱动电流,快速响应输出单元112a和驱动输出单元112b配合工作可以进行全范围的输出。对电压输出缓冲电路110的整体效果而言,达到高的转换速率以及全范围输入输出的转换范围,经过简单的偏置和调整,可以应用于有时序控制需求,需要驱动较大容性负载的电路中。

[0086]

申请人选取了专利文献《us6392485b1-high slew rate differential amplifier circuit》中的电路为第一现有的电压输出缓冲电路。此外,申请人选取了专利文献《us7449952b2-amplifying circuit having a pull up circuit and a pull down》中的电路为第二现有的电压输出缓冲电路。此外,申请人选取了文献《anew compact low-power high-speed rail-to-rail class-b buffer for lcd applications》中的电路为第三现有的电压输出缓冲电路。为了验证本发明中电压输出缓冲电路110改进后的提升效果,申请人将本发明中电压输出缓冲电路110、第一现有的电压输出缓冲电路、第二现有的电压输出缓冲电路和第三现有的电压输出缓冲电路进行仿真和对比以进行效果验证。其中,图8为本实施例中的第一现有的电压输出缓冲电路的电路图。图9为本实施例中的第二现有的电压输出缓冲电路的电路图。图10为本实施例中的第三现有的电压输出缓冲电路的电路图。

[0087]

图11为本实施例中的第一仿真对比图。如图11所示,仿真电路中的容性负载的容值为10pf,在静态功耗相近的条件下。输入电压从1v到2v相互切换时,输出本发明中电压输出缓冲电路110、第一现有的电压输出缓冲电路、第二现有的电压输出缓冲电路和第三现有的电压输出缓冲电路的仿真结果。其中,curve_1为本发明中电压输出缓冲电路110的输出曲线,curve_2为第一现有的电压输出缓冲电路的输出曲线,curve_3为第三现有的电压输出缓冲电路的输出曲线,curve_4为第二现有的电压输出缓冲电路的输出曲线。

[0088]

继续参照图11,本发明中电压输出缓冲电路110的输出曲线curve_1的稳定时间约

为80ns,在输入端vin的电压抬升和下降时,由图11可以看出,输出曲线curve_1的转换速率比输出曲线curve_2、curve_3和curve_4的转换速率更快。这说明了本发明的电压输出缓冲电路110具有更快的响应速度。

[0089]

图12为本实施例中的第二仿真对比图。如图12所示,仿真电路中的输入端vin的电压模拟从地电位到电源电压,也即由低电位到高电位转变,在仿真电路中以0v~3.3v作为输入端vin的电压,以模拟仿真电路中的输入端vin的电压由低电位到高电位的转变。通过观察图12中的各个电压输出缓冲电路的输出电压是否精准的跟随输入端vin的电压,就可以判断出本发明中电压输出缓冲电路110、第一现有的电压输出缓冲电路、第二现有的电压输出缓冲电路和第三现有的电压输出缓冲电路的电压跟随精度。

[0090]

继续参照图12,图12中上下两个仿真曲线观察点不同,上方的曲线是集合了所有电压输出缓冲电路的输出与输入曲线波形,下方的曲线是分别用每一个电压输出缓冲电路的输出电压和输入电压做减法后得到的结果,该结果越接近0v越好,偏离0v越多,则说明电压跟随精度越差。图12中的标注同图11一样,curve_1为本发明中电压输出缓冲电路110的输出曲线,curve_2为第一现有的电压输出缓冲电路的输出曲线,curve_3为第三现有的电压输出缓冲电路的输出曲线,curve_4为第二现有的电压输出缓冲电路的输出曲线。通过图12可以看出本发明中的电压输出缓冲电路110的输出曲线curve_1拥有全范围较好的电压跟随精度。

[0091]

综上所述,本发明实施例中提供了一种电压缓冲电路,包括:输入模块和输出模块,所述输入模块包括第一差分放大器和第二差分放大器,所述第一差分放大器的反向输入端接于所述第二差分放大器的反向输入端,作为所述电压缓冲电路的输入端vin,用于接收输入电压,所述第一差分放大器的输出端和所述第二差分放大器的输出端分别输出第一电位信号和第二电位信号。所述输出模块包括驱动输出单元,所述驱动输出单元具有第一驱动mos管和第二驱动mos管,所述第一驱动mos管的源极接于电源vdd,栅极接于所述第二差分放大器的输出端,漏极接于所述第一差分放大器的正向输入端、所述第二差分放大器的正向输入端和所述第二驱动mos管的漏极,作为所述电压缓冲电路的输出端vout,所述第二驱动mos管的栅极接于所述第一差分放大器的输出端,源极接于地端vss。所述输出模块根据所述第一电位信号和所述第二电位信号,调节所述第一驱动mos管和所述第二驱动mos管的驱动电流,以使所述电压缓冲电路的输出端vout的电压跟随所述输入电压vin。在本发明中,所述第一差分放大器用于接收较高范围输入电压,所述第二差分放大器用于接收较低范围输入电压,使得电压缓冲电路能够接收全范围的输入电压。此外,所述输出模块还包括快速响应输出单元,所述快速响应输出单元用于接收所述第一电位信号和所述第二电位信号,并根据所述第一电位信号和所述第二电位信号的电压的变化产生充电电流、第三电位信号和第四电位信号,所述第一驱动mos管和所述第二驱动mos管接收所述第三电位信号和所述第四电位信号,并根据所述第三电位信号和所述第四电位信号的电压的变化调节所述驱动电流。让输出模块能够提供较大的瞬时电流来让负载进行充电和放电,快速调节输出电压以跟随输入电压,使得所述电压缓冲电路具有转换速率高的优点。

[0092]

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍

属于本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1