一种基于VPX的CAN和1553b双冗余架构设计方法

一种基于vpx的can和1553b双冗余架构设计方法

技术领域

1.本发明涉及一种基于vpx的can和1553b双冗余架构设计方法,属于通信领域,尤其涉及一种基于vpx的can和1553b的双冗余硬件结构、软件判别以及链路切换的方法。

背景技术:

2.控制器域网can(controller area network)是一种国际标准化的串行通信协议,是国际上应用最广泛的总线之一,在汽车计算机控制系统和嵌入式工业控制局域网中已经得到了广泛应用。1553b总线是mil

‑

std

‑

1553b总线的简称,作为美国军方专为飞机上设备制定的一种信息传输总线标准,现在被广泛应用在当代的各种民航客机以及军用飞机上,在航天系统也有着广泛的应用。15333b总线具有双通道设计,1553b总线可以在两个通道bus_a和bus_b之间切换。

3.can和1553b总线都有着一定的检错和纠错的能力,但是can和1553b总线的检错和纠错主要是针对传输线路中的突发错误。然而,由于车辆和飞机等的电磁环境比较复杂,并且在很多场合对链路的可靠性传输能力要求较高,为了防止由于器件损坏等原因导致通讯中断,本设计提出了基于vpx的can和1553b双冗余架构。

技术实现要素:

4.本发明目的在于,提供一种基于vpx的can和1553b双冗余架构,以解决can和1553b通信中由于电磁环境和器件损耗等导致的通信中断问题,提高通信的可靠性。

5.本发明提出的一种基于vpx的can和1553b双冗余架构,包括:

6.两颗mcu芯片,其中一颗作为主处理器,另一颗作为备用处理器。两颗mcu芯片通过通用输入输出gpio(general

‑

purpose input/output)互连,采用串行外设接口spi(serial peripheral interface)通信协议。

7.两颗mcu芯片通过srio(serial rapid i/o)总线与vpx接插件连接,可以通过srio协议与上位机通信,上报故障信息等。

8.can总线收发芯片,完成can总线的差分数据发送与差分数据接收功能,can总线收发芯片与隔离芯片连接。

9.隔离芯片,完成两颗mcu芯片与两个can总线收发芯片的电气隔离与电平转换,隔离芯片一端与mcu芯片相连,一端与can总线收发芯片相连。

10.1553b协议处理芯片,完成1553b总线数据收发功能。1553b协议处理芯片与mcu芯片直接相连。

11.1553b隔离变压器,完成1553b链路的电气隔离与阻抗匹配。1553b隔离变压器与1553b协议处理芯片直接相连。

12.可选地,mcu芯片选用xc7z045ffg676,作为主控芯片,并且该芯片内部集成了can总线控制器功能。

13.可选地,can总线收发芯片选用tja1050芯片。

14.可选地,隔离芯片选用adum1201crz芯片。

15.可选地,1553b协议处理芯片选用hi6110芯片。

16.可选地,1553b隔离变压器选用pm

‑

db2791芯片。

17.基于vpx的can和1553b双冗余的架构在进行正常工作时,首先启动自检程序,自检的工作流程为步骤一到步骤四所示。

18.步骤一:系统上电后,一颗mcu芯片作为主处理器,另一颗mcu芯片作为协处理器,首先开始进行双冗余的链路自检;

19.步骤二:主处理器通过can总线向协处理器发送自检报文,并且通过gpio向协处理器发送can总线自检的通知。协处理器收到自检通知后,检查是否收到can总线的自检报文。当1秒内没有收到can总线的自检报文,协处理器通过gpio向主处理反馈接收数据超时。当协处理器收到can总线的自检报文后,进行报文比对,当接收到的can总线数据比对完全一致,协处理器通过gpio通知主处理器can总线接收数据正确,否则通知主处理器can总线接收数据错误。

20.步骤三:主处理器设置1553b协议处理芯片的工作模式为总线控制器bc(bus control)模式,协处理器设置1553b协议处理芯片的工作模式为远程终端rt(remote terminal)模式。主处理器通过1553b总线的bus_a通道向协处理器发送自检报文,并且通过gpio向协处理器发送1553b自检的通知。协处理器收到自检通知后,检查是否收到来自bus_a通道的自检报文。当1秒内没有收到自检报文,协处理器通过gpio向主处理反馈bus_a通道接收数据超时。当协处理器收到bus_a通道的自检报文后,进行数据比对,当接收到的自检报文数据比对完全一致,协处理器通过gpio向主处理器发送接收bus_a通道数据正确,否则发送接收bus_a通道数据错误。

21.步骤四:当1553b总线的bus_a通道自检完成后,启动1553b总线的bus_b通道自检。1553b总线的bus_b通道自检同步骤三相同。

22.步骤五:主处理器通过srio向上位机报告can总线和1553b总线自检的结果。

23.当can总线和1553b总线自检通过后,系统开始进行正常工作流程,具体步骤如步骤六到步骤八所示。

24.步骤六:主处理器切换到正常的can总线和1553b总线数据收发状态,主处理器将1553b协议处理芯片切换到正常的bc/rt/bm(总线监控器,bus monitor)模式。协处理器切换到静默状态,不进行任何操作。

25.步骤七:主处理器在进行can总线数据收发时,监听can总线控制器内部的错误计数器信息,当错误计数器的错误统计结果超过阈值之后,主处理器停止can总线数据收发,并且通过gpio通知协处理器,启动协处理器的can总线通信功能。

26.步骤八:主处理器在进行1553b总线数据收发时,监听1553b协议处理芯片反馈的错误信息,当接收到1553b总线数据错误之后,主处理器首先将1553b的通信链路从bus_a改为bus_b。如果切换为bus_b后错误依然存在,主处理器停止1553b总线数据收发,并且通过gpio通知协处理器,启动协处理器的1553b总线通信功能。

27.本发明的优点及有益效果在于:该发明可以实现can总线和1553b总线的链路自检与状态上报功能,并且在总线链路通信的过程中可以实时监测链路信息,当链路存在故障时及时切换冗余链路保证通信不会中断,从而提升了整个通信链路的稳定性和可靠性。

附图说明

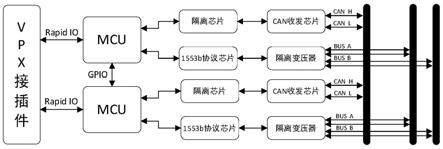

28.图1为本发明所提出的双冗余架构设计图。

29.图2为本发明所提出的mcu电路原理图。

30.图3为本发明所提出的1553b电路原理图。

31.图4为本发明所提出的can电路原理图。

32.图5为本发明所提出的vpx接口电路原理图。

33.图6为本发明所提出的双冗余上电自检流程图。

34.图7为本发明所提出的双冗余监测及切换流程图。

具体实施方式

35.下面将结合附图和实施例对本发明作进一步的详细说明。

36.本发明设计了一种完全双冗余的can和1553b总线通信架构,并且提出了基于此双冗余架构的链路自检与链路切换的方法,从而提高了can和1553b的链路稳定性和鲁棒性。

37.本设计所提出的系统整体架构如图1所示。本发明以图2

‑

图5所示意的一种双冗余架构实现方案为例,对本发明的链路自检与链路切换实施方案进行详细的介绍。

38.步骤一:本设计中两颗xc7z045ffg676芯片作为系统的主处理器及协处理器,如图2所示。设u1为主处理器,u2为协处理器。

39.步骤二:由于xc7z045ffg676芯片内部集成了can总线控制器的功能,因此主处理器可以直接调用xcanps_send指令向协处理器发送一串报文“0x11 0x22 0x33 0x44 0x55 0x66 0x77 0x88 0x99 0xaa0xbb0xcc0xdd0xee 0xff”,并且通过spi接口发送一串报文“0x55 0xaa 0x00 0xff”通知协处理器启动can链路自检。当协处理器接收到来自主处理器的can自检通知之后,通过xcanps_recv指令接收can总线报文,若协处理器在1秒内没有接收到can总线的信息,通过spi总线向主处理器上报“0x55 0xaa 0x01 0xff”表示接收数据超时,表明此时can总线自检存在问题。若协处理器接收到can总线数据,但是数据存在异常,协处理器向主处理器上报“0x55 0xaa 0x02 0xff”。若can总线接收数据正确,上报“0x55 0xaa 0x03 0xff”,表明can总线链路自检通过。

40.步骤三:主处理器和协处理器分别设置图3中的u3和u4芯片内部的控制寄存器control register,令u3与u4分别工作在bc和rt模式,并且设置1553b总线使用bus_a通道收发数据。主处理器通过控制u3芯片内部的发送数据队列transmit data fifo,向协处理器发送一串报文“0xff 0xee 0xdd 0xcc 0xbb 0xaa 0x99 0x88 0x77 0x66 0x55 0x44 0x33 0x22 0x11”,并且通过spi接口发送一串报文“0x55 0xaa 0x04 0xff”通知协处理器启动1553b总线的bus_a自检。当协处理器收到来自主处理器的1553b总线bus_a自检通知后,通过hi6110芯片的接收数据队列received data fifo读取接收到的bus_a通道数据。若协处理器在1秒内没有接收到bus_a通道的数据,通过spi总线向主处理器上报“0x55 0xaa 0x05 0xff”表示接收数据超时,表明此时1554b的bus_a总线存在问题。当协处理器接收到bus_a的数据,但是数据存在异常,协处理器向主处理器上报“0x55 0xaa 0x06 0xff”。bus_a总线接收数据正常,上报“0x55 0xaa 0x07 0xff”,表示bus_a总线链路自检通过。

41.步骤四:当主处理器接收到从处理器的bus_a自检信息后,启动bus_b总线自检。主处理器设置图3中的u3和u4芯片的控制寄存器control register,选用1553b总线的bus_b

链路工作。主处理器通过控制u3芯片内部的发送数据队列transmit data fifo,向协处理器发送一串报文“0xff 0xee 0xdd 0xcc 0xbb 0xaa 0x99 0x88 0x77 0x66 0x55 0x44 0x33 0x22 0x11”,并且通过spi接口发送一串报文“0x55 0xaa 0x08 0xff”启动1553b总线的bus_b自检。当协处理器收到来自主处理器的1553b总线bus_b自检通知后,通过hi6110芯片的接收数据队列received data fifo读取1553b总线数据。若协处理器1秒内没有接收到bus_b通道的数据,通过spi总线向主处理器上报“0x55 0xaa 0x09 0xff”表示接收数据超时,表明此时1554b的bus_b总线存在问题。当协处理器接收到bus_b的数据,但是数据存在异常,协处理器向主处理器上报“0x55 0xaa 0x0a 0xff”。bus_b总线接收数据正常,上报“0x550xaa 0x0b 0xff”,表示bus_b总线链路自检通过。

42.步骤五:主处理器u1通过srio总线向上位机报告自检结果。自检结果的报文形式为“0x7e 0x7e 0x7e 0x04 0x01(0x00) 0x01(0x00) 0x01(0x00) 0x7e 0x7e”。其中第5

‑

7字节分别为can、bus_a、bus_b的自检结果,01表示自检成功,00表示自检失败。

43.当can总线和1553b总线自检通过后,系统开始进行正常工作流程,具体步骤如步骤六到步骤八所示。

44.步骤六:主处理器u1切换为正常的can和1553b总线的收发状态,通过控制control register将1553b协议芯片切换为工作所需的bc/rt/bm工作模式。协处理器u4不进行任何操作,处于静默状态。

45.步骤七:主处理器u1在进行正常的can总线数据收发时,要通过can总线控制器的xcanps_getbuserrorcounter指令监听can总线的错误统计信息。当can总线的错误计数超过100时,主处理器停止can总线的数据收发,并且通过gpio总线向协处理器u2发送报文“0x55 0xaa 0x0c 0xff”,启动协处理器u2的can总线通信功能。

46.步骤八:主处理器u1在进行1553b总线数据收发时,要监听1553b总线协议处理芯片的错误寄存器error register的故障检测信息,当error register的结果不是全0时,表明总线通信存在问题,首先u1通过控制control register将1553b总线链路从bus_a切换为bus_b,若故障解除,则通过1553b的bus_b通道进行正常数据通信。若是故障没有解除,则主处理器u1停止1553b总线工作,通过gpio发送报文“0x55 0xaa 0x0d 0xff”,启动协处理器u2的1553b总线收发功能。

47.综上所述,本发明提出的一种基于vpx的can和1553b双冗余架构设计方法,可以实现can总线和1553b总线的链路自检与状态上报功能,并且在总线链路通信的过程中可以实时监测链路信息,当链路存在故障时及时切换冗余链路保证通信不会中断,从而提升了整个通信链路的稳定性和可靠性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1