一种基于SoCFPGA芯片的高速数据采集及处理系统的制作方法

一种基于soc fpga芯片的高速数据采集及处理系统

技术领域

1.本实用新型属于数据采集分析领域,特别涉及一种基于soc fpga芯片的高速数据采集及处理系统。

背景技术:

2.目前高速数据采集与处理系统在机器人、人工智能、超声检测、武器装备光电采集等领域有着广泛的应用,然而由于高速数据采集与处理系统需要解决高速应用、高速缓存、大数据存储、高速数据处理及数据通信的问题,因此使用arm平台、dsp平台或fpga平台很难完成此项需求。在传统的芯片架构中,处理器、dsp、fpga往往都各自独立工作。

3.在嵌入式平台上,采用高速a/d转换器及ddr存储搭建高速数据采集与处理系统时对处理器有较高的要求:一是速度上要满足a/d转换器的采样速率,但是在100msps 的采样速度下,往往只有fpga或高端的dsp才能满足速度要求;二是对于ddr的控制比较复杂,对于大部分处理器而言将耗去很多的内部资源;三是对于海量的数据处理,需要处理器拥有强大的数据处理能力。

4.为解决高速采样、数据存储、高速处理、高速传输的问题,现有技术多采用 fpga+arm或fpga+dsp的方案设计。这样的设计方案可以结合fpga的高速采集、逻辑处理的优势和arm或dsp的高速数据处理的优势,完成高速数据采集与处理的功能。该方案采用板级集成的方式,即在一块电路板上设计复杂的电路,将电路通过pcb板走线连接在一起。此种方式设计的系统不仅设计成本高,而且受限于pcb走线和i/o 引脚性能的影响,无法实现高带宽的数据通信;而且在这种方案中,需要在arm/dsp 芯片和fpga芯片之间设计一个合理的高速数据传输通道,以便于fpga采集到的高速数据可以实时的与arm/dsp处理端进行实时交互。这种设计方案设计需要设计复杂的通信总线,将耗费大量的arm/dsp和fpga芯片的资源,很难达到小型化的要求。

技术实现要素:

5.本实用新型解决的技术问题是:为了解决高速数据采集、高速数据处理和小型化之间的矛盾,同时解决高速数据采集时出现的传输带宽瓶颈的问题,并在高速缓存、大数据存储、高速数据传输和处理方面进行改进,以保证高速数据采集和处理的时间缩短,数据不丢失,本实用新型设计一种基于soc fpga芯片的高速数据采集及处理系统。

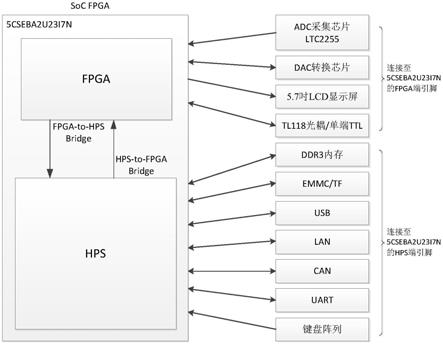

6.本实用新型的技术方案是:一种基于soc fpga芯片的高速数据采集及处理系统,其特征在于,包括soc fpga处理芯片、ddr3内存、nand flash存储器、高速adc采集芯片、dac转换芯片、lcd显示屏、矩阵键盘电路和光耦/单端ttl;

7.所述高速adc采集芯片连接soc fpga处理芯片的fpga的i/o管脚上,高速adc采集芯片模拟采集部分连接外部模拟信号,数字部分连接至fpga端的i/o上,完成对模拟信号的采集功能;

8.所述dac转换芯片连接soc fpga处理芯片的fpga的i/o管脚上,通过hps端模拟输

出电压,供外部模拟采样电路不同的模式下工作;

9.所述lcd显示屏连接soc fpga处理芯片的fpga的i/o管脚上,通过管脚映射方式,驱动显示,作为人机交设的显示界面;

10.所述ddr3内存连接soc fpga处理芯片的hps端的内存控制器接口,作为系统运行内存;

11.所述emmc/tf模块连接在soc fpga处理芯片的hps端的emmc控制接口,用于存储数据;

12.所述usb模块、lan模块、can模块和uart模块分别连接在soc fpga处理芯片的 hps端的usb控制接口、lan phy接口、can控制器接口和uart控制器接口,完成usb、lan、can和uart外设接口的数据通信功能;

13.所述键盘阵列连接在soc fpga处理芯片的hps端的通用i/o接口上,通过行列矩阵扫描方式完成采集和数据上报功能。

14.本实用新型进一步的技术方案是:所述soc fpga选用altera公司的cyclone v 系列5cseba2u23i7芯片。

15.本实用新型进一步的技术方案是:所述ddr3芯片选用紫光的scb15h512160af型号芯片。

16.本实用新型进一步的技术方案是:所述高速adc采集芯片选用cbm94ad67

‑

200型号芯片。

17.本实用新型进一步的技术方案是:所述dac转换芯片选用cbm53d24aqf型号芯片。

18.本实用新型进一步的技术方案是:所述按键矩阵由多个点触按键组成4

×

4矩阵排列,分为输入和输出2组信号连接至hps端。

19.本实用新型进一步的技术方案是:所述hps端到fpga端,使用h2f_lw_axi_master 内部总线将参数由arm端传递给fpga端;fpga端到hps端,使用f2h_axi_slave内部总线将数据又fpga端传递给arm端。

20.本实用新型进一步的技术方案是:所述hps端和fpga端共享一块存储单元,通过 dma方式进行数据交互。

21.发明效果

22.本实用新型的技术效果在于:本系统克服了传统多片处理器相互传递数据带宽的瓶颈。本系统中的soc fpga芯片芯片集成fpga逻辑和arm处理器,利用芯片本身的高性能、高集成、内部高速总线的优势,最终解决了高速模拟信号采集应用中数据传输带宽较低的问题,提高通信数据吞吐率,以及减小印制板布线面积、节省成本方面具有较好的应用场景。本发明需要解决高速数据采集、高速数据处理和小型化之间的矛盾需求,及实现了99%单元级国产化替代的要求。

23.具体来说,本实用新型和现有技术相比的创新之处为:现有技术多采用arm+fpga 来实现,fpga负责完成诸如i/o逻辑控制、adc高速采集后,通过外部总线进行数据传输至arm端,后arm端进行存储、数据处理、数据融合后,调用液晶屏显示驱动、网络驱动完成数据的显示和通信。本发明采用soc fpga后,逻辑上还是arm+fpga的处理思路,采用内部高速总线,大大加速了数据的双向传递,在此基础上,通过使用soc fpga 芯片的管脚映射功能,将液晶屏显示部分的管脚应设置fpga的i/o接口上,hps端(arm 端)处理数据完成后,仅需要

将数据通过高速总线传递至fpga侧,由fpga侧映射功能完成实时图像的显示和刷新;其次,网络通信数据通过hps侧的协议解析后,可直接通过内部高速总线传递至fpga侧,无需hps侧建立数据缓存和传输处理。

附图说明

24.图1为基于soc fpga高速采集处理系统电路框图

25.图2为soc fpga hps和fpga端高速总线框图

具体实施方式

26.在本实用新型的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

27.参见图1

‑

图2,在传统的芯片架构中,处理器、dsp、fpga往往都各自独立、互不相干。当一个系统需要用到处理器、dsp、fpga中的多个元件时,采用板级集成的方式,在一块电路板上设计复杂的电路,将它们通过pcb板走线连接在一起。以此种方式设计的系统不仅设计生产成本高,而且受限于pcb走线和i/o引脚性能的影响,无法实现高带宽的数据通信。

28.随着信息技术的高速发展,单芯soc芯片(system on chip)的出现,解决了上述需求。altera公司(被intel收购)推出soc fpga系列、xilinx公司推出zynq系列都是此类芯片。

29.集成处理器和fpga器件具有划时代的意义,arm和fpga的优势共存一体,即arm 的顺序控制、丰富外设、开源驱动,与fpga的并行运算、高速接口、灵活定制相得益彰,再加上其内部多条高速桥接总线,使其数据交互链路畅通无阻。

30.目前,各行各业正趋向于通过资源整合和并购方式来获得更强、更稳固的竞争力,芯片架构亦是如此。为解决高速数据采集、处理、传输的需求,各大传统的fpga厂家都推出了带有嵌入式硬核处理器的soc fpga。如intel fpga部门基于不同应用推出的带有cortex

‑

a9、cortex

‑

a53、至强cpu等一系列soc fpga器件,以及xilinx推出的带有cortex

‑

a9、cortexa53处理器zynq系列fpga。无论intel公司的soc fpga 器件,还是xilinx公司的zynq器件,其基本架构都是在同一个硅片上集成fpga和 arm/cpu处理器,并通过高速、高带宽的互联架构连接起来。soc fpga器件具有划时代的意义。这样arm和fpga的优势共存一体,即arm的顺序控制、丰富外设、开源驱动,与fpga的并行运算、高速接口、灵活定制相得益彰。在加上其内部具有多条高速桥接总线,使其数据交互链路畅通无阻。

31.现有与本发明相近的设计方案多采用xilinx公司的zynq系列fpga完成。对比socfpga和zynq fpga可以发现,xilinx公司的zynq系列芯片,仅支持arm先启动,然后fpga启动的方式;而intel公司的soc fpga,arm和fpga均可独立启动,互不干涉,甚至可以一方不上电,另一方也能正常工作。soc fpga芯片针对zynq芯片的这种优势,给单独调试带来很大的好处,支持单独调试arm端功能和fpga端功能,在单独调试完成后,将两端功能整合起来调试,降低设计和调试难度。

32.针对本发明的需求,可选用的方案为xilinx的zynq系列和intel的soc fpga系列。 zynq使用的是vivado集成编译环境,soc fpga使用的是quartus编译环境。相比较而言,在编译速度、仿真速度、软件集成度等方面,soc fpga具有一定的优势。再者, soc fpga由于采用intel成熟的cpu设计和加工技术,具有功耗控制、发热量控制的优势。其次,xilinx作为传统fpga的设计生产厂商,zynq系列偏重于fpga逻辑门的实现,对arm顺序执行架构的集成和生态环境的建设均存在不足,而intel从建立之初至今,发展方向一直放在传统x86架构(复杂指令集架构)cpu上(arm数据精简指令集架构),收购altera公司后,将其处理器架构的优势与altera的fpga相结合,在性能、功耗、软件生态等方面具备一定的优势。本发明需要实现高速采集、处理、显示和数据传输的功能,在arm端设计的比重较大,综合考虑,采用intel公司的socfpga芯片。

33.本实用新型解决的技术方案是:一种基于soc fpga芯片的高速采集设备,主要由 soc fpga处理芯片、ddr3内存、nand flash存储器、高速adc采集芯片、dac转换芯片、5.7吋lcd显示屏、矩阵键盘电路和若干外设转换芯片等部分组成。图1中ddr3 内存、emmc/tf模块、usb模块、lan模块、can模块、uart模块、键盘阵列模块连接至soc fpga芯片的hps端,hps全称为hard processor system即硬件处理系统,此硬件处理系统基于cortex

‑

a9 arm处理器构建,ddr3内存作为arm处理器的存储交换单元,作为系统加载运行、数据搬移和处理的桥梁,完成通用arm处理器的计算和处理功能;usb模块、lan模块、can模块、uart模块挂载在hps(arm处理器)相关外设接口上,加载linux下的相应驱动程序,完成usb、lan、can、uart等外设接口的数据通信功能;键盘阵列挂载在hps(arm处理器)的通用gpio接口上,通过行列矩阵扫描方式完成采集和数据上报功能。

34.本实用新型进一步的技术方案是:5.7吋lcd显示屏连接至soc fpga的逻辑端引脚 (fpga端),映射至arm系统内存中,调用运行在arm端(hps端)的linux系统的显示器驱动程序完成显示功能。lcd显示屏部分作为人机交互的外设,完成菜单显示、参数设置、实时结果显示的功能。

35.ddr3内存挂载在hps端,构成系统的运行内存,用于linux操作系统的各项操作。

36.nand flash存储器连接至soc fpga的hps端,构成系统的存储空间,用于linux 操作系统的加载、数据文件的存储。

37.矩阵键盘采集电路连接至soc fpga的hps端,arm处理器通过查询扫描方式确定是否有按键被按下及按下按键的标识,通过内部低速总线h2f_lw_axi_master发送至 fpga端,fpga提取按键信息,通过spi总线设置dac的参数,并通过显示屏显示当前设置的参数值。

38.adc芯片挂载在fpga端,adc模拟采集部分连接外部模拟信号,数字部分连接至fpga 端的i/o上,完成对模拟信号的采集功能。

39.所述adc采集电路实用3片14位精度adc芯片完成采集任务,通过fpga的逻辑处理先将3路数据(42位数据)暂存至fpga内部fifo中,然后fpga逻辑通过压缩、提取、滤波等算法将数据转换为32位数据,再通过内部高速总线f2h_axi_slave发送至hps端,hps端在经过排序、抽点等算法完成一帧显示数据的构建,最终将显示数据发送至lcd屏,将结果显示在显示屏上。

40.所述soc fpga芯片作为整个链路的核心,完成adc数据采集、参数设置、显示屏控

制、数据处理显示、按键采集等功能,本实用新型发明以soc fpga芯片为核心处理芯片,配合多种芯片辅助处理,完成新型采集系统的设计。

41.本发明对常见的方案进行优化设计,解决了不同处理芯片高速传输带宽较低的问题。其方案如下:

42.soc fpga选用altera公司的cyclone v系列5cseba2u23i7芯片,该器件具有25000 个fpga逻辑单元(le);175kb嵌入式ram存储器;4个数字锁相环pll;双核基于 cortex

‑

a9硬核处理器系统(hps),运行主频为800mhz;包含ddr3控制器、千兆以太网mac控制器、nand flash控制器、sd/mmc控制器、spi主从机控制器、usb控制器、 uart控制器、i2c控制器、uart控制器等外设控制器。hps全称为hard processor system 即硬件处理系统,此硬件处理系统基于cortex

‑

a9 arm处理器构建,ddr3内存作为arm 处理器的存储交换单元,作为系统加载运行、数据搬移和处理的桥梁,完成通用arm 处理器的计算和处理功能。

43.ddr3芯片选用紫光的scb15h512160af,两片16

×

32mbit ddr3芯片,共512mb的内存模组,ddr3内存芯片由hps端的ddr3控制器直接控制,无需fpga端操作。

44.nand flash芯片选用兆易创新的gd5f4gm5ufxxg,组成4gb的flash存储空间,用于加载linux操作系统、存储应用程序、存储文件等,flash存储器由hps端的nandflash控制器直接控制,无需fpga端操作。

45.高速adc芯片选用芯佰微公司的cbm94ad67

‑

200芯片,该芯片具有200msps的采样率,可以3.3v/1.8v单电源供电,16位精度的高速模拟数字转换器。adc芯片模拟部分连接外部采集的模拟电压信号,转换成数字信号后,连接至fpga端的io上,由fpga 进行数据采集、缓存、处理、发送等操作。

46.dac芯片选用芯佰微公司的cbm53d24aqf芯片,该芯片具有低功耗、2.5v至5.5v 供电、2路模拟输出、12位精度、建立时间为10us、可以轨对轨直接输出等特点,通过hps端spi总线配置模拟输出电压,供外部模拟采样电路工作在不同的模式下。

47.lcd触摸显示屏选用沐泽的lpm101uan11型10.1吋lcd显示屏,此款屏基于colortft

‑

lcd cmos模组,具有分辨率为1920

×

1200、具有262k颜色深度、亮度为1000 流明、

±

80

°

的可视角度格式等特点,广泛用于小型化工业、军工设备中。lcd的ttl 输入信号连接至fpga的i/o管脚上,通过映射功能映射至arm系统内存中,调用运行在arm端(hps端)的linux系统的显示器驱动程序完成显示功能。lcd显示屏部分作为人机交互的外设,完成菜单显示、参数设置、实时结果显示的功能。

48.按键矩阵由多个点触按键组成4

×

4矩阵排列,分为输入和输出2组信号连接至hps 端,通过hps端应用程序中的矩阵扫描算法采集按键是否按下等状态。矩阵按键配合 lcd显示功能,完成人机交互、参数设置、菜单选项等功能。

49.外设芯片采用国产化芯片进行设计,主要由usb hub芯片fe2.1、千兆网交换芯片 sf6524、can总线驱动器jpca82c250、串行驱动器cbm3245eeai、cbm487eese等组成,完成usb、lan、can、rs232/rs422/rs485等外设的通信功能。

50.系统加电运行后,首先由hps端加载linux操作系统,加载完系统后将fpga的程序写入fpga的ram中,接着自动运行加载qt桌面程序,等待人机交互的输入。键盘阵列程序检测到有按键按下后,判断按键设置的功能、选项、参数等信息存储在flash 中,同时将参数通过内部总线h2f_lw_axi_master发送至fpga端,fpga根据参数设置,产生不同频率的发射

脉冲信号、重复频率信号等输出,同时根据滤波等级、抽点因子等参数设置内部寄存器。fpga产生发射脉冲及重复频率后,驱动模拟电路进行数据采集工作;fpga端先将采集的数据通过内部fifo进行缓冲处理,调用fpga的提取算法、滤波算法、压缩算法等逻辑,将3路共42位数据转换为32位数据,通过 f2h_axi_slave总线发送至hps端;hps端再进行二次数据处理,最终将处理后的数据通过lcd显示屏显示出来,如果在参数选择中选择网络传输使能,则同时将处理后的数据通过千兆以太网接口发送至指定计算机的千兆以太网接口,在指定计算机上通过相应的应用程序显示处理。

51.hps端到fpga端,使用h2f_lw_axi_master内部总线将参数由arm端传递给fpga 端。

52.fpga端到hps端,使用f2h_axi_slave内部总线将数据又fpga端传递给arm端。

53.hps端和fpga端共享一块存储单元,通过dma方式进行数据交互。

54.信号传递:

55.系统开机后,进入linux操作系统,系统自动加载qt可执行程序显示界面,按下菜单键调出系统菜单,设置dac输出参数、发射脉冲频率、发射脉冲宽度、重复频率、滤波等级、抽点因子等参数后,hps端将设置的参数保存为文件存储在flash中,设置qt 程序中c程序算法中的输入参数,同时将参数通过内部总线h2f_lw_axi_master发送至 fpga端,fpga根据参数设置,产生不同频率的发射脉冲信号、重复频率信号等输出,同时根据滤波等级、抽点因子等参数设置内部寄存器。fpga产生发射脉冲及重复频率后,外部模拟电路开始工作,此时打开adc芯片的使能信号,开始采集adc的数据,先将adc的数据缓存至fpga的内部fifo中,再调用fpga端的提取算法、滤波算法、压缩算法等逻辑,将3路共42位数据转换为32位数据,通过f2h_axi_slave总线发送至hps端, hps端的qt应用程序中再通过排序、抽点算法得到需要显示的最终数据,调用linux驱动层将显示结果发送至lcd显示屏上显示出来。lcd显示屏连接在fpga的io管脚上,通过fpga内部ram与hps端共享内存,hps端计算显示内容后,数据存放在ram中,由fpga 调用显示。

56.同时,显示数据可通过千兆以太网接口,使用udp协议,将数据送往指定的地址,在通用计算机上通过相应的应用程序显示出来。

57.本实用新型充分利用嵌入式linux操作系统内嵌大量驱动程序的优势,包括显示、 spi、uart、i2c、can等驱动程序,通过修改设备树、设备节点等信息完成上述功能的驱动部分,再通过编写dma、h2f_lw_axi_master、f2h_axi_slave等设备驱动,完成总线传输部分的驱动。

58.在linux操作系统下,采用qt编程工具+qwt控件,编写lcd显示屏的应用界面程序,采用多线程技术,结合查询方式和中断方式进行数据的采集和处理;采用时间驱动机制及现有的生产者

‑

消费者模型对缓冲区进行管理,保证整个链路数据的完整性和实时性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1