一种面积紧凑的自适应偏置NMOS型LDO电路

一种面积紧凑的自适应偏置nmos型ldo电路

技术领域

1.本实用新型涉及集成电路设计技术领域,具体涉及一种面积紧凑的自适应偏置nmos型ldo电路。

背景技术:

2.图1至3给出了实现全集成ldo线性稳压器的3种基本结构。人们习惯把低压降(ldo)线性稳压器简化称呼为ldo,本实用新型中亦延续这一习惯。其中:

3.参见图1所示,第一种结构为采用pmos管作功率传输管的电路结构,其容易通过密勒补偿得到一个极低的主极点以保证环路的稳定性,具有负载电流范围大、线性调整率和负载调整率好等优点;而且适合在较低电源电压下工作。为了把输出电压过冲控制在一定的范围之内,输出端的等效阻抗必须控制在一定的范围之内,由于pmos的载流子迁移率低,需要以更大的尺寸和更大的输出级电流(即r取值不能过大)保证输出端的低阻特性。这意味着,在同等的静态电流下其误差放大器的带宽往往小得多、功率传输管栅极负载大得多,因而难以满足全集成线性稳压器的快速响应要求。主要用在负载切换速率小于100ma/μs的场合。

4.参见图2所示,第二种结构为采用nmos管作功率传输管的电路结构,由于输出端固有的低阻特性和nmos管的高载流子迁移率特性,输出级不需要维持较大的最小偏置电流,而且作为功率传输管的nmos管的尺寸更小一些,因而容易实现快速响应特性,能够应对负载切换速率更高的场合。此外,其带宽随负载变化小,因而环路稳定性好;nmos功率传输管的漏极接电源,因此,电源抑制能力更好。由于功率传输管的栅极比输出电压高出一个vgs,要求误差放大器具有较高的工作电压,不过这在多数电子系统中都不是问题,因为i/o的标准供电电压是2.5/3.3v,带隙基准一般也采用3.3v电压供电,远高于soc内核所需的1~1.2v电压。由于功率传输级没有电压增益,该结构的调整范围有限,最大负载电流往往较小,但是soc的模块功耗往往也只有几十ma。

5.参见图3所示,第三种结构为采用fvf结构的电路结构,实际上是第一种结构的变种,适合全集成实现和快速响应场合,但是其线性调整率较差,而且,如果添加额外的共栅增益级以改善线性调整率的话,需要一定的稳态电流以维持环路稳定性,不利于降低静态功耗。

6.本实用新型的背景是给数模混合集成电路提供稳定的1.2v电压源,最大负载电流为20ma,所处的应用环境可能在1ns时间里完成最大电流和最小电流(约200ua)之间的切换,切换速率高达19.8a/μs;过冲电压要在1μs内恢复到稳态值附近。

7.第二种结构是本实用新型的全集成线性稳压器的基本实现框架。

8.由于低静态电流是线性稳压器的基本要求,误差放大器的带宽和输出摆率都是十分有限的,即便采用第二种结构,其固有的瞬态恢复速度也往往不能满足建立时间的要求。因此,一般都是需要采取额外的措施以加快功率传输管栅极电压的恢复速度,进而实现快速的瞬态恢复。

9.这里涉及到两个问题:(1)瞬变过冲的检测;(2)功率传输管栅极电压的恢复机制。其中:

10.(1)瞬变过冲的检测

11.传统的过冲检测机制是通过一个c-r高通网络监测输出电压的瞬变,问题在于,要提高阶跃检测幅度就得增加电阻和电容的大小,需要消耗较多的芯片面积;

12.(2)功率传输管栅极电压的恢复机制

13.在负载切换时输出电压过冲的本质在于功率传输管的栅极电压不能及时恢复到负反馈环路的线性调整范围内(这个范围实际上是非常小的,反比于环路增益)。原因在于占据ldo芯片主要面积的功率传输管的栅极寄生电容非常大!解决这一问题的基本途径也是两个:提高误差放大器的输出摆率,以及直接向功率传输管的栅极注入(或者抽取)一定的电流。第一种途径的响应速度一般要慢一点,但是不会发生过调整导致的震荡;第二种途径的响应速度快一点,但是可能会出现过调整导致的震荡,而且无法借助线性分析工具去预知其行为。

技术实现要素:

14.本实用新型目的是提供一种面积紧凑的自适应偏置nmos型ldo电路,通过采用非平衡负载差分放大器检测过冲并向误差放大器注入额外的偏置电流以提高瞬时输出摆率,进而实现过冲输出的快速恢复;同时,由于误差放大器始终在负反馈环路中,能够对功率传输管栅极充放电电流的大小进行控制,因而能够适应多种负载切换的情况。

15.本实用新型的技术方案是:一种面积紧凑的自适应偏置nmos型ldo电路,包括误差放大器电路、自适应偏置电流源电路、作为功率传输管的nmos管 n5、作为负载电阻的电阻r2、频率补偿电路、上过冲检测电路和下过冲检测电路,所述上过冲检测电路自适应控制nmos管n6的开启与关闭,所述下过冲检测电路自适应控制pmos管p5的开启与关闭;

16.所述上过冲检测电路被配置为在检测到发生上过冲时打开nmos管 n6,以向误差放大器电路提供额外的偏置电流,当输出上过冲电压恢复到接近稳态值时关闭nmos管n6;

17.所述下过冲检测电路被配置为在检测到发生下过冲时打开pmos管p5,并通过nmos管n7~n8构成的电流镜向误差放大器电路提供额外的偏置电流,当输出下过冲电压恢复到接近稳态值时关闭pmos管p5;

18.所述nmos管n5的漏极电性连接到电压源vdd1,源极电性连接到电阻r2的一端并作为ldo电路的输出电源端vp;

19.所述电阻r2的另一端接地。

20.上述技术方案中,所述误差放大器电路选用套筒式共源共栅结构,包括 nmos管n1~n4、pmos管p1~p4和偏置电流源ib1,其中,

21.所述pmos管p1的源极电性连接到电压源vdd2,栅极分别电性连接到pmos管p2的栅极、pmos管p3的漏极和nmos管n3的漏极,漏极电性连接到pmos管p3的源极;

22.所述pmos管p2的源极电性连接到电压源vdd2,漏极电性连接到 pmos管p4的源极;

23.所述pmos管p3的栅极分别电性连接到偏置电压源vb2和pmos管 p4的栅极;

24.所述pmos管p4的漏极分别电性连接到nmos管n5的栅极和nmos 管n4的漏极;

25.所述nmos管n3的栅极分别电性连接到偏置电压源vb1和nmos管 n4的栅极,源极电

性连接到nmos管n1的漏极;

26.所述nmos管n4的源极电性连接到nmos管n2的漏极;

27.所述nmos管n1的栅极电性连接到参考电压源vr,源极分别电性连接到nmos管n2的源极和经偏置电流源ib1接地;

28.所述nmos管n2的栅极分别电性连接到上过冲检测电路的输入端、下过冲检测电路的输入端和输出电源端vp。

29.上述技术方案中,所述自适应偏置电流源电路包括nmos管n6~n8和pmos管p5,其中,

30.所述pmos管p5的源极电性连接到电压源vdd2,栅极电性连接到下过冲检测电路的输出端,漏极分别电性连接到nmos管n7的栅极、漏极和 nmos管n8的栅极;

31.所述nmos管n6的源极接地,栅极电性连接到上过冲检测电路的输出端,漏极分别电性连接到nmos管n1的源极nmos管n2的源极;

32.所述nmos管n7的源极接地;

33.所述nmos管n8的源极接地,漏极电性连接到nmos管n6的漏极。

34.上述技术方案中,所述上过冲检测电路包括pmos管p9、pmos管p10、 nmos管n11、nmos管n12和偏置电流源ib3;

35.所述pmos管p9的源极分别电性连接到pmos管p10的源极和经偏置电流源ib3电性连接到电压源,栅极电性连接到参考电压源vr,漏极分别电性连接到nmos管n6的栅极和nmos管n11的漏极;

36.所述pmos管p10的栅极电性连接到输出电源端vp,漏极分别电性连接到nmos管n12的漏极、栅极和nmos管n11的栅极;

37.所述nmos管n11的源极接地;

38.所述nmos管n12的源极接地。

39.上述技术方案中,所述nmos管n11与nmos管n12的器件尺寸比例为2:1。

40.上述技术方案中,所述下过冲检测电路包括pmos管p7、pmos管p8、 nmos管n9和nmos管n10;

41.所述pmos管p7的源极分别电性连接到电压源和pmos管p8的源极,栅极分别电性连接到pmos管p8的栅极、漏极和nmos管n10漏极,漏极分别电性连接到pmos管p5的栅极和nmos管n9的漏极;

42.所述nmos管n9的源极分别电性连接到nmos管n10的源极和经偏置电流源ib2接地,栅极电性连接到参考电压源vr;

43.所述nmos管n10的栅极电性连接到输出电源端vp。

44.上述技术方案中,所述pmos管p7与pmos管p8的器件尺寸比例为 2:1。

45.上述技术方案中,还包括pmos管p6和电阻r1;

46.所述pmos管p6的源极和漏极均电性连接到nmos管n5的栅极,栅极电性连接到电阻r1的一端;

47.所述电阻r1的另一端接地。

48.本实用新型的优点是:

49.1.本实用新型引入一种非平衡负载差分放大器作为下过冲检测单元,具有芯片面

积小、瞬态注入电流大的优点。

50.2.本实用新型的过冲触发的额外电流注入误差放大器作为其偏置电流,这能够保证给nmos管n5的栅极充电的电流大小受到负反馈环路的控制,能够适应多种负载切换速度场合。

51.3.本实用新型的pmos管p6起到双重的作用,快速切换负载瞬间的稳压效果和频率补偿效果,实现了器件的功能复用,不需要额外的补偿电容,有利于节省芯片面积。

附图说明

52.下面结合附图及实施例对本实用新型作进一步描述:

53.图1为背景技术中采用pmos管作为功率传输管的ldo线性稳压器的基本电路结构图。

54.图2为背景技术中采用nmos管作为功率传输管的ldo线性稳压器的基本电路结构图。

55.图3为背景技术中采用fvf结构的ldo线性稳压器的基本电路结构图。

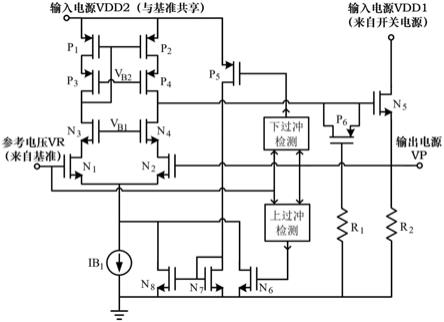

56.图4为本实用新型的线性稳压器的主体电路图。

57.图5为本实用新型的上过冲检测电路的电路结构图。

58.图6为本实用新型的下过冲检测电路的电路结构图。

59.图7为在典型工艺角下负载电流以1ns在200μa和20ma之间切换时本实用新型的输出电压(实线)与关闭自适应偏置的输出电压(虚线)的对比示意图。

60.图8为在典型工艺角下负载电流以1ns从200μa切换到20ma时本实用新型的上冲响应的局部放大图。

61.图9为在典型工艺角下负载电流以1ns从20ma切换到200μa时本实用新型的下冲响应的局部放大图。

62.图10为本实用新型在负载5ma、10ma、15ma、20ma时的环路特性示意图(负载100pf)。

63.图11为本实用新型在负载5ma、10ma、15ma、20ma时的线性调整率仿真结果示意图。

64.图12为本实用新型在输出压降为40mv、130mv、220mv、400mv时的负载调整率仿真结果示意图。

65.图13为本实用新型在负载电流分别为5ma、10ma、15ma、20ma时的最小压降示意图。

66.图14为本实用新型在负载电流分别为0.2ma、2ma、20ma时的psrr。

具体实施方式

67.实施例:

68.参见图4所示,一种面积紧凑的自适应偏置nmos型ldo电路,包括误差放大器电路、自适应偏置电流源电路、作为功率传输管的nmos管n5、作为负载电阻的电阻r2、频率补偿电路、上过冲检测电路和下过冲检测电路,所述上过冲检测电路自适应控制nmos管n6的开启与关闭,所述下过冲检测电路自适应控制pmos管p5的开启与关闭;

69.所述上过冲检测电路被配置为在检测到发生上过冲时打开nmos管 n6,以向误差放大器电路提供额外的偏置电流,当输出上过冲电压恢复到接近稳态值时关闭nmos管n6;

70.所述下过冲检测电路被配置为在检测到发生下过冲时打开pmos管p5,并通过nmos管n7~n8构成的电流镜向误差放大器电路提供额外的偏置电流,当输出下过冲电压恢复到接近稳态值时关闭pmos管p5;

71.所述nmos管n5的漏极电性连接到电压源vdd1,源极电性连接到电阻r2的一端并作为ldo电路的输出电源端vp;

72.所述电阻r2的另一端接地。

73.本实施例中,所述误差放大器电路选用套筒式共源共栅结构,包括 nmos管n1~n4、pmos管p1~p4和偏置电流源ib1,其中,

74.所述pmos管p1的源极电性连接到电压源vdd2,栅极分别电性连接到pmos管p2的栅极、pmos管p3的漏极和nmos管n3的漏极,漏极电性连接到pmos管p3的源极;

75.所述pmos管p2的源极电性连接到电压源vdd2,漏极电性连接到 pmos管p4的源极;

76.所述pmos管p3的栅极分别电性连接到偏置电压源vb2和pmos管 p4的栅极;

77.所述pmos管p4的漏极分别电性连接到nmos管n5的栅极和nmos 管n4的漏极;

78.所述nmos管n3的栅极分别电性连接到偏置电压源vb1和nmos管 n4的栅极,源极电性连接到nmos管n1的漏极;

79.所述nmos管n4的源极电性连接到nmos管n2的漏极;

80.所述nmos管n1的栅极电性连接到参考电压源vr,源极分别电性连接到nmos管n2的源极和经偏置电流源ib1接地;

81.所述nmos管n2的栅极分别电性连接到上过冲检测电路的输入端、下过冲检测电路的输入端和输出电源端vp。

82.本实施例中,所述自适应偏置电流源电路包括nmos管n6~n8和pmos 管p5,其中,

83.所述pmos管p5的源极电性连接到电压源vdd2,栅极电性连接到下过冲检测电路的输出端,漏极分别电性连接到nmos管n7的栅极、漏极和 nmos管n8的栅极;

84.所述nmos管n6的源极接地,栅极电性连接到上过冲检测电路的输出端,漏极分别电性连接到nmos管n1的源极nmos管n2的源极;

85.所述nmos管n7的源极接地;

86.所述nmos管n8的源极接地,漏极电性连接到nmos管n6的漏极。

87.参见图5所示,所述上过冲检测电路包括pmos管p9、pmos管p10、 nmos管n11、nmos管n12和偏置电流源ib3;

88.所述pmos管p9的源极分别电性连接到pmos管p10的源极和经偏置电流源ib3电性连接到电压源,栅极电性连接到参考电压源vr,漏极分别电性连接到nmos管n6的栅极和nmos管n11的漏极;

89.所述pmos管p10的栅极电性连接到输出电源端vp,漏极分别电性连接到nmos管n12的漏极、栅极和nmos管n11的栅极;

90.所述nmos管n11的源极接地;

91.所述nmos管n12的源极接地。

92.本实施例中,所述nmos管n11与nmos管n12的器件尺寸比例为2:1。

93.参见图6所示,所述下过冲检测电路包括pmos管p7、pmos管p8、 nmos管n9和nmos管n10;

94.所述pmos管p7的源极分别电性连接到电压源和pmos管p8的源极,栅极分别电性连接到pmos管p8的栅极、漏极和nmos管n10漏极,漏极分别电性连接到pmos管p5的栅极和nmos管n9的漏极;

95.所述nmos管n9的源极分别电性连接到nmos管n10的源极和经偏置电流源ib2接地,栅极电性连接到参考电压源vr;

96.所述nmos管n10的栅极电性连接到输出电源端vp。

97.本实施例中,所述pmos管p7与pmos管p8的器件尺寸比例为2:1。

98.本实施例中,还包括pmos管p6和电阻r1;

99.所述pmos管p6的源极和漏极均电性连接到nmos管n5的栅极,栅极电性连接到电阻r1的一端;

100.所述电阻r1的另一端接地。

101.soc芯片的io环供电标准一般是2.5v或者3.3v,110nm以后节点的数字内核供电电压一般是1.2v,因此,这种用于给数字内核供电的线性稳压器有足够的电压空间采用nmos作为nmos管,即本实用新型的电路结构。

102.nmos型全集成ldo的优点在于快速响应、要求的最小压降小、电源抑制比高、带宽恒定等,为了缓解环路增益不足的缺点,本实用新型的误差放大器采用套筒式共源共栅结构,参见图4所示。误差放大器中的nmos 管n1~n4和pmos管p1~p4都偏置在亚阈值区,以保证在偏置电流增加几十倍的时候还能够工作在饱和区。发生上过冲时打开nmos管n6管以提供额外的偏置电流,发生下过冲时打开pmos管p5管以提供额外的偏置电流。 pmos管p6起到两个作用:(1)其源极和漏极与n阱衬底之间的pn结在输出下冲时能够利用反向稳压特性削减下冲的幅度;(2)其栅源和栅漏寄生电容和电阻r1构成频率补偿结构,引入的额外零点使得本实用新型也能够在挂载nf级电容负载时保持稳定。

103.本实用新型的静态电流分配如下:偏置电流源ib1提供的偏置电流为 3μa,下过冲检测和上过冲检测模块各消耗约0.5μa电流,输出级的空载静态电流约为5μa。整个ldo加上偏置电路的偏置电流不超过10μa。

104.本实用新型的实施方案在55nm cmos工艺下实现,电压源vdd1采用大于1.3v的电源供电即可,电压源vdd2与基准共用电源,一般在2.5~3.6v 之间。本实用新型的空载静态电流小于10μa。

105.下面结合附图具体说明本实用新型的优点

106.参见图7所示,可以看到,当负载电流以1ns在200μa和20ma之间切换时,本实用新型具有明显的过冲恢复速度加快的效果,下过冲恢复速度增加的尤其明显。

107.参见图8所示,是上过冲响应的局部放大图,可以看到,上过冲电压可以在175ns内恢复到终值的10%范围内(即1.32v),大约300ns就可以恢复到终值附近1%范围内。

108.参见图9所示,是下过冲响应的局部放大图,可以看到,下过冲电压可以在40ns内恢复到终值的10%范围内(即1.08v),大约60ns就可以恢复到终值附近1%范围内。

109.参见图10所示,是五种负载电流情况下的环路特性波特图,正常工作时具有带宽基本恒定的特点,空载的相位裕度为40度。

110.参见图11所示,是不同负载电流时输出电压随输出压降变化的曲线,由仿真波形可以计算出,当输出压降从50mv变化到300mv时,在负载电流为 5ma时的平均线性调整率为

0.0012%(12μv/v);负载电流为10ma,线性调整率为0.0018%(18μv/v);负载电流为15ma,线性调整率为0.0024% (24μv/v);负载电流为20ma时,线性调整率为0.003%(29μv/v)。

111.参见图12所示,是不同压降时输出电压随负载电流的变化情况,由此可以计算出本实用新型压降40mv时,满负载范围内的平均负载调整率为 1.67μv/ma;压降130mv时,满负载范围内的平均负载调整率为1.19μv/ma;压降220mv时,满负载范围内的平均负载调整率为1.14μv/ma;压降400mv 时,满负载范围内的平均负载调整率为1.13μv/ma。

112.参见图13所示,是不同负载电流时输出电压随输出压降变化的曲线。如果以线性调整率小于5mv/v为标准,在负载电流为5ma时,使输出电压保持稳压的最小压降约为10mv;负载电流为10ma时,使输出电压保持稳压的最小压降约为15mv;负载电流为15ma时,使输出电压保持稳压的最小压降约为20mv;负载电流为20ma时,使输出电压保持稳压的最小压降约为25mv。这意味着本实用新型具有极高的效率。

113.参见图14所示,是负载电流分别为0.2ma、2ma、20ma时的psrr。从仿真波形可以看出在低频psrr可达100db以上。频率为1mhz时,负载电流为0.2ma时的psrr为54db;负载电流为2ma时的psrr为51db;负载电流为20ma时的psrr为44db。最差的psrr大于10db。

114.当然上述实施例只为说明本实用新型的技术构思及特点,其目的在于让熟悉此项技术的人能够了解本实用新型的内容并据以实施,并不能以此限制本实用新型的保护范围。凡根据本实用新型主要技术方案的精神实质所做的修饰,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1