一种基于FPGA的MEMS振镜驱动信号的相位同步方法与流程

一种基于fpga的mems振镜驱动信号的相位同步方法

技术领域:

1.本发明涉及微振镜控制领域,具体涉及一种基于fpga的mems振镜驱动信号的相位同步方法。

背景技术:

2.mems(micro-electro-mechanical system,微机电机械系统)产业的发展对信息、医疗、空间技术等领域产生的重大影响,在此背景下,诸多mems产品应运而生,其中mems振镜是基于mems技术制作的可驱动微镜,镜面直径通常只有几毫米。与传统的光学扫描镜相比,具有重量轻、体积小、易于大批量生产、生产成本较低的优点。在光学、机械性能和功耗方面表现更为突出,在高清投影、激光雷达、三维扫描等领域有广泛应用前景。

3.按照驱动原理,mems振镜可分为静电驱动、电磁驱动、压电驱动、热电驱动几种类型,目前常见的有静电驱动和电磁驱动两种。静电驱动是利用带电导体之间产生的静电吸引力,该力作用到镜面上,在力矩的作用下,进行扭转运动;电磁驱动是利用洛伦兹力驱使镜面发生扭转,在其结构上,电磁驱动式的mems振镜加上磁性材料,通过电流与磁性材料产生的磁场相互作用,产生电磁力使得镜面发生扭转运动。不管以何种方式驱动,都需要外界产生一定的驱动信号,以获得振动所需的扭转力。从工作模式来看,mems振镜可分为谐振态和非谐振态两类。非谐振态工作方式的工作频率可以自由调整,可以从零开始到微镜结构固有谐振频率范围以内实时调节;谐振态工作方式要求mems振镜需要工作在谐振频点下,扫描频率偏离谐振频点扫描角度会大幅降低,甚至不能正常工作。

4.对于二维mems振镜,在相互垂直的两个方向均可振动扫描,即x轴(快轴)方向和y轴(慢轴)方向。在两轴均采用谐振态工作模式的情况下,mems振镜的快轴和慢轴都工作在各自的频率范围内。两轴同时振动时,振动的轨迹呈李萨如图形,轨迹的形状取决于两轴振动的频率比、振幅比和初相位差。此三种因素由驱使微镜振动的驱动信号所决定,其中,频率和振幅都可直观的进行调节,两轴的驱动信号设定初相位差时,需要进行相位同步,通常是分别预先设定两轴驱动信号的初相位,再选择一个时刻将两个信号的相位同时重置到初相位,以获得特定的初相位差。因选择相位同步的时刻具有随机性,可能导致驱动信号发生跳变,从而影响振镜的正常工作状态,甚至损坏振镜结构。

技术实现要素:

5.针对现有技术的不足,本发明的目的在于提供一种基于fpga的mems振镜驱动信号的相位同步方法,在设定两轴驱动信号的初相位差时,利用fpga的高速处理特性,在mems振镜的快轴驱动信号和慢轴驱动信号两者都即将到达初相位时,两轴驱动信号同时回到初相位,使mems振镜的两轴驱动信号在相位相对连续的情况下进行同步,获得特定的初相位差。

6.为了实现上述发明目的,本发明采用了如下技术方案:

7.一种基于fpga的mems振镜驱动信号的同步方法,其特征在于包括以下步骤:

8.a.采用fpga实现dds信号发生器产生驱动信号,将周期的信号波形存储到fpga的

rom中,rom的深度即为一个周期的采样点数,rom地址与psw存在线性映射关系,通过控制psw能够循环读出rom中的信号;

9.b.通过相位累加器实现对psw的控制,即在每个时钟上升沿,psw值增加一个频率控制字fsw(frequency setting word),当psw值大于pswmax时,psw值回到psw-pswmax,如此循环,将psw值映射到rom地址,即可读出所需频率的信号,根据dds原理可以得出输出信号的频率f

out

为

[0010][0011]

其中f

clk

为dds的工作时钟频率,fsw为频率控制字,psw

max

是最大相位控制字;

[0012]

控制mems振镜的两轴振动需要上述fpga中两个rom产生驱动信号,两个rom由相互独立的相位累加器控制。

[0013]

c.对mems振镜的两轴驱动信号进行相位同步来获得特定的初相位差,由两轴驱动信号的初相位差得出两轴驱动信号的初相位,根据映射关系得出两轴驱动信号的初相位控制字,快轴驱动信号的初相位控制字由psw1表示,慢轴驱动信号的初相位控制字由psw2表示;

[0014]

d.设定相位同步的窗口期为psw

max

/2n,n=0,1,2,3

…

;

[0015]

e.在快轴驱动信号的psw值处于psw1-psw

max

/2n至psw1时,快轴同步使能信号sync_ready_out1拉高;同理,在慢轴驱动信号的psw值处于psw2-pswmax/2n至psw2时,慢轴同步使能信号sync_ready_out2拉高;

[0016]

f.获得两轴同步使能信号的重合部分,

[0017]

sync_ready=sync_ready_out1&sync_ready_out2

ꢀꢀꢀꢀꢀꢀ

(2)

[0018]

其中sync_ready是相位同步使能信号,sync_ready高电平有效,表示可以进行相位同步操作,在sync_ready信号的上升沿,将快轴的psw值置为psw1,将慢轴的psw值置为psw2,至此,快轴和慢轴的驱动信号相位在同一时刻回到初相位,完成了相位同步操作。

[0019]

上述技术方案中:

[0020]

所述驱动信号是用于驱使mems振镜振动的电压信号或电流信号,包括驱使mems振镜快轴振动的快轴驱动信号,和驱使mems振镜慢轴振动的慢轴驱动信号,两轴驱动信号均为周期信号,其相位在0到360度之间周期循环。

[0021]

所述相位同步是指使mems振镜的快轴驱动信号和慢轴驱动信号在同一时刻回到初相位,目的是获得特定的初相位差,初相位可以设置为0到360度之间的任一值。

[0022]

本发明中,信号在任意时刻的相位可由psw(phase setting word,相位控制字)表示,相位与相位控制字具有线性映射关系,相位为360度时对应相位控制字的最大值psw

max

。驱动信号相位同步的窗口期为psw

max

/2n(n=0,1,2,3

…

),当n值越大时,相位同步时的相位值越接近初相位。

[0023]

设定快轴驱动信号的初相位为psw1,设定慢轴驱动信号的初相位为psw2,为了保证信号的连续性,应在相位即将到达初相位时进行相位同步,且同步时的相位值应尽可能的接近初相位。当快轴驱动信号的相位值处于psw1-psw

max

/2n和psw1之间时,快轴进入同步准备状态。同理,当慢轴驱动信号的相位值处于psw2-psw

max

/2n和psw2之间时,慢轴进入同步准备状态。两轴同时处于同步准备状态时,进行相位同步操作。

[0024]

当n等于0时,驱动信号相位同步的窗口期是整个信号周期的任一时期,等同于直接进行相位同步操作。当n值越大时,相位同步时的相位值越接近初相位,对信号连续性的影响越小,但完成相位同步操作所等待的时间越长。

[0025]

本发明的优点在于:本发明可以显著改善直接相位同步带来的驱动信号形状突变,保证驱动信号在相位同步时相位的连续性,减小相位同步时对mems振镜造成的不良影响。

附图说明:

[0026]

图1为本发明一实施例相位累加器示意图;

[0027]

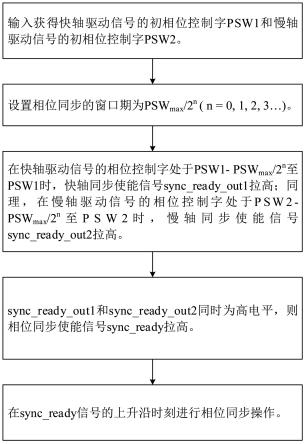

图2为本发明一实施例相位同步方法流程图;

[0028]

图3为本发明一实施例相位控制字与同步使能信号时序图;

具体实施方式:

[0029]

下面对本发明的实施例作详细说明。

[0030]

本发明的内容是一种基于fpga的mems振镜驱动信号的同步方法,本实施例中,驱动信号的产生方式是采用fpga实现dds(direct digital synthesis,直接频率合成)信号发生器。首先,将周期的信号波形存储到fpga的rom中,rom的深度即为一个周期的采样点数,rom地址与psw存在线性映射关系,通过控制psw能够循环读出rom中的信号。

[0031]

如图1所示,通过相位累加器实现对psw的控制,即在每个时钟上升沿,psw值增加一个fsw(frequency setting word,频率控制字),当psw值大于psw

max

时,psw值回到psw-psw

max

,如此循环。将psw值映射到rom地址,即可读出所需频率的信号,根据dds原理可以得出输出信号的频率f

out

为

[0032][0033]

其中f

clk

为dds的工作时钟频率,fsw为频率控制字,psw

max

是最大相位控制字。

[0034]

控制mems振镜的两轴振动需要上述两个rom产生驱动信号,两个rom由相互独立的相位累加器控制。

[0035]

对mems振镜的两轴驱动信号进行相位同步来获得特定的初相位差,步骤如图2所示。

[0036]

首先,由两轴驱动信号的初相位差得出两轴驱动信号的初相位,根据映射关系得出两轴驱动信号的初相位控制字。快轴驱动信号的初相位控制字由psw1表示,慢轴驱动信号的初相位控制字由psw2表示。

[0037]

进一步的,设定相位同步的窗口期为psw

max

/2n(n=0,1,2,3

…

),其中n值越大,窗口期越小,表示相位同步时的相位值越接近初相位,从而对信号连续性的影响就越小。而造成的不良影响是,两轴相位同步的窗口期重合的机会变小,相位同步的等待时间会变长。当同步时间无要求时,起始可设定较大的n值;而对同步时间比较敏感时,可根据信号的相位同步时间和信号的连续性两种因素确定n的初始值。

[0038]

进一步的,在快轴驱动信号的psw值处于psw1-psw

max

/2n至psw1时,即图3中的

△

t1时间段,快轴同步使能信号sync_ready_out1拉高;同理,在慢轴驱动信号的psw值处于

psw2-psw

max

/2n至psw2时,即图3中的

△

t2时间段,慢轴同步使能信号sync_ready_out2拉高。

[0039]

进一步的,获得两轴同步使能信号的重合部分,即图3中

△

t时间段。

[0040]

sync_ready=sync_ready_out1&sync_ready_out2

ꢀꢀꢀꢀꢀꢀ

(2)

[0041]

其中sync_ready是相位同步使能信号,sync_ready高电平有效,表示可以进行相位同步操作。在sync_ready信号的上升沿,将快轴的psw值置为psw1,将慢轴的psw值置为psw2。至此,快轴和慢轴的驱动信号相位在同一时刻回到初相位,完成了相位同步操作。

[0042]

附图中的流程图和示意图显示了本发明的实施例的fpga算法流程以及功能体系架构,其中流程图的每个方框可以代表一个模块、程序段或指令的一部分。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1