用来测试具有排错功能的芯片上时钟控制器的测试装置的制作方法

本发明涉及测试装置,尤其涉及用来测试芯片上时钟控制器的测试装置。

背景技术:

1、申请人的美国专利(专利号:us 10,605,861 b2)公开一种集成电路测试装置。然而,若该集成电路测试装置本身不正常运行(例如:基于设定错误、设计错误或制造瑕疵,该集成电路测试装置迫使它的芯片时钟控制器仅能输出用于实现一排错功能的一低速时钟),包含该集成电路测试装置的产品可能会面临客退(return merchandiseauthorization(rma))问题。

技术实现思路

1、本公开的目的之一在于提供一种测试装置,以测试具有一排错功能的一芯片上时钟控制器,从而避免现有技术的问题。

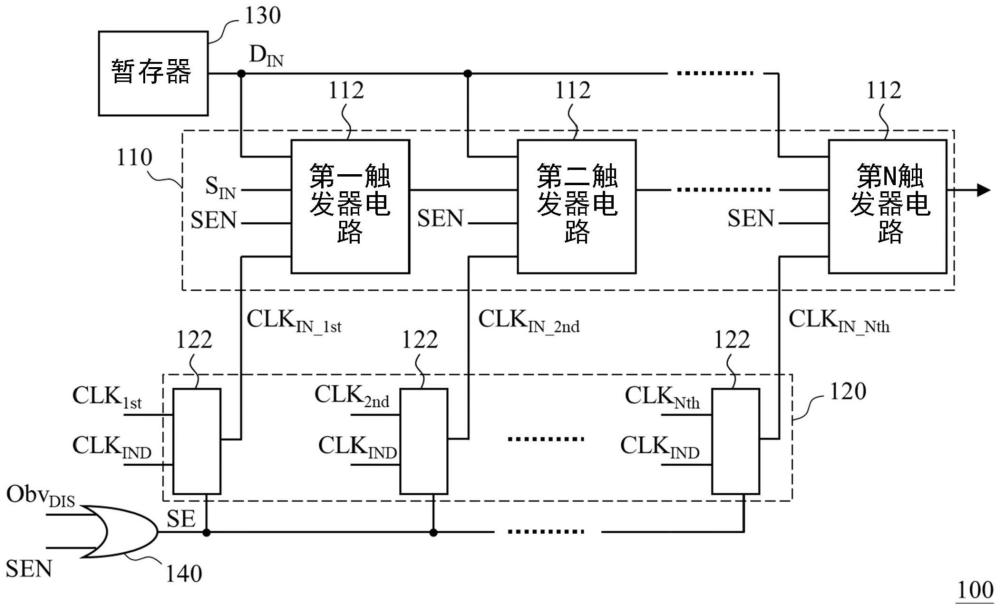

2、本公开的测试装置的一实施例用来测试一芯片上时钟控制器。该实施例包含一扫描链与一测试电路。该扫描链包含n个触发器电路,其中该n为一正整数。该n个触发器电路的一第k触发器电路包含一第k输入切换器以及一第k触发器,其中该k为不大于该n的一正整数。该第k输入切换器用来依据一扫描使能(scan enable(sen))信号输出一输入信号,其中该输入信号为一第一输入信号与一第二输入信号的其中之一。该第k触发器用来依据一输入时钟输出一存储信号作为一第k输出信号,其中该存储信号为该第一输入信号与该第二输入信号的其中之一。该测试电路包含n个选择电路。该n个选择电路耦接该n个触发器电路,其中该n个选择电路的一第k选择电路对应该第k触发器电路。该第k选择电路包含:一第k时钟切换器,用来依据一选择信号输出一第k观察时钟与一独立时钟的其中之一作为该输入时钟给该第k触发器,其中在一排错电路测试模式下,该选择信号由该sen信号决定,该第k观察时钟来自于该芯片上时钟控制器的一第k芯片上时钟电路。基于上述,该第k输入切换器先依据该sen信号的一第一信号值输出该第一输入信号,使得该第k触发器依据该输入时钟存储该第一输入信号作为该存储信号,此时该第一输入信号的值为一第一输入值;然后,该第k输入切换器依据该sen信号的一第二信号值输出该第二输入信号,此时该第k触发器依据该输入时钟存储该第二输入信号作为该存储信号或保留该第一输入信号作为该存储信号,该第二输入信号的值为不同于该第一输入值的一第二输入值;接下来,该第k触发器的该第k输出信号的值(亦即:该第一输入值或该第二输入值)指出该输入时钟是否依据测试设定触发或不触发该第k触发器,从而指出用于传输该输入时钟的一或多个受测电路是否正常运行。

3、本公开的测试装置的另一实施例用来测试一芯片上时钟控制器。该实施例包含一扫描链与一测试电路。该扫描链包含n个触发器电路。该n个触发器电路的任一触发器电路用来先存储一第一输入信号作为一存储信号,然后依据一输入时钟存储一第二输入信号作为该存储信号或保留该第一输入信号作为该存储信号,接着输出该存储信号,其中该n为正整数。由于该第一输入信号的值不同于该第二输入信号的值,该存储信号的值可指出该任一触发器电路是否在测试设定下依据该输入时钟存储该第二输入信号或保留该第一输入信号,从而指出用于传输该输入时钟的一或多个受测电路是否正常运行。该测试电路包含n个选择电路,该n个选择电路对应该n个触发器电路。该n个选择电路的任一选择电路用来依据该测试设定输出一观察时钟与一独立时钟的其中之一作为该输入时钟,以输出该输入时钟给该任一选择电路所对应的该n个触发器电路之一,其中该观察时钟来自于该芯片上时钟控制器。

4、有关本发明的特征、实作与技术效果,兹配合附图作优选实施例详细说明如下。

技术特征:

1.一种测试装置,用来测试一芯片上时钟控制器,该测试装置包含:

2.如权利要求1所述的测试装置,其中该第k观察时钟为一锁相回路时钟与一稳定时钟的其中之一;在该排错电路测试模式下,该一或多个受测电路包含该第k时钟切换器与该第k芯片上时钟电路的一多工器,且当该第k输出信号的值为该第一输入值时,该第k输出信号指出该第k触发器未被触发以存储该第二输入信号,从而指出该一或多个受测电路的至少其中之一不正常运行。

3.如权利要求1所述的测试装置,其中该第k观察时钟为一锁相回路时钟、一稳定时钟以及该锁相回路时钟的一除频时钟的其中之一;在该排错电路测试模式的一第一测试流程中,该一或多个受测电路包含该第k时钟切换器与该第k芯片上时钟电路的一第一多工器,且当该第k输出信号的值为该第一输入值时,该第k输出信号指出该第k触发器未被触发以存储该第二输入信号,从而指出该一或多个受测电路不正常运行,该第一多工器用来输出该锁相回路时钟与该稳定时钟的其中之一。

4.如权利要求1所述的测试装置,其中该第k观察时钟为一锁相回路时钟、一稳定时钟以及该锁相回路时钟的一除频时钟的其中之一;在该排错电路测试模式的一第二测试流程中,该一或多个受测电路包含该第k芯片上时钟电路的一第二多工器,且当该第k输出信号的值为该第二输入值时,该第k输出信号指出该第k触发器被触发以存储该第二输入信号,从而指出该一或多个受测电路不正常运行,该第二多工器用来输出该除频时钟或者该锁相回路时钟与该稳定时钟的其中之一。

5.如权利要求1所述的测试装置,其中该测试电路进一步包含:

6.如权利要求5所述的测试装置,其中该第k观察时钟为一锁相回路时钟与一稳定时钟的其中之一;在该正常测试模式下,该一或多个受测电路包含该或门与第k时钟切换器,且当该第k输出信号的值为该第二输入值时,该第k输出信号的值指出该第k触发器被触发以存储该第二输入信号,从而指出该一或多个受测电路不正常运行。

7.如权利要求1所述的测试装置,进一步包含该芯片上时钟控制器,其中该芯片上时钟控制器包含n个芯片上时钟电路,该n个芯片上时钟电路耦接该n个选择电路,且包含该第k芯片上时钟电路,该n个芯片上时钟电路的任一芯片上时钟电路包含:

8.如权利要求7所述的测试装置,其中该至少一多工器为一单一多工器,该单一多工器用来输出该稳定时钟与该锁相回路时钟的其中之一,以作为该观察时钟。

9.如权利要求7所述的测试装置,其中该至少一多工器包含:

10.一种测试装置,用来测试一芯片上时钟控制器,该测试装置包含:

技术总结

一种用来测试具有一排错功能的一芯片上时钟控制器的测试装置。该测试装置包含一扫描链与一测试电路。该扫描链包含N个触发器电路。任一触发器电路先存储一第一输入信号作为一存储信号,然后依据一输入时钟存储一第二输入信号作为该存储信号或者依据该输入时钟保留目前的存储信号,接着输出该存储信号。基于该第一与第二输入信号的值不同,该存储信号的值可指出该任一触发器电路是否在测试设定下依据该输入时钟存储该第二输入信号或保留目前的存储信号,从而指出用于传输该输入时钟的受测电路是否正常运行。该测试电路依据该测试设定输出一观察时钟与一独立时钟的其中之一作为该输入时钟,其中该观察时钟来自于该芯片上时钟控制器。

技术研发人员:永昇平,薛培英

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!