射频偏置电路的制作方法

本公开涉及集成电路,尤其涉及射频电路,具体涉及一种射频偏置电路。

背景技术:

1、当前的射频偏置电路多采用的绝对温度成正比(proportional to absolutetemperature,ptat)电流源偏置电路,存在受工艺、温度、供电电压等影响,出现增益变化较大的问题,如ptat电流偏置易受工艺角影响,并且利用ptat电流产生的偏置在高温端无法完全补偿增益损失,也不具有增益级较多时的温度增益补偿作用,使得上述射频电路在带宽内无法获得相对稳定的增益。

技术实现思路

1、本公开提供了一种射频偏置电路。

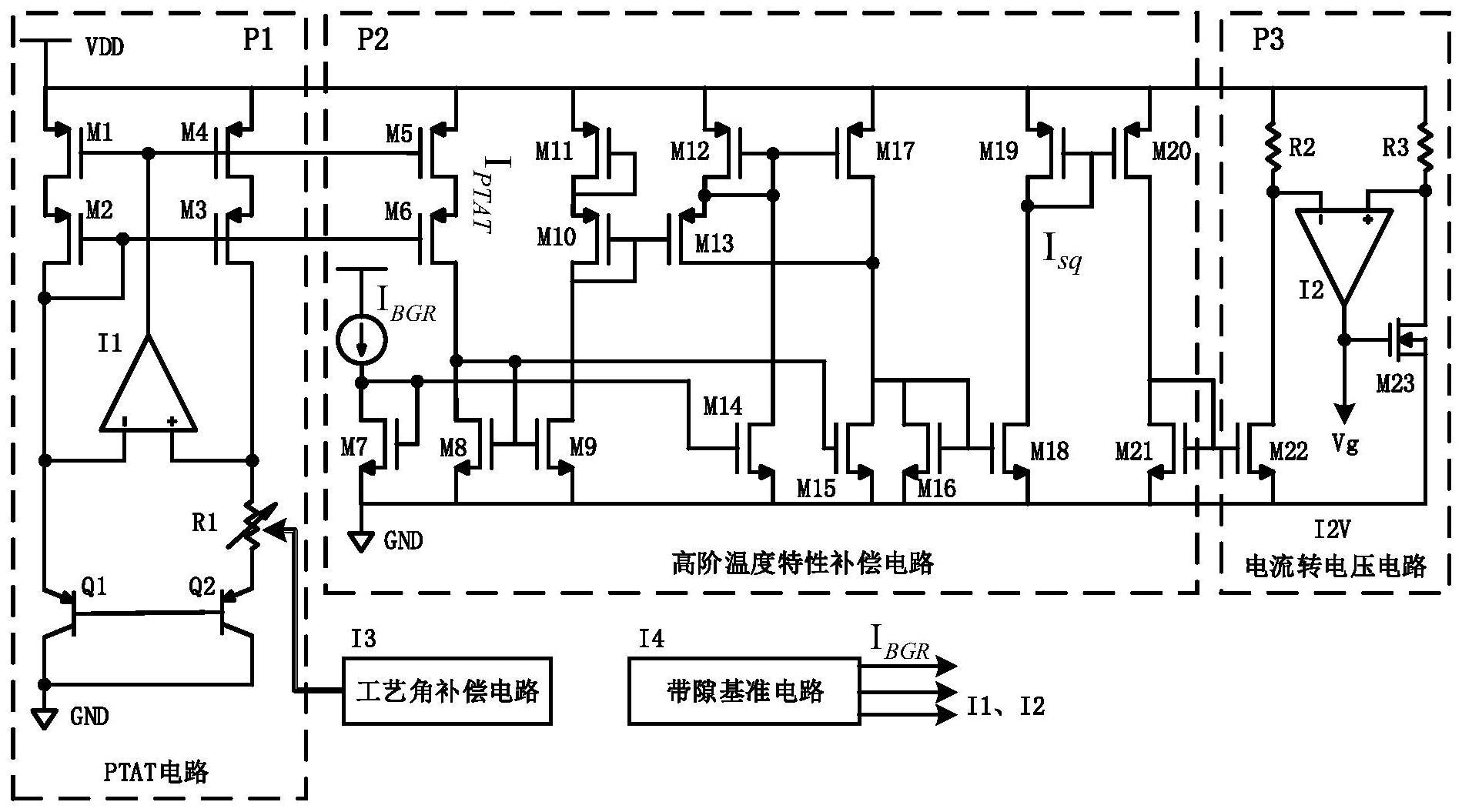

2、根据本公开的第一方面,提供了一种射频偏置电路。该射频偏置电路包括ptat电路p1和工艺角补偿电路i3;

3、其中,所述ptat电路p1包括晶体管m1、晶体管m2、晶体管m3、晶体管m4、运算放大器i1、晶体管q1、晶体管q2以及可调电阻r1;

4、所述晶体管m1的源级与电源端vdd连接,漏极与所述晶体管m2的源级连接,栅极与所述晶体管m4的栅极连接;所述晶体管m4的源级与电源端vdd连接,漏极与所述晶体管m3的源级连接;所述晶体管m2的漏极和所述晶体管m2栅极连接,栅极与所述晶体管m3的栅极连接;所述运算放大器i1的反相输入端与所述晶体管m2的漏极连接,同相输入端与所述晶体管m3的漏极连接,输出端与所述晶体管m1和所述晶体管m4的栅极连接;所述晶体管q1的栅极与所述晶体管q4的栅极连接,源级与所述晶体管m2的漏极连接,漏极接地;所述晶体管q2的源级通过所述可调电阻r1与所述晶体管m3的漏极连接,漏极接地;所述可调电阻r1与所述工艺角补偿电路i3连接;所述工艺角补偿电路i3用于通过控制所述可调电阻r1补偿所述ptat电路p1电流因工艺角的变化。

5、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述晶体管m1、所述晶体管m2、所述晶体管m3以及所述晶体管m4共同构成电流镜结构;所述电流镜结构为两级mos管结构。

6、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述晶体管q1和所述晶体管q2为三极管;所述晶体管q1、所述晶体管q2以及所述电阻r1共同构成温度补偿结构。

7、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述射频偏置电路还包括高阶温度特性补偿电路p2和电流转电压电路p3;

8、所述高阶温度特性补偿电路p2的输入端分别与电源端vdd、以及所述晶体管m4和所述晶体管m3的栅极连接,输出端与所述电流转电压电路p3连接;

9、所述高阶温度特性补偿电路p2用于将所述ptat电路p1产生的iptat进行平方高阶整形生成的isq提供给所述电流转电压电路p3。

10、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述高阶温度特性补偿电路p2包括:

11、晶体管m5、晶体管m6、晶体管m8、晶体管m9、晶体管m10、晶体管m11、晶体管m12、晶体管m13、晶体管m14、晶体管m15、晶体管m16、晶体管m17、晶体管m18、晶体管m19、晶体管m20以及晶体管m21;

12、其中,所述晶体管m5的栅极与所述晶体管m4的栅极连接,源级与电源端vdd连接,漏极与所述晶体管m6的源级连接;所述晶体管m6的栅极与所述晶体管m3的栅极连接,漏极分别与所述晶体管m8的漏极、所述晶体管m15的栅极、以及所述晶体管m8和所述晶体管m9的栅极连接;所述晶体管m11的源级与电源端vdd连接,栅极和漏极与所述晶体管m10的源级连接;所述晶体管m10的漏极分别与所述晶体管m9的漏极、以及所述晶体管m10和所述晶体管m13的栅极连接;所述晶体管m12的源级与电源端vdd连接,漏极分别与所述晶体管m13的源级、所述晶体管m14的漏极、以及所述晶体管m12和所述晶体管m17的栅极连接;所述晶体管m13的漏极分别与所述晶体管m17的漏极和所述晶体管m15的漏极连接;所述晶体管m17的源级与电源端vdd连接,漏极分别与所述晶体管m15的漏极、所述晶体管m16的漏极、以及所述晶体管m16和所述晶体管m18的栅极连接;所述晶体管m19的源级与电源端vdd连接,漏极分别与所述晶体管m18的漏极、以及所述晶体管m19和所述晶体管m20的栅极连接;所述晶体管m20的源级与电源端vdd连接,漏极分别与所述晶体管m21的漏极和所述电流转电压电路p3连接;所述晶体管m21的栅极与所述电流转电压电路p3连接;所述晶体管m8、所述晶体管m9、所述晶体管m14、所述晶体管m15、所述晶体管m16、所述晶体管m18以及所述晶体管m21的源级接地。

13、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述晶体管m10、所述晶体管m11、所述晶体管m12以及所述晶体管m13共同构成跨导线性环结构。

14、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述跨导线性环结构中工作在饱和区的晶体管之间的驱动电压满足所述晶体管m10与所述晶体管m11的驱动电压之和等于所述晶体管m12与所述晶体管m13的驱动电压之和。

15、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述电流转电压电路p3包括:

16、晶体管m22、晶体管m23、电阻r2、电阻r3以及运算放大器i2;

17、其中,所述运算放大器i2的同相输入端与所述晶体管m23的漏极连接,并通过所述电阻r3与电源端vdd连接;反相输入端与所述晶体管m22的漏极连接,并通过所述电阻r2与电源端vdd连接;输出端与所述晶体管m23的栅极连接,输出端用于输出电压增益;所述晶体管m22的栅极与所述晶体管m21的栅极连接,源级与所述晶体管m23的源级连接,并接地。

18、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述射频偏置电路还包括带隙基准电流源电路i4;

19、所述带隙基准电流源电路i4用于产生所述运算放大器i1和所述运算放大器i2的偏置电流。

20、如上所述的方面和任一可能的实现方式,进一步提供一种实现方式,所述高阶温度特性补偿电路p2还包括晶体管m7;

21、所述带隙基准电流源电路i4分别与所述晶体管m7的漏极和栅极、以及所述晶体管m14的栅极连接;所述晶体管m7的源级接地;

22、所述带隙基准电流源电路i4还用于产生和电源电压、温度无关的恒定电流ibgr,并给所述晶体管m7供电。

23、本技术实施例提供的一种射频偏置电路,包括ptat电路p1和工艺角补偿电路i3;ptat电路p1包括晶体管m1、晶体管m2、晶体管m3、晶体管m4、运算放大器i1、晶体管q1、晶体管q2以及可调电阻r1;晶体管m1的源级与电源端vdd连接,漏极与晶体管m2的源级连接,栅极与晶体管m4的栅极连接;晶体管m4的源级与电源端vdd连接,漏极与晶体管m3的源级连接;晶体管m2的漏极和晶体管m2栅极连接,栅极与晶体管m3的栅极连接;运算放大器i1的反相输入端与晶体管m2的漏极连接,同相输入端与晶体管m3的漏极连接,输出端与晶体管m1和晶体管m4的栅极连接;晶体管q1的栅极与晶体管q4的栅极连接,源级与晶体管m2的漏极连接,漏极接地;晶体管q2的源级通过可调电阻r1与晶体管m3的漏极连接,漏极接地;可调电阻r1与工艺角补偿电路i3连接;基于此,ptat电路p1和工艺角补偿电路i3共同构成了具有工艺角补偿功能的ptat电路,工艺角补偿电路i3通过控制可调电阻r1补偿ptat电路p1电流因工艺角的变化,能够使得射频电路在带宽内获得相对稳定的增益。

24、应当理解,

技术实现要素:

部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!