基准电压产生电路及芯片的制作方法

本发明涉及集成电路领域,具体地涉及一种基准电压产生电路以及一种芯片。

背景技术:

1、基准电压电路广泛地应用于模拟电路中,用于提供与工艺、电压和温度无关的电压,该电压可用于高精度数据转换器、大规模数字soc等模块或芯片中。在工业领域的高精度数据采集系统中,芯片的采样精度受制于芯片上基准电压源的抗电源干扰能力、工作温度范围、负载能力。为了保证芯片在宽输入电压、宽工作温度范围下稳定可靠工作,降低甚至消除基准波动带来的采样精度降低的问题,亟需研制一种宽温度范围高电源抑制、低温度漂移的基准电压产生电路,以解决高精度采样系统面临的电压波动、宽温度工作引起参考电压变化,从而导致采样精度降低的难题。

2、现有的技术中主要通过一个传统的带隙基准核心电路,实现一个不随工艺、温度、电压变化的带隙基准电压,该方案提供一个一阶温度补偿的参考电压,该电压随温度变化较大,并且基准电压源的电源抑制能力较低。

技术实现思路

1、本发明提供一种低温漂、高电源抑制的基准电压产生电路。

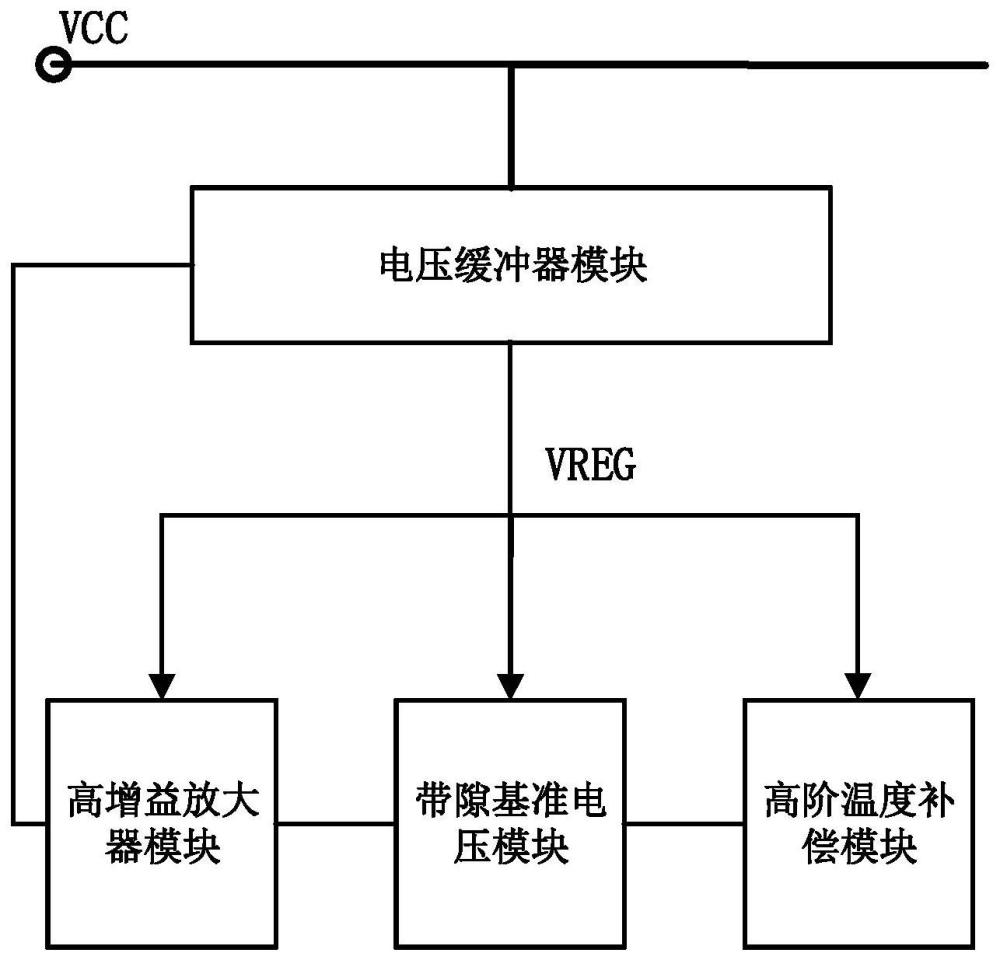

2、本发明提供的基准电压产生电路,包括:电压缓冲器模块、高增益放大器模块、带隙基准电压模块以及高阶温度补偿模块;所述电压缓冲器模块用于同时为所述高增益放大器模块、带隙基准电压模块以及高阶温度补偿模块提供工作电压;所述带隙基准电压模块与所述高增益放大器模块以及电压缓冲器模块连接,用于产生温度补偿的基准电压;所述高阶温度补偿模块与所述带隙基准电压模块连接,用于消除所述带隙基准电压模块输出的基准电压的高阶温度项。

3、本发明实施例中,所述带隙基准电压模块包括:第一三极管q1、第二三极管q2、第一电阻r1、第二电阻r2、第三电阻r3、第七电阻r7以及第八电阻r8;第一三极管q1的基极与集电极连接并接地,第二三极管q2的基极与集电极连接并接地,第一三极管q1的发射极与第二电阻r2的第一端连接,第二三极管q2的发射极与第一电阻r1的第一端连接;第一电阻r1的第二端与第三电阻r3的第一端连接,第三电阻r3的第二端与第二电阻r2的第二端以及第七电阻r7的第一端连接,第七电阻r7的第二端与第八电阻r8的第一端连接,第八电阻r8的第二端连接到电压缓冲器模块的电压输出点,第七电阻r7的第二端与第八电阻r8的第一端的公共连接点作为基准电压输出点。

4、本发明实施例中,所述高增益放大器模块包括第一放大器a1,第一放大器a1的正向输入端与第二电阻r2的第一端以及第一三极管q1的发射极连接,第一放大器a1的负向输入端与第一电阻r1的第二端以及第三电阻r3的第一端连接,第一放大器a1的输出端与所述电压缓冲器模块连接。

5、本发明实施例中,所述高阶温度补偿模块包括:第二放大器a2、第三三极管q3、第三pmos管mp3、第四pmos管mp4、第一电容c1、第四电阻r4、第五电阻r5以及第六电阻r6;第三三极管q3的基极与集电极连接并接地,第三三极管q3的发射极与第四pmos管mp4的漏极连接,并通过第四电阻r4连接到第一电阻r1与第三电阻r3之间的公共连接点,并通过第五电阻r5连接到第一三极管q1与第二电阻r2之间的公共连接点;第四pmos管mp4的源极与第三pmos管mp3的源极相连,并连接到电压缓冲器模块的电压输出点,第四pmos管mp4的栅极与第三pmos管mp3的基极连接,第三pmos管mp3的栅极与第二放大器a2的输出端连接并与第一电容c1的第一端连接,第三pmos管mp3的漏极与第一电容c1的第二端、第二放大器a2的正向输入端以及第六电阻r6的第一端连接,第二放大器a2的负向输入端连接到第七电阻r7与第八电阻r8之间的公共连接点,作为基准电压输出点vref,第六电阻r6的第二端接地。

6、本发明实施例中,所述电压缓冲器模块包括:第一nmos管mn1、第二nmos管mn2、第一pmos管mp1、第二pmos管mp2、第一电流源i1以及第二电流源i2;第一nmos管mn1的栅极连接vcas电压,第一nmos管mn1的漏极与第二pmos管mp2的栅极以及第一电流源i1的第一端连接,第一nmos管mn1的源极与第一pmos管mp1的漏极、第二nmos管mn2的栅极以及第二电流源i2的第一端连接;第二pmos管mp2的源极连接电源vcc,第一电流源i1的第二端连接电源vcc,第二电流源i2的第二端接地,第二nmos管mn2的源极接地,第二pmos管mp2的漏极与第一pmos管mp1的源极以及第二nmos管mn2的漏极连接的公共点作为电压缓冲器模块的电压输出点,第一pmos管mp1的栅极连接到第一放大器a1的输出端。

7、本发明实施例中,所述带隙基准电压模块包括:第一组双极型晶体管、第二组双极型晶体管、第一电阻r1、第二电阻r2、第三电阻r3以及第七电阻r7;第一组双极型晶体管的发射极和第二组双极型晶体管的发射极均接地,第一组双极型晶体管的集电极与第二电阻r2的第一端连接,第一组双极型晶体管的集电极与第一电阻r1的第一端连接;

8、第一电阻r1的第二端与第三电阻r3的第一端连接,第三电阻r3的第二端与第二电阻r2的第二端以及第七电阻r7的第一端连接,第七电阻r7的第二端连接到电压缓冲器模块的电压输出点。

9、本发明实施例中,所述高增益放大器模块包括第一放大器a1,第一放大器a1的正向输入端与第二电阻r2的第一端以及第一三极管q1的发射极连接,第一放大器a1的负向输入端与第一电阻r1的第二端以及第三电阻r3的第一端连接,第一放大器a1的输出端与所述电压缓冲器模块连接。

10、本发明实施例中,所述高阶温度补偿模块包括:第二放大器a2、第三组双极型晶体管、第三pmos管mp3、第四pmos管mp4、第一电容c1、第四电阻r4、第五电阻r5以及第六电阻r6;第三组双极型晶体管的发射极接地,第三组双极型晶体管的集电极与第四pmos管mp4的漏极连接,并通过第四电阻r4连接到第一电阻r1与第三电阻r3之间的公共连接点,并通过第五电阻r5连接到第一三极管q1与第二电阻r2之间的公共连接点;第四pmos管mp4的源极与第三pmos管mp3的源极相连,并连接到电压缓冲器模块的电压输出点,第四pmos管mp4的栅极与第三pmos管mp3的基极连接,第三pmos管mp3的栅极与第二放大器a2的输出端连接并与第一电容c1的第一端连接,第三pmos管mp3的漏极与第一电容c1的第二端、第二放大器a2的正向输入端以及第六电阻r6的第一端连接,第二放大器a2的负向输入端作为参考电压输出点vref,第六电阻r6的第二端接地。

11、本发明实施例中,所述电压缓冲器模块包括:第一nmos管mn1、第二nmos管mn2、第一pmos管mp1、第二pmos管mp2、第一电流源i1以及第二电流源i2;第一nmos管mn1的栅极连接vcas电压,第一nmos管mn1的漏极与第二pmos管mp2的栅极以及第一电流源i1的第一端连接,第一nmos管mn1的源极与第一pmos管mp1的漏极、第二nmos管mn2的栅极以及第二电流源i2的第一端连接;第二pmos管mp2的源极连接电源vcc,第一电流源i1的第二端连接电源vcc,第二电流源i2的第二端接地,第二nmos管mn2的源极接地,第二pmos管mp2的漏极与第一pmos管mp1的源极以及第二nmos管mn2的漏极连接的公共点作为电压缓冲器模块的电压输出点,第一pmos管mp1的栅极连接到第一放大器a1的输出端;所述电压缓冲器模块的电压输出点与第七电阻r7的第二端、第四pmos管mp4的源极、第三pmos管mp3的源极以及第二放大器a2的负向输入端连接的公共点作为参考电压输出点vref。

12、本发明还提供一种芯片,该芯片包括上述的基准电压产生电路。

13、本发明通过电压缓冲器模块为高增益放大器模块、带隙基准电压模块以及高阶温度补偿模块提供稳定的工作电压vreg,提升基准电压的电源抑制能力,通过带隙基准电压模块与高增益放大器模块、电压缓冲器模块产生一阶温度补偿的基准电压,通过高阶温度补偿模块消除基准电压的高阶温度项,从而生成具有低温度系数、高电源抑制特性的基准电压(参考电压)vref。

14、本发明技术方案的其它特征和优点将在下文的具体实施方式部分予以详细说明。

- 还没有人留言评论。精彩留言会获得点赞!