基于FPGA的PLC模块自适应组态测试方法与流程

本发明涉及生产测试,尤其涉及基于fpga的plc模块自适应组态测试方法。

背景技术:

1、在生产plc模块过程中,现有的方式占用大量的人力时间按照固有的顺序及事先准备好的pc上位机测试程序,排查模块好坏,效率低下。该技术利用fpga强大的并行数据处理能力,可同时处理多路模块数据,可自动随机的测试各plc模块的好坏,操作简便并可靠!

2、目前所用的plc测试程序,是运行在pc端的程序,执行的的是iec61499标准,目前大多数的iec61499功能块运行时是软件实现,并且在pc或者linux设备上运行,因此iec61499目前是一个典型的“软”控制器,iec61499运行时的实时性存在比较大的延时。

技术实现思路

1、本发明公开基于fpga的plc模块自适应组态测试方法,旨在解决背景技术中提出来的iec61499运行时的实时性存在比较大的延时的技术问题。

2、为了实现上述目的,本发明采用了如下技术方案:

3、基于fpga的plc模块自适应组态测试方法,包括uart协议、被测模块和测试程序,所述被测模块为plc模块,且被测模块包括di模块、do模块、ai模块和ao模块,测试方法具体包括以下步骤:

4、步骤一:自动检测组态模块:当连上所有被测的plc模块,fpga通过uart串口协议自动扫描所接入的plc模块型号类型,每个模块对应一个id节点,程序采用迭代自动寻址方式,每次扫描识别到最后模块并存储该模块id,暂时性排除该模块,下次迭代再识别出最后模块,多次迭代后,最终完成所有节点的自学习,即自动寻址到所有的模块id;

5、步骤二:自动启动测试程序:在所述步骤一完成的基础上,针对所搜索到的被测模块,完成的组态模型,fpga会进入测试程序执行程序,按照组态的顺序依次执行对应模块的测试程序。

6、在一个优选的方案中,所述uart协议是采用全双工通信模式,可同时收发数据,且plc模块是以id号进行区分的,在所述测试程序在执行中时,同时接收模块的返回数据包,自动检测输出与返回数据的匹配,实时输出检测结果,在所述测序程序执行过程中,涉及到数据的动态实时比对,实时数据的并行存储处理,所执行的测试程序是通过对iec61499的硬件实现。

7、在一个优选的方案中,所述fpga是一种控制芯片,且fpga的具体型号为xilinx的zynq7000,所述测试程序的软件端为简单的配置开关和交互信号,其他均由fpga硬件代码实现,全部为并行处理。

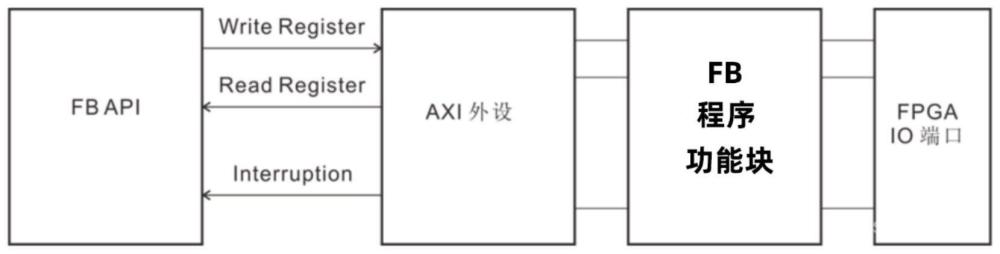

8、在一个优选的方案中,所述测试程序的操作过程包括有事件输入、事件输出和数据输入输出,所述事件输入:当需要向功能块注入事件时,运行时向输入事件寄存器对应的bit位置1,硬件fb检测输入事件寄存器的状态,一旦发现变化,转向事件处理,完成后,清除对应的状态位,所述事件输出:当功能块输出一个事件时,在输出事件寄存器相关位置1,并产生一个中断信号,由运行时软件读取事件寄存器,并且清零,所述数据输入/输出:当需要对数据操作时,调用data register读取数据后并通过api接口与模块进行数据交互。

9、由上可知,基于fpga的plc模块自适应组态测试方法,包括uart协议、被测模块和测试程序,所述被测模块为plc模块,且被测模块包括di模块、do模块、ai模块和ao模块,测试方法具体包括以下步骤:步骤一:自动检测组态模块:当连上所有被测的plc模块,fpga通过uart串口协议自动扫描所接入的plc模块型号类型,每个模块对应一个id节点,程序采用迭代自动寻址方式,每次扫描识别到最后模块并存储该模块id,暂时性排除该模块,下次迭代再识别出最后模块,多次迭代后,最终完成所有节点的自学习,即自动寻址到所有的模块id;步骤二:自动启动测试程序:在所述步骤一完成的基础上,针对所搜索到的被测模块,完成的组态模型,fpga会进入测试程序执行程序,按照组态的顺序依次执行对应模块的测试程序。本发明提供的基于fpga的plc模块自适应组态测试方法具有对生产的测试实际生产效率改进明显,原先要按照预设的模块组合方式组装,找到对应的测试程序准备,再启动运行对应匹配的测试程序,在一套测试准备阶段至少耗时半小时,新的测试系统对测试模块可随机组装,5分钟内完成测试准备及运行,效率提升80%以上。测试过程无需人工实时监控pc机状态,系统可自动输出测试结果数据的技术效果。

技术特征:

1.基于fpga的plc模块自适应组态测试方法,包括uart协议、被测模块和测试程序,其特征在于,所述被测模块为plc模块,且被测模块包括di模块、do模块、ai模块和ao模块,测试方法具体包括以下步骤:

2.根据权利要求1所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述uart协议是采用全双工通信模式,可同时收发数据,且plc模块是以id号进行区分的。

3.根据权利要求1所述的基于fpga的plc模块自适应组态测试方法,其特征在于,在所述测试程序在执行中时,同时接收模块的返回数据包,自动检测输出与返回数据的匹配,实时输出检测结果。

4.根据权利要求3所述的基于fpga的plc模块自适应组态测试方法,其特征在于,在所述测序程序执行过程中,涉及到数据的动态实时比对,实时数据的并行存储处理,所执行的测试程序是通过对iec61499的硬件实现。

5.根据权利要求1所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述fpga是一种控制芯片,且fpga的具体型号为xilinx的zynq7000。

6.根据权利要求5所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述测试程序的软件端为简单的配置开关和交互信号,其他均由fpga硬件代码实现,全部为并行处理。

7.根据权利要求1所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述测试程序的操作过程包括有事件输入、事件输出和数据输入输出,所述事件输入:当需要向功能块注入事件时,运行时向输入事件寄存器对应的bit位置1,硬件fb检测输入事件寄存器的状态,一旦发现变化,转向事件处理,完成后,清除对应的状态位。

8.根据权利要求7所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述事件输出:当功能块输出一个事件时,在输出事件寄存器相关位置1,并产生一个中断信号,由运行时软件读取事件寄存器,并且清零。

9.根据权利要求8所述的基于fpga的plc模块自适应组态测试方法,其特征在于,所述数据输入/输出:当需要对数据操作时,调用data register读取数据后并通过api接口与模块进行数据交互。

技术总结

本发明公开了基于FPGA的PLC模块自适应组态测试方法,包括UART协议、被测模块和测试程序,所述被测模块为PLC模块,且被测模块包括DI模块、DO模块、AI模块和AO模块,自动检测组态模块:当连上所有被测的PLC模块,FPGA通过UART串口协议自动扫描所接入的PLC模块型号类型,每个模块对应一个ID节点,程序采用迭代自动寻址方式,每次扫描识别到最后模块并存储该模块ID,暂时性排除该模块,下次迭代再识别出最后模块,多次迭代后,最终完成所有节点的自学习,即自动寻址到所有的模块ID。本发明公开的基于FPGA的PLC模块自适应组态测试方法具有对生产的测试实际生产效率改进明显,测试过程无需人工实时监控PC机状态,系统可自动输出测试结果数据的技术效果效果。

技术研发人员:林春惠,孟崴,王川,郑晓生

受保护的技术使用者:上海海得控制系统股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!