带隙基准源电路及原位背景校准方法与流程

本发明涉及集成电路,尤其涉及一种带隙基准源电路及原位背景校准方法。

背景技术:

1、带隙基准源(bandgap voltage reference)是模拟集成电路中用来产生稳定参考电压的基本构建模块。它的输出电压不仅要在温度变化下保持相对稳定,而且还要具有高的绝对精度,因为它会直接影响电路系统的性能。例如,在电压稳压器(voltageregulator)应用中,稳压器的输出电压由公式vreg=vbg*(1+α)决定,其中vbg是带隙基准源电压,α是一个比例常数。因此,vbg的电压精度直接决定了稳压器输出电压的精度。

2、图1为现有技术中一种带隙基准源电路。图1所示带隙基准源电路中,误差放大器a11输入失调电压导致节点vdp11以及节点vdn11之间的电压误差,电流镜失配误差导致电流i11、i12以及i13之间的电流误差等。

3、图2为现有技术中又一种带隙基准源电路。图2所示带隙基准源电路中,利用了三个斩波器ch21、ch22和ch23,通过斩波技术可以提高带隙基准源电压的精度,但它需要一个持续工作的时钟信号clk,会增加电路的功耗,其次,它会产生额外的噪声源,这会干扰电路系统中的其他模块。例如,时钟信号和斩波器的噪声会通过电源、地和带隙基准源电压输出传播。虽然可以在带隙基准源电压输出上加上滤波器来减小噪声,但是这会增加电路面积和启动时间。而且,并不能消除对电源和地的噪声干扰。另外,图2中尽管可以消除pmos管mp21和pmos管mp22之间的匹配误差,但并没有消除pmos管mp23与pmos管mp21、pmos管mp22之间的匹配误差,从而导致带隙基准源电压保留了一定的误差。

4、因此,有必要提供一种新型的带隙基准源电路及原位背景校准方法以解决现有技术中存在的上述问题。

技术实现思路

1、本发明的目的在于提供一种带隙基准源电路及原位背景校准方法,以减少带隙基准源电路输出的电压误差。

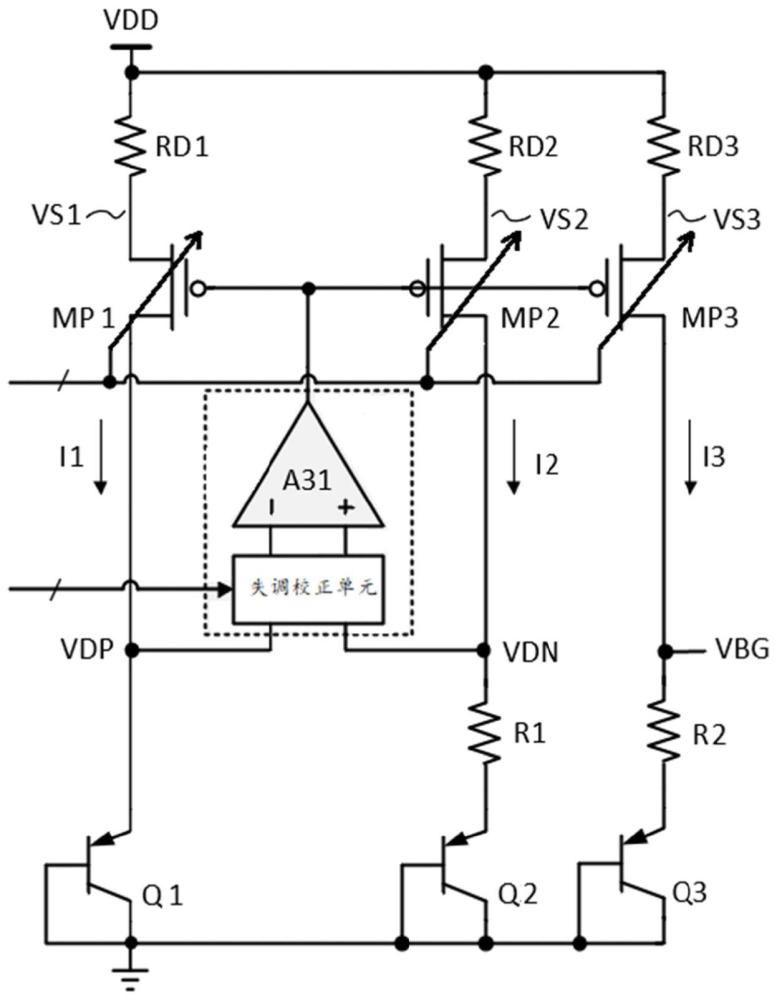

2、为实现上述目的,本发明的所述带隙基准源电路,包括第一pmos管、第二pmos管、第三pmos管、第一三极管、第二三极管、第三三极管、第一电阻、第二电阻、误差放大器、电阻单元、失调校正单元、电压比较单元和校正码调节单元,所述第一pmos管的源极、所述第二pmos管的源极和所述第三pmos管的源极均与所述电阻单元连接,所述第一pmos管的栅极与所述第二pmos管的栅极、所述第三pmos管的栅极和所述误差放大器的输出端连接,所述第一pmos管的漏极与所述第一三极管的发射极连接,所述第一三极管的基极和集电极均接地,所述第二pmos管的漏极与所述第一电阻的一端连接,所述第一电阻的另一端与所述第二三极管的发射极连接,所述第二三极管的基极和集电极均接地,所述第三pmos管的漏极与所述第二电阻的一端连接,所述第二电阻的另一端与所述第三三极管的发射极连接,所述第三三极管的基极和集电极均接地,所述失调校正单元用于调整所述第一pmos管的漏极电压以及所述第二pmos管的漏极电压,所述电压比较单元用于比较所述第一pmos管的源极端输入线上电压、所述第二pmos管的源极端输入线上电压和所述第三pmos管的源极端输入线上电压相互之间的大小,以及比较所述第一pmos管的漏极电压和所述第二pmos管的漏极电压的大小,所述校正码调节单元用于根据所述电压比较单元的比较结果调整所述电阻单元的电阻值或调整所述第二pmos管和所述第三pmos管的宽长比,所述校正码调节单元还用于根据所述电压比较单元的比较结果调整所述失调校正单元。

3、可选地,所述电阻单元包括第一退化电阻、第二退化电阻和第三退化电阻,所述第一退化电阻的一端、所述第二退化电阻的一端和所述第三退化电阻的一端均接电源电压,所述第一退化电阻的另一端与所述第一pmos管的源极连接,所述第二退化电阻的另一端与所述第二pmos管的源极连接,所述第三退化电阻的另一端与所述第三pmos管的源极连接。

4、可选地,所述电压比较单元包括多路复选电路和比较模块,所述多路复选电路的第一输入端与所述第一pmos管的源极连接,所述多路复选电路的第二输入端与所述第一pmos管的漏极连接,所述多路复选电路的第三输入端与第二pmos管的漏极连接,所述多路复选电路的第四输入端与所述第二pmos管的源极连接,所述多路复选电路的第五输入端与所述第三pmos管的源极连接,所述多路复选电路的第一输出端与所述比较模块的第一输入端连接,所述多路复选电路的第二输出端与所述比较模块的第二输入端连接。

5、可选地,所述校正码调节单元用于根据所述电压比较单元的比较结果调整所述第二pmos管和所述第三pmos管的宽长比,以及调整所述失调校正单元。

6、可选地,所述电阻单元包括第一退化电阻、第二退化电阻、第三退化电阻、第一可调退化电阻、第二可调退化电阻和第三可调退化电阻,所述第一退化电阻的一端、所述第二退化电阻的一端和所述第三退化电阻的一端均接电源电压,所述第一退化电阻的另一端与所述第一可调退化电阻的一端连接,所述第一可调退化电阻的另一端与所述第一pmos管的源极连接,所述第二退化电阻的另一端与所述第二可调退化电阻的一端连接,所述第二可调退化电阻的另一端与所述第二pmos管的源极连接,所述第三退化电阻的另一端与所述第三可调退化电阻的一端连接,所述第三可调退化电阻的另一端与所述第三pmos管的源极连接。

7、可选地,所述电压比较单元包括多路复选电路和比较模块,所述多路复选电路的第一输入端与所述第一退化电阻的另一端连接,所述多路复选电路的第二输入端与所述第一pmos管的漏极连接,所述多路复选电路的第三输入端与第二pmos管的漏极连接,所述多路复选电路的第四输入端与所述第二退化电阻的另一端连接,所述多路复选电路的第五输入端与所述第三退化电阻的另一端连接,所述多路复选电路的第一输出端与所述比较模块的第一输入端连接,所述多路复选电路的第二输出端与所述比较模块的第二输入端连接。

8、可选地,所述校正码调节单元用于根据所述电压比较单元的比较结果调整所述第一可调退化电阻的电阻值、所述第二可调退化电阻的电阻值、所述第三可调退化电阻的电阻值,以及调整所述失调校正单元。

9、可选地,所述比较模块为自动归零比较器。

10、本发明还提供了一种所述带隙基准源电路的原位背景校准方法,包括以下步骤:

11、s1:通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第二pmos管的源极端输入线上电压,以得到第一比较结果;

12、s2:使所述校正码调节单元根据所述第一比较结果调整所述电阻单元的电阻值或调整所述第二pmos管的宽长比,然后执行步骤s1,直至所述电压比较单元输出的第一比较结果发生翻转;

13、s3:通过所述电压比较单元比较所述第一pmos管的漏极电压和所述第二pmos管的漏极电压的大小,以得到第二比较结果;

14、s4:使所述校正码调节单元根据所述第二比较结果调整所述失调校正单元,然后执行步骤s3,直至所述电压比较单元输出的第二比较结果发生翻转;

15、s5:重复执行若干次步骤s1至步骤s4;

16、s6:通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第三pmos管的源极端输入线上电压,以得到第三比较结果;

17、s7:使所述校正码调节单元根据所述第三比较结果调整所述电阻单元的电阻值或调整所述第三pmos管的宽长比,然后执行步骤s6,直至所述电压比较单元输出的第三比较结果发生翻转。

18、可选地,所述电阻单元包括第一退化电阻、第二退化电阻和第三退化电阻,所述第一退化电阻的一端、所述第二退化电阻的一端和所述第三退化电阻的一端均接电源电压,所述第一退化电阻的另一端与所述第一pmos管的源极连接,所述第二退化电阻的另一端与所述第二pmos管的源极连接,所述第三退化电阻的另一端与所述第三pmos管的源极连接;

19、通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第二pmos管的源极端输入线上电压,包括:

20、通过所述电压比较单元比较所述第一pmos管的源极电压和所述第二pmos管的源极电压。

21、可选地,通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第三pmos管的源极端输入线上电压,包括:

22、通过所述电压比较单元比较所述第一pmos管的源极电压和所述第三pmos管的源极电压。

23、可选地,使所述校正码调节单元根据所述第一比较结果调整所述电阻单元的电阻值或调整所述第二pmos管的宽长比,包括:

24、使所述校正码调节单元根据所述第一比较结果调整所述第二pmos管的宽长比。

25、可选地,使所述校正码调节单元根据所述第三比较结果调整所述电阻单元的电阻值或调整所述第三pmos管的宽长比,包括:

26、使所述校正码调节单元根据所述第三比较结果调整所述第三pmos管的宽长比。

27、可选地,所述电阻单元包括第一退化电阻、第二退化电阻、第三退化电阻、第一可调退化电阻、第二可调退化电阻和第三可调退化电阻,所述第一退化电阻的一端、所述第二退化电阻的一端和所述第三退化电阻的一端均接电源电压,所述第一退化电阻的另一端与所述第一可调退化电阻的一端连接,所述第一可调退化电阻的另一端与所述第一pmos管的源极连接,所述第二退化电阻的另一端与所述第二可调退化电阻的一端连接,所述第二可调退化电阻的另一端与所述第二pmos管的源极连接,所述第三退化电阻的另一端与所述第三可调退化电阻的一端连接,所述第三可调退化电阻的另一端与所述第三pmos管的源极连接;

28、通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第二pmos管的源极端输入线上电压,包括:

29、通过所述电压比较单元比较所述第一可调退化电阻一端的电压和所述第二可调退化电阻一端的电压。

30、可选地,通过所述电压比较单元比较所述第一pmos管的源极端输入线上电压和所述第三pmos管的源极端输入线上电压,包括:

31、通过所述电压比较单元比较所述第一可调退化电阻一端的电压和所述第三可调退化电阻一端的电压。

32、可选地,使所述校正码调节单元根据所述第一比较结果调整所述电阻单元的电阻值或调整所述第二pmos管的宽长比,包括:

33、使所述校正码调节单元根据所述第一比较结果调整所述第二可调退化电阻的电阻值。

34、可选地,使所述校正码调节单元根据所述第三比较结果调整所述电阻单元的电阻值或调整所述第三pmos管的宽长比,包括:

35、使所述校正码调节单元根据所述第三比较结果调整所述第三可调退化电阻的电阻值。

36、本发明的有益效果在于:所述电压比较单元用于比较所述第一pmos管的源极端输入线上电压、所述第二pmos管的源极端输入线上电压和所述第三pmos管的源极端输入线上电压相互之间的大小,以及比较所述第一pmos管的漏极电压和所述第二pmos管的漏极电压的大小,所述校正码调节单元用于根据所述电压比较单元的比较结果调整所述电阻单元的电阻值或调整所述第二pmos管和所述第三pmos管的宽长比,所述校正码调节单元还用于根据所述电压比较单元的比较结果调整所述失调校正单元,减少了带隙基准源电路输出的电压误差。

- 还没有人留言评论。精彩留言会获得点赞!