一种快响应的无片外电容LDO电路

本技术涉及一种ldo电路,属于集成电路,具体是指一种快响应的无片外电容ldo电路。

背景技术:

1、随着电子产业的快速发展,集成电路的规模日益增加,片上系统已经变得无处不在。电源管理技术在电子行业发展中成为一大焦点,低压差线性稳压器(ldo)作为电源管理芯片中的一员,以其低成本、结构简单、低功耗以及低噪声的特点广泛应用于片上系统当中。

2、在传统的ldo电路中,输出端外接大电容不仅可以起到频率补偿的作用,还可作为电荷存储、泄放器件来减小输出电压的变化值,但外接大电容会提高应用的复杂度和成本,而且面积比较大,会使片上系统的集成度变差,这就使得无片外电容ldo的发展成为一种必然趋势。

3、然而,无片外电容ldo的主极点是在电路的内部,所以它只能通过功率管自身来进行瞬态响应。因此,无片外电容ldo普遍存在瞬态响应性能差,输出电压过冲大等问题。

技术实现思路

1、本实用新型的目的在于克服上述的缺点,提供一种快响应的无片外电容ldo电路,该电路具有快瞬态响应,高稳定性,功耗低,面积小等优点。

2、针对现有技术和上述不足之处,本实用新型采用以下设计方案来实现:

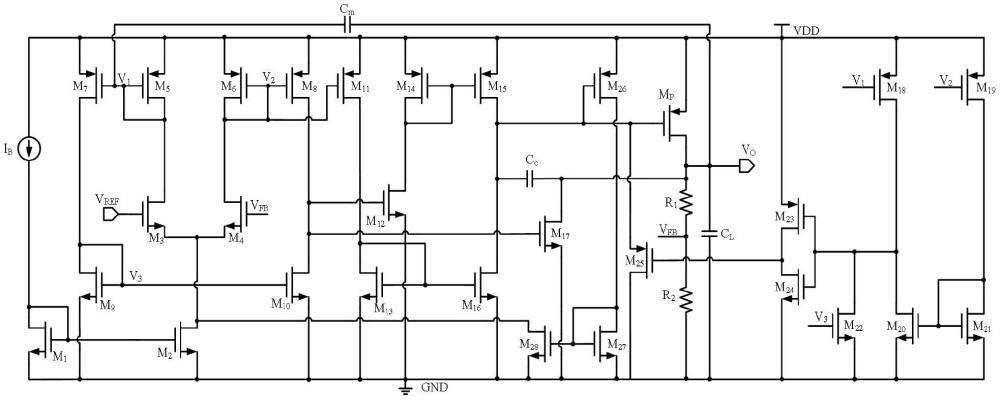

3、一种快响应的无片外电容ldo电路,包括跨导运算放大器、第二级放大器、自适应偏置电路、下冲抑制电路和电压输出模块;所述的跨导运算放大器用于比较反馈电压和参考电压,并产生控制电压输出模块中pmos功率管的输出;所述的第二级放大器用于进一步放大跨导运算放大器的输出,从而使电压输出模块中pmos功率管的输出更稳定;所述的自适应偏置电路用于采样pmos功率管的输出电流,并通过电流镜的形式把采样到的电流传递给误差放大器,从而提高电路的瞬态响应性能;所述的下冲抑制电路用于为pmos功率管提供栅极到地信号端的放电通路,从而降低电路输出的下冲电压,提高瞬态响应能力;所述的电压输出模块用于根据第二级放大器的输出来控制pmos功率管,pmos功率管的漏极作为ldo电路的输出,并通过反馈电阻网络把输出电压反馈到跨导运算放大器的另一个输入端。

4、进一步的是,所述的跨导运算放大器包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管;所述的第一晶体管、第二晶体管、第九晶体管、第十晶体管的源极都接地信号端;所述的第五晶体管、第六晶体管、第七晶体管、第八晶体管的源极都接电源电压端;所述的第一晶体管的漏极与偏置电流源ib相连,同时第一晶体管的漏极与栅极互连,并与所述的第二晶体管的栅极相连;所述的第二晶体管的漏极分别与所述的第三晶体管、第四晶体管的源极相连;所述的第三晶体管的栅极与参考电压端相连,漏极与所述的第五晶体管的漏极相连;所述的第四晶体管的栅极通过第二电阻r2接地信号端,漏极与所述的第六晶体管的漏极相连;所述的第五晶体管的漏极与栅极互连,并与所述的第七晶体管的栅极相连;所述的第六晶体管的漏极与栅极互连,并与所述的第八晶体管的栅极相连;所述的第七晶体管的漏极与所述的第九晶体管的漏极相连;所述的第八晶体管的漏极与所述的第十晶体管的漏极相连;所述的第九晶体管的漏极与栅极互连,并与所述的第十晶体管的栅极相连;所述的第十晶体管的漏极与所述的第十二晶体管、第十七晶体管的栅极相连。

5、进一步的是,所述的第二级放大器包括第十一晶体管、第十二晶体管、第十三晶体管、第十四晶体管、第十五晶体管、第十六晶体管;所述的第十二晶体管、第十三晶体管、第十六晶体管的源极都接地信号端;所述的第十一晶体管、第十四晶体管、第十五晶体管的源极都接电源电压端;所述的第十一晶体管的栅极与所述的第六晶体管、第八晶体管的栅极相连,漏极与所述的第十三晶体管的漏极相连;所述的第十二晶体管的漏极与所述的第十四晶体管的漏极相连;所述的第十三晶体管的漏极与栅极互连,并与所述的第十六晶体管的栅极相连;所述的第十四晶体管的漏极与栅极互连,并与所述的第十五晶体管的栅极相连;所述的第十五晶体管的漏极与所述的第十六晶体管的漏极相连;所述的第十六晶体管的漏极与所述的第二十六晶体管、pmos功率管的栅极相连接,并与第一电容cc的一端相连。

6、进一步的是,所述的自适应偏置电路包括第二十六晶体管、第二十七晶体管、第二十八晶体管;所述的第二十七晶体管、第二十八晶体管的源极与地信号端相连;所述的第二十六晶体管的源极与电源电压端相连,栅极与所述的pmos功率管的栅极相连,漏极与所述的第二十七晶体管的漏极相连;所述的第二十七晶体管的漏极与栅极互连,并与所述的第二十八晶体管的栅极相连;所述的第二十八晶体管的漏极与所述的第二晶体管的漏极相连。

7、进一步的是,所述的下冲抑制电路包括第十八晶体管、第十九晶体管、第二十晶体管、第二十一晶体管、第二十二晶体管、第二十三晶体管、第二十四晶体管、第二十五晶体管;所述的第二十晶体管、第二十一晶体管、第二十二晶体管、第二十四晶体管的源极都与地信号端相连;所述的第十八晶体管、第十九晶体管、第二十三晶体管的源极都与电源电压端相连;所述的第十八晶体管的栅极与所述的第五晶体管、第七晶体管的栅极相连,漏极与所述的第二十晶体管的漏极相连;所述的第十九晶体管的栅极与所述的第六晶体管、第八晶体管的栅极相连,漏极与所述的第二十一晶体管的漏极相连;所述的第二十晶体管的栅极与所述的第二十一晶体管的栅极相连,漏极与所述的第二十二晶体管的漏极相连;所述的第二十一晶体管的漏极与栅极互连;所述的第二十二晶体管的栅极与所述的第九晶体管、第十晶体管的栅极相连,漏极与所述的第二十三晶体管、第二十四晶体管的栅极相连;所述的第二十三晶体管的漏极与所述的第二十四晶体管的漏极相连,栅极与所述的第二十四晶体管的栅极相连;所述的第二十四晶体管的漏极与所述的第二十五晶体管的栅极相连;所述的第二十五晶体管的源极与pmos功率管的栅极相连,漏极与地信号端相连。

8、进一步的是,所述的电压输出模块包括第十七晶体管、pmos功率管、第一电容cc、第二电容cm、第一电阻r1和第二电阻r2;所述的第十七晶体管的栅极与所述的第十二晶体管的栅极,漏极与第一电容cc的另一端相连,源极与地信号端相连;所述的pmos功率管的栅极与所述的第十五晶体管的漏极相连,源极与电源电压端相连,漏极作为输出端与第一电阻r1的一端相连,并与所述的第十七晶体管的漏极相连;所述的第一电阻r1和第二电阻r2串联,它们的连接端处与第四晶体管m4的栅极相连。

9、本实用新型具有以下优点:第一,本实用新型采用了自适应偏置电路,在不增加额外的功耗情况下增大了电路的带宽,并降低了电路的上冲、下冲电压;第二,本实用新型采用了有源前馈频率补偿结构和米勒电容补偿结构,在无片外电容的情况下,能很好的保持电路的稳定性;第三,本实用新型提出了一种下冲抑制结构,当输出从轻载向重载突变时,能显著减小下冲电压,提高ldo的瞬态响应性能。

技术特征:

1.一种快响应的无片外电容ldo电路,其特征在于包括跨导运算放大器、第二级放大器、自适应偏置电路、下冲抑制电路和电压输出模块;跨导运算放大器用于比较反馈电压和参考电压,并产生控制电压输出模块中pmos功率管的输出;第二级放大器用于进一步放大跨导运算放大器的输出,从而使电压输出模块中pmos功率管的输出更稳定;自适应偏置电路用于采样pmos功率管的输出电流,并通过电流镜的形式把采样到的电流传递给误差放大器,从而提高电路的瞬态响应性能;下冲抑制电路用于为pmos功率管提供栅极到地信号端的放电通路,从而降低电路输出的下冲电压,提高瞬态响应能力;电压输出模块用于根据第二级放大器的输出来控制pmos功率管,pmos功率管的漏极作为ldo电路的输出,并通过反馈电阻网络把输出电压反馈到跨导运算放大器的另一个输入端。

2.根据权利要求1所述的一种快响应的无片外电容ldo电路,其特征在于:所述的跨导运算放大器包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10;第一晶体管m1、第二晶体管m2、第九晶体管m9、第十晶体管m10的源极都接地信号端gnd;第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8的源极都接电源电压端vdd;第一晶体管m1的漏极与偏置电流源ib相连,同时漏极与栅极互连,并与第二晶体管m2的栅极相连;第二晶体管m2的漏极分别与第三晶体管m3、第四晶体管m4的源极相连;第三晶体管m3的栅极与参考电压端vref相连,漏极与第五晶体管m5的漏极相连;第四晶体管m4的栅极通过第二电阻r2接地信号端gnd,漏极与第六晶体管m6的漏极相连;第五晶体管m5的漏极与栅极互连,并与第七晶体管m7的栅极相连;第六晶体管m6的漏极与栅极互连,并与第八晶体管m8的栅极相连;第七晶体管m7的漏极与第九晶体管m9的漏极相连;第八晶体管m8的漏极与第十晶体管m10的漏极相连;第九晶体管m9的漏极与栅极互连,并与第十晶体管m10的栅极相连;第十晶体管m10的漏极与第十二晶体管m12、第十七晶体管m17的栅极相连。

3.根据权利要求1所述的一种快响应的无片外电容ldo电路,其特征在于:所述的第二级放大器包括第十一晶体管m11、第十二晶体管m12、第十三晶体管m13、第十四晶体管m14、第十五晶体管m15、第十六晶体管m16;第十二晶体管m12、第十三晶体管m13、第十六晶体管m16的源极都接地信号端gnd;第十一晶体管m11、第十四晶体管m14、第十五晶体管m15的源极都接电源电压端vdd;第十一晶体管m11的栅极与第六晶体管m6、第八晶体管m8的栅极相连,漏极与第十三晶体管m13的漏极相连;第十二晶体管m12的漏极与第十四晶体管m14的漏极相连;第十三晶体管m13的漏极与栅极互连,并与第十六晶体管m16的栅极相连;第十四晶体管m14的漏极与栅极互连,并与第十五晶体管m15的栅极相连;第十五晶体管m15的漏极与第十六晶体管m16的漏极相连;第十六晶体管m16的漏极与第二十六晶体管m26、pmos功率管mp的栅极相连接,并与第一电容cc的一端相连。

4.根据权利要求1所述的一种快响应的无片外电容ldo电路,其特征在于:所述的自适应偏置电路包括第二十六晶体管m26、第二十七晶体管m27、第二十八晶体管m28;第二十七晶体管m27、第二十八晶体管m28的源极与地信号端gnd相连;第二十六晶体管m26的源极与电源电压端vdd相连,栅极与pmos功率管mp的栅极相连,漏极与第二十七晶体管m27的漏极相连;第二十七晶体管m27的漏极与栅极互连,并与第二十八晶体管m28的栅极相连;第二十八晶体管m28的漏极与所述跨导运算放大器中的第二晶体管m2的漏极相连。

5.根据权利要求1所述的一种快响应的无片外电容ldo电路,其特征在于:所述的下冲抑制电路包括第十八晶体管m18、第十九晶体管m19、第二十晶体管m20、第二十一晶体管m21、第二十二晶体管m22、第二十三晶体管m23、第二十四晶体管m24、第二十五晶体管m25;第二十晶体管m20、第二十一晶体管m21、第二十二晶体管m22、第二十四晶体管m24的源极都与地信号端gnd相连;第十八晶体管m18、第十九晶体管m19、第二十三晶体管m23的源极都与电源电压端vdd相连;第十八晶体管m18的栅极与第五晶体管m5、第七晶体管m7的栅极相连,漏极与第二十晶体管m20的漏极相连;第十九晶体管m19的栅极与第六晶体管m6、第八晶体管m8的栅极相连,漏极与第二十一晶体管m21的漏极相连;第二十晶体管m20的栅极与第二十一晶体管m21的栅极相连,漏极与第二十二晶体管m22的漏极相连;第二十一晶体管m21的漏极与栅极互连;第二十二晶体管m22的栅极与第九晶体管m9、第十晶体管m10的栅极相连,漏极与第二十三晶体管m23、第二十四晶体管m24的栅极相连;第二十三晶体管m23的漏极与第二十四晶体管m24的漏极相连,栅极与第二十四晶体管m24的栅极相连;第二十四晶体管m24的漏极与第二十五晶体管m25的栅极相连;第二十五晶体管m25的源极与pmos功率管mp的栅极相连,漏极与地信号端gnd相连。

6.根据权利要求1所述的一种快响应的无片外电容ldo电路,其特征在于:所述的电压输出模块包括第十七晶体管m17、pmos功率管mp、第一电容cc、第二电容cm、第一电阻r1和第二电阻r2;第十七晶体管m17的栅极与第十二晶体管m12的栅极,漏极与第一电容cc的另一端相连,源极与地信号端gnd相连;pmos功率管mp的栅极与第十五晶体管m15的漏极相连,源极与电源电压端vdd相连,漏极作为输出端与第一电阻r1的一端相连,并与第十七晶体管m17的漏极相连;第一电阻r1和第二电阻r2串联,它们的连接端处与第四晶体管m4的栅极相连。

技术总结

本技术公开了一种快响应的无片外电容LDO电路,由跨导运算放大器、第二级放大器、自适应偏置电路、下冲抑制电路和电压输出模块组成。该电路采用自适应偏置电路结构,在不增加额外的功耗情况下增大了电路的带宽,提高了电路的瞬态响应性能;同时,本技术采用了有源前馈频率补偿结构和米勒电容补偿结构,在无片外电容的情况下,能很好的保持电路的稳定性;此外,本技术提出了一种下冲抑制结构,当输出从轻载向重载突变时,能显著减小下冲电压,提高LDO的瞬态响应性能。

技术研发人员:段吉海,麦峻玮,李冀

受保护的技术使用者:桂林电子科技大学

技术研发日:20230828

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!