测试存取端口电路的制作方法

[0001]

本发明涉及一种测试存取端口(test access port,tap)电路,特别是涉及一种能够提升传输流通量(throughput)的测试存取端口电路。

背景技术:

[0002]

在现有技术中,联合测试工作组(joint test action group,jtag)是以序列的方式传输信息,联合测试工作组的接口主要包含数据输入端、数据输出端、重置端、频率信号端及模式选择端。一般来说,为了能够以联合测试工作组的接口来传输测试数据,系统会在待测装置上安装测试存取端口(test access port,tap)电路,测试存取端口可以通过联合测试工作组所规范的接口来控制内部的缓存器,以获取或输出待测装置的数据来进行测试及侦错。

[0003]

由于测试存取端口电路是以序列(serial)的方式通过数据输出端来输出数据位,并通过数据输入端来接收数据,因此一次仅能输出或输入一个位的数据,传输速率甚低。在现有技术中,若欲加快系统传输数据的速度,就必须通过其他的接口来实现,而需额外增加硬件,整体测试系统的弹性并不高。

技术实现要素:

[0004]

本发明的一实施例揭露一种测试存取端口(test access port,tap)电路。测试存取端口电路包含数据输入端、数据输出端、重置端、模式选择端、至少一测试数据缓存器组、辅助数据缓存器组、指令缓存器组及控制器。

[0005]

控制器耦接于模式选择端及指令缓存器组。控制器根据模式选择端所接收的至少一模式选择信号控制至少一测试数据缓存器组、辅助数据缓存器组,及指令缓存器组。

[0006]

在重置端输入模式下,当控制器控制第一测试数据缓存器组储存数据输入端所接收的第一输入数据位时,辅助数据缓存器组储存重置端所接收的第二输入数据位。

[0007]

本发明的另一实施例揭露一种测试存取端口电路。测试存取端口电路包含数据输入端、数据输出端、重置端、模式选择端、至少一测试数据缓存器组、辅助数据缓存器组、指令缓存器组及控制器。

[0008]

控制器耦接于模式选择端及指令缓存器组。控制器根据模式选择端所接收的至少一模式选择信号控制至少一测试数据缓存器组、辅助数据缓存器组,及指令缓存器组。

[0009]

在数据输入端输入模式下,控制器控制测试数据缓存器组自数据输入端接收第一输入数据位,而在数据输入端输出模式下,当控制器控制第一测试数据缓存器组自数据输出端输出第一输出数据位时,第一辅助数据缓存器组自数据输入端输出第二输出数据位。

[0010]

本发明的另一实施例揭露一种测试存取端口电路。测试存取端口电路包含数据输入端、数据输出端、重置端、模式选择端、至少一测试数据缓存器组、辅助数据缓存器组、指令缓存器组及控制器。

[0011]

控制器耦接于模式选择端及指令缓存器组。控制器根据模式选择端所接收的至少

一模式选择信号控制至少一测试数据缓存器组、辅助数据缓存器组,及指令缓存器组。

[0012]

在数据输出端输出模式下,控制器控制一测试数据缓存器组自数据输出端输出第一输出数据位,而在数据输出端输入模式下,当控制器控制第一测试数据缓存器组自数据输入端接收第一输入数据位时,第一辅助数据缓存器组自数据输出端接收第二输入数据位。

附图说明

[0013]

图1是本发明一实施例的测试存取端口电路的示意图。

[0014]

图2是本发明另一实施例的测试存取端口电路的示意图。

[0015]

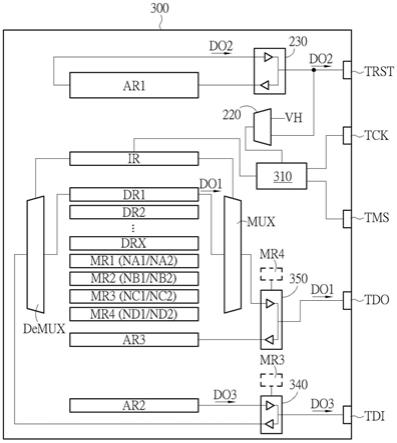

图3是本发明另一实施例的测试存取端口电路的示意图。

[0016]

图4是图3的测试存取端口电路在数据输出端输入模式下的示意图。

具体实施方式

[0017]

图1是本发明一实施例的测试存取端口(test access port,tap)电路100的示意图。测试存取端口电路100可以应用于联合测试工作组(joint test action group,jtag)中,并与系统中待测的电路或装置(例如:待写入的内存系统)相耦接以获取或输出待测电路或装置的数据来进行测试及侦错。

[0018]

在图1中,测试存取端口电路100包含数据输入端tdi、数据输出端tdo、频率信号端tck、重置端trst、模式选择端tms、多个测试数据缓存器组dr1至drx、辅助数据缓存器组ar1、指令缓存器组ir及控制器110,其中x为正整数。

[0019]

控制器110耦接于频率信号端tck、模式选择端tms及指令缓存器组ir,控制器110可以根据频率信号端tck所接收的多个频率信号判读模式选择端tms所接收的多个模式选择信号,并可根据模式选择信号控制测试数据缓存器组dr1至drx、辅助数据缓存器组ar1,及指令缓存器组ir。在有些实施例中,测试数据缓存器组dr1至drx、辅助数据缓存器组ar1及指令缓存器组ir可各包含多个串接的移位寄存器,因此控制器110可以通过移位操作来对测试数据缓存器组dr1至drx、辅助数据缓存器组ar1及指令缓存器组ir进行写入及输出。

[0020]

在一般应用于联合测试工作组的测试存取端口电路中,控制器110中可包含有限状态机(finite state machine,fsm),有限状态机可以包含多个预设的状态,并且可以根据模式选择信号在不同的状态中切换来控制。有限状态机中的预设状态一般会包含重置、闲置、设定指令缓存器组及设定测试数据缓存器等状态。在此情况下,控制器110可以先通过对指令缓存器组ir进行获取(captrue)及移位(shift)等操作来写入不同的数值以选取对应的测试数据缓存器组。例如在图1中,解多任务器demux及多任务器mux即可根据指令缓存器组ir中所储存的数值来导通对应的路径。接着便可对对应的测试数据缓存器组进行获取或移位等操作。举例来说,若测试数据缓存器组dr1至drx及辅助数据缓存器组ar1总共有32个缓存器组,则指令缓存器组ir则可包含5个位来表示32个不同的数值,并可分别对应到不同的缓存器组,然而本发明并不以此为限,在本发明的其他实施例中,指令缓存器组ir中也可根据系统的需求而包含更多或更少数量的缓存器。

[0021]

在现有技术中,测试存取端口电路100是通过数据输入端tdi来接收数据,并通过数据输出端tdo来输出数据位,由于一次只能输入或输出一个位的数据,因此传输的流通量

较小。此外,在有些实施例中,由于通过连续传送高电位的模式选择信号也可以达到重置控制器110的效果,因此在联合测试工作组的通信过程中,也可以协议好不再通过重置端trst来传送重置信号,而只通过模式选择信号来进行重置。在此情况下,测试存取端口电路100除了可以通过数据输入端tdi来接收数据之外,还可以通过重置端trst来接收数据,达到提升传输流通量的效果。

[0022]

举例来说,在重置端输入模式下,当控制器110控制测试数据缓存器组dr1储存数据输入端tdi所接收的输入数据位di1时,辅助数据缓存器组ar1也可以同时或依序储存重置端trst所接收的第二输入数据位di2。也就是说,当控制器100通过指令缓存器组ir选取了测试数据缓存器组dr1来接收数据输入端tdi所接收到的数据时,辅助数据缓存器组ar1也可以同步接收重置端trst所接收到的数据,因此控制器110接收数据的输入流通量就可以提升为两倍。也就是说,测试存取端口电路100可以默认测试数据缓存器组dr1与辅助数据缓存器组ar1之间的关联性,并对两者平行(parallel)进行写入。

[0023]

在有些实施例中,测试数据缓存器组dr1及辅助数据缓存器组ar1可具有相同大小的储存空间,例如包含相同数量的移位寄存器,因此两者可以同步地接收应用于联合测试工作组的主控端所传来的数据,并且同步完成移位输入。然而,在有些其他实施例中,测试数据缓存器组dr1及辅助数据缓存器组ar1也可能具有相异大小的储存空间,例如辅助数据缓存器组ar1的储存空间可能小于测试数据缓存器组dr1的储存空间,则测试存取端口电路100便可能需要增加其他的逻辑电路,使得联合测试工作组的主控端可以在辅助数据缓存器组ar1已填满而测试数据缓存器组dr1尚未填满的情况下,终止对辅助数据缓存器组ar1进行移位输入的操作。在一实施例中,控制器110可以将有效的数据位存放在相同宽度数据的最低有效位(least significant bit,lsb)端,假设从最高有效位(most significant bit,msb)开始传输,则最终在辅助数据缓存器中的数据即所需长度的数据,多余的位因为先进入缓存器,最后都已被移位输出(shift-out),因此不会影响辅助数据的接收。

[0024]

图2是本发明一实施例的测试存取端口电路200的示意图。测试存取端口电路200与测试存取端口电路100具有相似的结构并且可以根据相似的原理操作,然而,测试存取端口电路200还可支持外部重置模式及重置端输出模式,也就是说,测试存取端口电路200保留了通过重置端trst接收重置信号来对控制器210进行重置的功能,并且还可以通过重置端trst进行输入及输出。

[0025]

在图2中,测试存取端口电路200可包含路径选择电路220及模式缓存器组mr1。路径选择电路220具有第一输入端、第二输入端、输出端及控制端,路径选择电路220的第一输入端耦接于重置端trst,路径选择电路220的第二输入端可接收默认电压vh,路径选择电路220的输出端可输出重置信号sig

rst

或默认电压vh至控制器210。在有些实施例中,路径选择电路220可例如以多任务器来实作。模式缓存器组mr1可耦接于路径选择电路220的控制端。在有些实施例中,若重置信号sig

rst

是以低电压来触发控制器210的重置事件,则默认电压vh可设定为高电压(例如图2中,默认电压vh为逻辑1的高电压),以免重置控制器210。然而,测试存取端口电路200在模式选择端tms连续接收高电位的模式选择信号之后,控制器210仍然会执行重置操作。

[0026]

在有些实施例中,联合测试工作组的主控端可以输入一系列的模式选择信号,使得控制器210中的有限状态机通过在指令缓存器组ir中写入对应的数值来选取模式缓存器

组mr1,并在模式缓存器组mr1中写入数值na1,例如但不限于0,将使路径选择电路220在其第一输入端(即重置端trst)及输出端之间建立电性连接,如此一来,测试存取端口电路200便可进入外部重置模式,而可经由重置端trst接收外部传来的重置信号sig

rst

。此外,若控制器210在选取模式缓存器组mr1后,在模式缓存器组mr1中写入数值na2,例如但不限于1,则将使路径选择电路220在其第二输入端(即默认电压vh)及输出端之间建立电性连接,使得控制器210将持续地接收到高电压的信号而不会被重置端trst的电压影响而被误重置,测试存取端口电路200便会进入重置端输入模式或重置端输出模式。

[0027]

在图2的实施例中,测试存取端口电路200除了可以通过重置端trst来接收数据之外,也可以通过重置端trst来输出数据。举例来说,在重置端输出模式下,当控制器210控制测试数据缓存器组dr1自数据输出端tdo输出输出数据位do1时,辅助数据缓存器组ar1也可同时或依序自重置端trst输出输出数据位do2。如此一来,就可以提升测试存取端口电路200中的输出流通量。

[0028]

为了同时支持重置端输出模式及重置端输入模式,测试存取端口电路200还可包含双向信号选择电路230及模式缓存器组mr2。双向信号选择电路230可耦接于辅助数据缓存器组ar1及重置端trst,而模式缓存器组mr2可耦接于双向信号选择电路230。

[0029]

在此情况下,控制器210可以通过指令缓存器组ir选取模式缓存器组mr2,并在模式缓存器组mr2中写入数值nb1,使得测试存取端口电路200进入重置端输入模式,并可控制双向信号选择电路230自重置端trst接收输入数据位di2(图2中未示)。相对地,当控制器210在模式缓存器组mr2中写入不同于数值nb1的数值nb2时,测试存取端口电路200便可进入重置端输出模式,而双向信号选择电路230则会自重置端trst输出输出数据位do2。

[0030]

由于测试存取端口电路200可以通过指令缓存器组ir来控制新增设的模式缓存器组mr1及mr2,并据以控制内部的信号路径,因此可以在不改变控制器210中有限状态机既有状态的情况下,使得测试存取端口电路200能够支持重置端输出模式、重置端输入模式及外部重置模式。也就是说,测试存取端口电路200的控制器210可以使用与现有技术相同的有限状态机,却能够提升输出及输入的流通量。

[0031]

图3是本发明一实施例的测试存取端口电路300的示意图。测试存取端口电路300与测试存取端口电路200具有相似的结构并且可以根据相似的原理操作,然而,测试存取端口电路300还可支持输入端输出模式及输出端输入模式,也就是说,测试存取端口电路300除了可以通过重置端进行输入及输出之外,还可以通过数据输入端tdi进行输出,并且可以通过数据输出端tdo来进行输入,因此还可以进一步提升输出及输出的流通量。

[0032]

在图3中,测试存取端口电路300可包含辅助数据缓存器组ar2。在数据输入端输入模式下,数据输入端tdi可用来接收数据,而控制器310可选择测试数据缓存器组dr1至drx中的一测试数据缓存器组来储存自数据输入端tdi接收的输入数据位。相对地,在数据输入端输出模式下,数据输入端tdi则可用来输出数据,例如当控制器310控制测试数据缓存器组dr1自数据输出端tdo输出输出数据位do1时,辅助数据缓存器ar2则可同时或依序自数据输入端tdi输出输出数据位do3。也就是说,测试存取端口电路300可以默认测试数据缓存器组dr1与辅助数据缓存器组ar2之间的关联性,并对两者平行进行输出。如此一来,就可以同步通过数据输出端tdo来输出测试数据缓存器组dr1中的数据位并通过数据输入端tdi来输出辅助数据缓存器组ar2中的数据位,达到提升输出流通量的效果。

[0033]

在有些实施例中,重置端输出模式及数据输入端输出模式可以同时启动,在此情况下,测试存取端口电路300就可以同时通过数据输出端tdo、重置端trst及数据输入端tdi分别用来输出测试数据缓存器组dr1、辅助数据缓存器组ar1及ar2中的输出数据位do1、do2及do3,使得输出流通量能够提高到现有技术的三倍。

[0034]

然而,本发明并不限定测试数据缓存器组dr1与辅助数据缓存器组ar2之间的关联性,在有些实施例中,测试存取端口电路300也可以默认其他测试数据缓存器组,例如测试数据缓存器组dr2与辅助数据缓存器组ar2之间的关联性,此时,在数据输入端输出模式下,当控制器310选择由测试数据缓存器组dr2自数据输出端tdo输出输出数据位时,辅助数据缓存器ar2则可同时或依序自数据输入端tdi输出输出数据位。

[0035]

在图3中,测试存取端口电路300还可包含双向信号选择电路340及模式缓存器组mr3。双向信号选择电路340可耦接于辅助数据缓存器组ar2及数据输入端tdi,而模式缓存器组mr3可耦接于双向信号选择电路340。在有些实施例中,控制器310可以在模式缓存器组mr3中写入数值nc1以控制双向信号选择电路340自数据输入端tdi接收输入数据位,此时测试存取端口电路300即进入数据输入端输入模式。相对地,若控制器310在模式缓存器组mr3中写入不同于数值nc1的数值nc2,则可以控制双向信号选择电路340自数据输入端tdi输出数据,例如输出辅助数据缓存器组ar2中的输出数据位do3,此时测试存取端口电路300即进入数据输入端输出模式。

[0036]

此外,测试存取端口电路300还可通过数据输出端来接收数据。图4是测试存取端口电路300在数据输出端输入模式下的示意图。测试存取端口电路300包含辅助数据缓存器组ar3。在数据输出端输出模式下,数据输出端tdo可用来输出数据,而控制器310可以选择测试数据缓存器组dr1至drx中的一测试数据缓存器组,并自数据输出端tdo输出储存在该测试数据缓存器组中的数据位。相对地,在图4所示的数据输出端输入模式下,数据输出端tdo则可用来接收数据。举例来说,当控制器310控制测试数据缓存器组dr1自数据输入端tdi接收输入数据位di1时,辅助数据缓存器组ar3同时或依序可自数据输出端tdo接收输入数据位di3。也就是说,测试存取端口电路300可以默认测试数据缓存器组dr1与辅助数据缓存器组ar3之间的关联性,并使两者平行接收并储存数据。如此一来,就可以同时通过数据输入端tdi来接收数据并储存至测试数据缓存器组dr1中,并通过数据输出端tdo来接收数据并储存至辅助数据缓存器组ar3中,达到提升输入流通量的效果。

[0037]

在有些实施例中,重置端输入模式及数据输出端输入模式可以同时启动,在此情况下,测试存取端口电路300就可以同时通过数据输入端tdi、重置端trst及数据输出端tdo来接收输入数据位di1、di2及di3并分别储存至测试数据缓存器组dr1、辅助数据缓存器组ar1及ar3中,使得输入流通量能够提高到现有技术的三倍。

[0038]

然而,本发明并不限定测试数据缓存器组dr1与辅助数据缓存器组ar3之间的关联性,在有些实施例中,测试存取端口电路300也可以默认其他测试数据缓存器组,例如测试数据缓存器组dr2与辅助数据缓存器组ar3之间的关联性,此时,在数据输出端输入模式下,当控制器310选择由测试数据缓存器组dr2储存自数据输入端tdi所接收的输入数据位时,辅助数据缓存器ar3则可同时或依序储存自数据输出端tdo所接收的输入数据位。

[0039]

在图4中,测试存取端口电路300还可包含双向信号选择电路350及模式缓存器组mr4。双向信号选择电路350耦接于辅助数据缓存器组ar3及数据输出端tdo,模式缓存器组

mr4可耦接于双向信号选择电路350。在有些实施例中,控制器310可以在模式缓存器组mr4中写入数值nd1以控制双向信号选择电路350自数据输出端tdo输出输出数据位,并使测试存取端口电路300进入数据输出端输出模式。相对地,若控制器310在模式缓存器组mr4中写入不同于数值nd1的数值nd2,则可以控制双向信号选择电路350自数据输出端tdo接收输入数据位,例如输入数据位di3,此时测试存取端口电路300即进入数据输出端输入模式。

[0040]

在有些实施例中,测试存取端口电路300可以通过重置端trst、数据输入端tdi及数据输出端tdo来接收或输出数据,因此可以进一步提升输入流通量及输出流通量,然而在有些实施例中,测试存取端口电路也可能根据系统的需求,而只支持数据输入端输出模式而不支持重置端输入模式、重置端输出模式及/或数据输出端输入模式,或是只支持数据输出端输入模式而不支持重置端输入模式、重置端输出模式及/或数据输入端输出模式。也就是说,设计者可以根据实际电路的需求,将测试存取端口电路300中的辅助数据缓存器组ar1、ar2及ar3中的任一者或任两者省略,并将其对应的双向信号选择电路及模式缓存器组省略,而仅保留需要的辅助数据缓存器及对应的双向信号选择电路及模式缓存器组。

[0041]

综上所述,本发明的实施例所提供的测试存取端口电路可以平行通过重置端、数据输入端及数据输出端来接收或输出数据,因此可以提升输入及输出的流通量。此外,由于本发明的实施例所提供的测试存取端口电路可以通过指令缓存器组来控制模式缓存器组,并通过模式缓存器组来控制内部信号的路径,因此无需重新设计控制器中的有限状态机,而可以维持测试存取端口电路在设计上的弹性。

[0042]

以上所述仅为本发明的优选实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

[0043]

【符号说明】

[0044]

100、200、300 测试存取端口电路

[0045]

110、210、310 控制器

[0046]

trst 重置端

[0047]

tck 频率信号端

[0048]

tms 模式选择端

[0049]

tdo 数据输出端

[0050]

tdi 数据输入端

[0051]

ir 指令缓存器组

[0052]

dr1至drx 测试数据缓存器组

[0053]

ar1、ar2、ar3 辅助数据缓存器组

[0054]

di1、di2、di3 输入数据位

[0055]

do1、do2、do3 输出数据位

[0056]

vh 默认电压

[0057]

sig

rst 重置信号

[0058]

demux 解多任务器

[0059]

mux 多任务器

[0060]

mr1、mr2、mr3、mr4 模式缓存器组

[0061]

220 路径选择电路

[0062]

230、340、350 双向信号选择电路

[0063]

na1、na2、nb1、nb2、nc1、nc2、nd1、nd2 数值。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1