一种基于储备池计算的工作记忆硬件实现方法与流程

[0001]

本发明涉及人工智能、生命科学技术领域,具体涉及一种基于储备池计算的工作记忆硬件实现方法。

背景技术:

[0002]

2001年,jaeger对传统的递归神经网络进行修改,使用非线性sigmoid函数模拟神经元的非线性状态,并将改良后的网络称为回声状态神经网络;同年,maass推出了流体状态机,该状态机网络所采用的思想和回声状态神经网络一样,只不过流体状态机的基础是神经计算,而回声状态神经网络的基础是机器学习,储备池计算是一种通用的神经形态计算方法,由回声状态神经网络和流体状态机发展而来,相较于回声状态神经网络及流体状态机,储备池计算算法更为方便易用,在储备池计算系统进行训练时,只有输出部分的权重需要得到大量频繁的修正,输入部分和计算部分的权重是固定不变的,这样的算法设计在便于硬件实现的同时还能够节省大量的存储资源,使得一个低功耗时序神经形态计算硬件加速器的实现变为可能,同时,得意于人们在新型半导体器件方面的发展,一些器件具有记录过往输入信息的天然特性,这样的器件使得储备池计算得到了更好的应用和发展。

[0003]

工作记忆是人类在短时间内维持和执行任务相关信息能力的记忆系统,在语言理解、学习、推力、思维等高级认知过程中起到关键作用,工作记忆由4个主要内部系统构成:中央执行系统、语音回路系统、视觉空间系统、情景缓冲区系统,人们可以通过这些内部系统储存环境中的信息,并最终被人们所利用。但是在目前的生命科学领域,人们还停留在使用mems探针技术、cmos纳米电极等技术获取生物神经元内部和神经元之间的数据阶段,并不能够根据神经元输入刺激直接通过硬件模仿神经元的发放特性,所以如何通过软件算法和硬件实现模拟神经元的工作记忆特性是当前亟需解决的难题。

技术实现要素:

[0004]

本发明的目的在于:针对以上所述现有技术存在的问题或不足,为解决工作记忆难以通过硬件实现的技术问题,本发明提供了一种基于储备池计算的工作记忆硬件实现方法,将储备池计算和工作记忆相结合,通过新型半导体存储器件构造储备池计算电路,节省了大量存储资源的同时将神经元当前输入刺激与过往输入刺激相关联,实现“记忆”功能,并通过后续readout计算模块中的神经兴奋型网络和神经抑制型网络对硬件网络中的神经元分别进行兴奋和抑制处理,实现工作记忆的发放特性,较好的实现了工作记忆的硬件模拟。

[0005]

本发明采用的技术方案如下:一种基于储备池计算的工作记忆硬件实现方法,所述方法通过以下系统实现,该系统包括两大部分:储备池计算模块和readout计算模块,所述储备池计算模块主要实现不同时刻输入刺激之间的关联,包括:储备池输入部分、储备池计算部分、储备池输出部分;所述readout计算模主要实现工作记忆中神经兴奋和神经抑制的功能,包括:神经兴奋型网络、神经抑制型网络、激活函数部分、全连接层部分。

[0006]

进一步地,所述储备池输入部分负责接收外界给予的神经元刺激信号,并按照权重分配原则将其分配至储备池计算中的各个存储单元。

[0007]

进一步地,所述储备池计算部分是由具有记忆功能特性的存储单元构成,所述存储单元支持但不限于忆阻器器件单元,存储单元之间互相连接,存储单元接收到来自储备池输入部分的信息后,将当前信号与过往的输入信号相关联并映射至高维空间中,交由后续的储备池输出部分进行信息的输出。

[0008]

进一步地,所述储备池输出部分负责储备池计算结果的输出,储备池输出部分按照权重分配的原则将储备池部分的计算结果传输至readout计算模块。

[0009]

进一步地,所述储备池计算模块中的存储单元由新型半导体存储器件构成,具有对时域输入信号的记忆功能,该存储单元在长时间没有输入刺激的情况下,其存储特性一直处于低态,在向该存储单元给予一个输入刺激后,存储单元的特性会在短时间内快速变化,并进入到高态,存储特性达到最高点后,特性会随着时间的推移不断缓慢衰减直至恢复到默认状态。

[0010]

进一步地,所述神经兴奋型网络负责工作记忆兴奋性的表达,由一个神经网络构成,该神经网络中的各层神经元之间联系紧密、逻辑距离相近,能够通过复杂计算分析出连续输入刺激中反复提及到的工作记忆区域,并对这类工作记忆进行兴奋表达,从而提高神经元的发放率特性。

[0011]

进一步地,所述神经抑制型网络负责工作记忆抑制性的表达,由一个神经网络构成,该神经网络中的各层神经元之间联系稀疏、逻辑距离较远,能够通过复杂计算分析出当前输入刺激和过往输入刺激中不同的部分,提取出过往输入刺激中兴奋的部分,假若这些兴奋的区域在当前输入中不再被表达,则对该工作记忆区域进行抑制表达,从而降低神经元的发放特性。

[0012]

进一步地,所述激活函数部分对神经兴奋型网络和神经抑制型网络的计算分析结果进行非线性映射,方便后续全连接层部分的输出,本发明支持但不限于tanh、sigmoid、relu、leaky-relu等非线性激活函数。

[0013]

进一步地,所述全连接层部分负责工作记忆发放特性的输出。

[0014]

一种基于储备池计算的工作记忆硬件实现方法,具体工作流程如下:

[0015]

s1:全局复位,将系统中的所有模块进行初始化;

[0016]

s2:将训练好的神经网络数学模型中的权重信息和网络结构信息存储到readout计算模块中;

[0017]

s3:向工作记忆硬件输入神经元刺激信号;

[0018]

s4:储备池计算模块采集刺激信号,并将其分配至储备池计算部分,利用具有记忆功能的存储器对刺激信号进行计算,将过往的刺激信息与当前的刺激信息相关联,并将计算结果通过储备池输出部分传输至readout计算模块;

[0019]

s5:readout计算模块接收到来自储备池计算模块的信号后,将信号分别传入至神经兴奋型网络和神经抑制型网络,两类神经网络分别对信号数据进行计算分析,并进行工作记忆的兴奋和抑制表达,将表达的结果传输至后续的激活函数部分;

[0020]

s6:激活函数部分接收到来自readout计算模块的信号后,将数据进行非线性映射,方便于后续全连接层的输出;

[0021]

s7:全连接层部分根据激活函数的处理结果对神经元工作记忆发放特性进行表达输出,完成此轮输入刺激的结果表达后,跳转至步骤3继续进行新一轮的神经元刺激输入,直到整个工作记忆硬件关闭为止。

[0022]

相较于现有技术,本发明的有益效果是:

[0023]

(1)本发明提供了一种基于储备池计算的工作记忆硬件实现方法,将储备池计算和工作记忆相结合,通过新型半导体存储器件构造储备池计算电路,节省了大量存储资源的同时将神经元当前输入刺激与过往输入刺激相关联,实现“记忆”功能,并通过后续readout计算模块中的神经兴奋型网络和神经抑制型网络对硬件网络中的神经元分别进行兴奋和抑制处理,实现工作记忆的发放特性,较好的实现了工作记忆的硬件模拟。

附图说明

[0024]

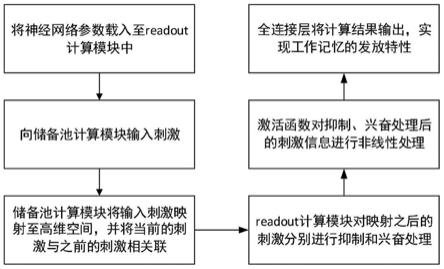

图1为本发明一种基于储备池计算的工作记忆硬件实现方法的硬件实现示意图;

[0025]

图2为本发明一种基于储备池计算的工作记忆硬件实现方法中存储单元的特性示意图;

[0026]

图3为本发明一种基于储备池计算的工作记忆硬件实现方法中存储单元特性在不同输入脉冲情况下的特性示意图;

[0027]

图4为本发明一种基于储备池计算的工作记忆硬件实现方法的储备池计算模块的结构示意图;

[0028]

图5为本发明一种基于储备池计算的工作记忆硬件实现方法的readout计算模块的结构示意图;

[0029]

图6为本发明一种基于储备池计算的工作记忆硬件实现方法的工作流程示意图。

具体实施方式

[0030]

为了使本发明的目的、技术方案及优点更加清楚明白,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明,即所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

[0031]

如图1所示,该图展示了本发明基于储备池计算的工作记忆硬件实现示意图,该系统主要包括两大部分:储备池计算模块和readout计算模块,储备池计算模块包括:储备池输入部分、储备池计算部分、储备池输出部分,储备池计算模块主要实现不同时刻输入刺激之间的关联,负责接收外界给予的神经元输入刺激,并通过内部的储备池计算网络将过往的输入刺激信息与当前的输入刺激信息相关联,实现短时间内对于连续刺激的记忆功能,然后将处理后的信息传输至readout计算模块;readout计算模块包括:神经兴奋型网络、神经抑制型网络、激活函数部分、全连接层部分,readout计算模块主要实现工作记忆中神经兴奋和神经抑制的功能,根据处理后的刺激信息对神经元进行兴奋和抑制处理,得出神经元的发放特性,最终实现神经元工作记忆发放特性的模拟。

[0032]

储备池计算模块的储备池输入部分负责接收外界给予的神经元刺激信号,并按照权重分配原则将其分配至储备池计算中的各个存储单元;储备池计算模块的储备池计算部分是由具有记忆功能特性的存储单元构成,所述存储单元支持但不限于忆阻器器件单元,存储单元之间互相连接,存储单元接收到来自储备池输入部分的信息后,将当前信号与过

往的输入信号相关联并映射至高维空间中,交由后续的储备池输出部分进行信息的输出;储备池计算模块的储备池输出部分负责储备池计算结果的输出,储备池输出部分按照权重分配的原则将储备池部分的计算结果传输至readout计算模块。

[0033]

本发明储备池计算模块中关于存储单元的特性示意图如附图2所示,该存储单元是一种新型半导体器件,具有对时域输入信号的记忆功能,该存储单元在长时间没有输入刺激的情况下,其存储特性一直处于低态,在向该存储单元给予一个输入刺激后,存储单元的特性会在短时间内快速变化,并进入到高态,存储特性达到最高点后,特性会随着时间的推移不断缓慢衰减直至恢复到默认状态。

[0034]

储备池计算模块的具体结构如附图4所示,储备池计算模块是基于回声状态神经网络和流体状态机发展改良而来的,如图4展示的那样,该计算模块包含:储备池输入层、储备池计算层、储备池输出层,各层的神经元个数都需要按照实际应用情况进行确定,储备池计算层所需的存储单元不宜过多,否则会出现过拟合的现象,另外,储备池输入层和计算层之间通过权重矩阵连接,储备池计算层和输出层之间也通过权重矩阵连接,储备池计算模块在接收到输入刺激后,将输入信号与输入权重相乘,并分配给计算层中不同的存储单元中,存储单元之间互相随机连接,在接收到输入信号后便通过存储特性反应出刺激信号的计算结果,并将计算结果与输出矩阵相乘,通过输出层将最终的信号处理结果输出至后续的readout计算模块。

[0035]

readout计算模块的具体结构如附图5所示,该readout计算模块是基于神经网络而来的,包含:神经抑制型网络、神经兴奋性网络、激活函数层、全连接层。神经抑制型网络负责工作记忆抑制性的表达,由一个神经网络构成,神经抑制型网络中的神经元之间联系不紧密、逻辑距离较远,能够通过复杂计算分析出当前输入刺激和过往输入刺激中不同的部分,提取出过往输入刺激中兴奋的部分,假若这些兴奋的区域在当前输入中不再被表达,则对该工作记忆区域进行抑制表达,从而降低神经元的发放特性,目的在于有意地丢失部分许久未经提及的工作记忆区域;神经兴奋型网络负责工作记忆兴奋性的表达,由一个神经网络构成,神经兴奋型网络中的神经元之间联系紧密、逻辑距离很近,该网络能够通过复杂计算分析出连续输入刺激中反复提及到的工作记忆区域,并对这类工作记忆进行兴奋表达,从而提高神经元的发放率特性。

[0036]

readout计算模块在接收到来自储备池计算模块的数据后,分别通过神经抑制型网络和神经兴奋型网络对数据进行计算处理,分析出其中的抑制区域和兴奋区域,并对工作记忆中需要抑制的区域进行抑制表达、对工作记忆中需要兴奋的区域进行兴奋表达,表达的结果传输至激活函数层,激活函数层对表达结果进行非线性处理,所支持的非线性激活函数包括但不限于tanh、sigmoid、relu、leaky-relu等,处理后的数据与输出矩阵相乘,最终由全连接层进行工作记忆发放特性的输出。

[0037]

如图3所示,该图展示了本发明储备池计算模块中存储单元特性在不同输入脉冲情况下的特性示意图,首先向存储单元输入3个连续刺激,存储单元的特性从默认状态迅速激发至高态。随后不向存储单元输入激励,存储单元的特性便逐渐衰减。接着向存储单元输入3个不连续的刺激,存储单元的特性先上升后衰减。最后向存储单元输入连续刺激,存储单元特性迅速上升,利用存储单元这样的功能特性,便可将过往的输入刺激和当前的输入刺激相关联,从而实现对于输入刺激的记忆功能。

[0038]

一种基于储备池计算的工作记忆硬件实现方法,具体工作流程如下:

[0039]

s1:全局复位,将系统中的所有模块进行初始化;

[0040]

s2:将训练好的神经网络数学模型中的权重信息和网络结构信息存储到readout计算模块中;

[0041]

s3:向工作记忆硬件输入神经元刺激信号;

[0042]

s4:储备池计算模块采集刺激信号,并将其分配至储备池计算部分,利用具有记忆功能的存储器对刺激信号进行计算,将过往的刺激信息与当前的刺激信息相关联,并将计算结果通过储备池输出部分传输至readout计算模块;

[0043]

s5:readout计算模块接收到来自储备池计算模块的信号后,将信号分别传入至神经兴奋型网络和神经抑制型网络,两类神经网络分别对信号数据进行计算分析,并进行工作记忆的兴奋和抑制表达,将表达的结果传输至后续的激活函数部分;

[0044]

s6:激活函数部分接收到来自readout计算模块的信号后,将数据进行非线性映射,方便于后续全连接层的输出;

[0045]

s7:全连接层部分根据激活函数的处理结果对神经元工作记忆发放特性进行表达输出,完成此轮输入刺激的结果表达后,跳转至步骤3继续进行新一轮的神经元刺激输入,直到整个工作记忆硬件关闭为止。

[0046]

以上所述实施例仅表达了本申请的具体实施方式,其描述较为具体和详细,但并不能因此而理解为对本申请保护范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请技术方案构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1