一种SiCMOSFET驱动电路参数优化设计方法与流程

一种sic mosfet驱动电路参数优化设计方法

技术领域

[0001]

本发明涉及一种sic mosfet驱动电路参数优化设计方法。

背景技术:

[0002]

目前sic mosfet在实际应用中,仍然沿用传统sic mosfet的驱动设计方法。然而,sic mosfet一般具有较快的开关速度和较高的电压承受能力,因而相比si器件具有更高的电压变化率,栅源电压干扰问题更突出。

[0003]

限制其sic mosfet开关速度的两个主要因素是栅极驱动能力和栅源电压干扰问题。参考文献[1]、参考文献[2]以及参考文献[3]在传统simosfet的驱动电路设计基础上,额外增加栅源电压最大变化值校验环节,依据电压变化率、驱动电阻和结电容等效电路估算了干扰引起的栅源电压最大变化值,防止栅源电压干扰问题引发器件损伤甚至失效。类似的,参考文献[4]中详细介绍了10kv sic mosfet在开关瞬态时的表征,指出在导通瞬态中,栅源电压干扰的正向尖峰将可能产生击穿电流,且由于该击穿电流的存在,增大导通电流和导通损耗;在关断瞬态中,栅源电压干扰的负向尖峰在超过允许范围时将会导致器件性能退化。在此基础上,参考文献[4]讨论了对栅源电压的干扰和对开关速度的限制,并在极端情况下,即假设通过器件的米勒电容的所有电流都对其栅源电容进行充电时,通过结电容等效电路估算最大栅源电压变化幅度。

[0004]

这些研究解释了栅源电压干扰的本质原因,为改进栅极驱动电路设计、消除干扰、提高开关速度提供了概念性依据;然而,这些研究尚未考虑影响sic mosfet动态特性的关键杂散参数,如栅极内阻、驱动回路电感和功率回路电感等。sic mosfet驱动电路参数优化设计方法尚不完备,急需针对sic mosfet高开关速度的特点,探索适合sic基mosfet的驱动设计方法,为sic mosfet器件未来在更高功率等级、更高性能要求场合的应用提供理论指导和应用技术支撑。

[0005]

参考文献:

[0006]

[1]zhang z,zhang w,wang f,et al.analysis of the switching speed limitation of wide band-gap devices in a phase-leg configuration:2012 ieee energy conversion congress and exposition(ecce),raleigh,usa,2012[c].ieee,15-20sep.2012.

[0007]

[2]chen z.characterization and modeling of high-switching-speed behavior of sic active devices[dissertation].virginiapolytechnic institute,2009.

[0008]

[3]nguyen b,zhang x,ferencz a,et al.analytic model for power mosfet turn-off switching loss under the effect of significant current diversion at fast switching events:2018ieee applied power electronics conference and exposition(apec),2018[c].287-291.

[0009]

[4]ji s,zheng s,wang f,et al.temperature-dependent characterization,

modeling,and switching speed-limitation analysis of third-generation 10-kv sic mosfet[j].ieee t power electr,2018,33(5):4317-4327.

技术实现要素:

[0010]

本发明要解决的技术问题,在于提供一种sic mosfet驱动电路参数优化设计方法,揭示驱动电阻与干扰尖峰、干扰振荡之间的关系,以栅极应力最小为目标,进行优化设计驱动电阻,提升sic基电力电子变换器的设计可靠性。

[0011]

本发明是这样实现的:一种sic mosfet驱动电路参数优化设计方法,包括如下步骤:

[0012]

步骤s1:构造干扰路径传递函数的特征多项式d(s);

[0013]

步骤s2:根据特征多项式构造标准二阶系统ct(s)=1/d(s);

[0014]

步骤s3:取sic mosfet的输入电容c

iss

和栅极内电阻r

g

为基准值进行参数标幺化:并联辅助电容驱动回路杂散电感驱动电阻r

*

=r/r

g

;

[0015]

步骤s4:验证杂散电感是否达到设定要求,以保证标准二阶系统ct(s)具有限定的阻尼比,驱动回路杂散电感标幺值为:

[0016][0017]

步骤s5:设计辅助并联电容标幺值:

[0018][0019]

步骤s6:设计驱动电阻标幺值:

[0020]

。

[0021]

进一步地,所述干扰路径传递函数为:

[0022][0023]

式中,d(s)为特征多项式,r表示驱动回路电阻,r

g

表示mosfet栅极内电阻,c

rss

和c

iss

均表示mosfet结电容,c

a

表示栅源极并联辅助电容,l

i

表示驱动回路电感,包括栅极引脚寄生电感l

g

以及源极引脚上的驱动回路电感l

s

,s为复频域。

[0024]

进一步地,所述驱动回路传递函数的特征多项式d(s),由于该特征多项式的三阶项系数远小于其他几项系数,将其近似视为二阶多项式,其数学表达式为:

[0025]

d(s)=s2(rr

g

c

a

c

iss

+l

i

c

iss

)+s(r

g

c

iss

+rc

iss

+rc

a

)+1

[0026]

式中,r表示驱动回路电阻,r

g

表示mosfet栅极内电阻,c

iss

表示mosfet结电容,c

a

表示栅源极并联辅助电容,l

i

表示驱动回路电感,包括栅极引脚寄生电感l

g

以及源极引脚上的驱动回路电感l

s

,s为复频域。

[0027]

进一步地,所述干扰路径的特性由d(s)进行描述,描述栅源电压干扰的标准二阶系统ct(s)为:

[0028]

。

[0029]

进一步地,根据所述标准二阶系统ct(s),得到其阻尼比为:

[0030]

。

[0031]

进一步地,取sic mosfet的输入电容c

iss

和栅极内电阻r

g

为基准值,其中c

iss

作为杂散电感和结电容的基准值,r

g

为驱动电阻的基准值;标幺化后的栅源极并联辅助电容驱动回路杂散电感驱动电阻r

*

=r/r

g

,根据所述标准二阶系统ct(s),以标幺值表示的标准二阶系统ct(s)的阻尼比为:

[0032]

。

[0033]

进一步地,根据所述标准二阶系统ct(s),得到其无阻尼自振频率为:

[0034]

。

[0035]

进一步地,取sic mosfet的输入电容c

iss

和栅极内电阻r

g

为基准值,其中c

iss

作为杂散电感和结电容的基准值,r

g

为驱动电阻的基准值;标幺化后的栅源极并联辅助电容驱动回路杂散电感驱动电阻r

*

=r/r

g

,根据所述标准二阶系统ct(s),以标幺值表示的标准二阶系统ct(s)的无阻尼自振频率为:

[0036]

。

[0037][0038]

进一步地,所述的驱动回路传递函数g

i

(s),其对斜率为k=

±

v

dc

/t

r

的斜坡信号响应为:

[0039][0040]

由终值定理可知,单位阶跃响应终值为:

[0041]

。

[0042]

进一步地,取sic mosfet的输入电容c

iss

和栅极内电阻r

g

为基准值,其中c

iss

作为杂散电感和结电容的基准值,r

g

为驱动电阻的基准值;标幺化后的栅源极并联辅助电容驱动回路杂散电感驱动电阻r

*

=r/r

g

,所述的驱动回路传递函数g

i

(s),其对斜率为k=

±

v

dc

/t

r

的斜坡信号响应为:

[0043]

[0044]

由终值定理可知,以标幺值表示的标准二阶系统ct(s)的单位阶跃响应终值为:

[0045]

c(∞)=kr

*

r

g

c

rss

。

[0046]

本发明具有如下优点:一种sic mosfet驱动电路参数优化设计方法,揭示驱动电阻与干扰尖峰、干扰振荡之间的关系,以栅极应力最小为目标,进行优化设计驱动参数,提升sic基电力电子变换器的设计可靠性。该方法简洁、直观。在实际工程应用中,对于特定的sic mosfet,根据数据手册提供的暂态特性参数,将其代入本发明提出的优化设计方法中,即可得到栅源电压干扰的标准二阶系统ct(s),其阻尼比和无阻尼自振频率描述了干扰的动态特性,这样便于直观和迅速地判断系统元件参数的合理性。于此同时,本方法对以上系统参数的标幺化处理,能大量的简化实际工程应用中的计算,节约设计所需时间,提高设计效率。

附图说明

[0047]

下面参照附图结合实施例对本发明作进一步的说明。

[0048]

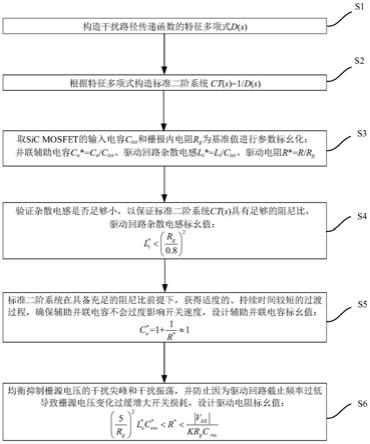

图1是根据本发明一种sic mosfet驱动电路参数优化设计方法流程图;

[0049]

图2为根据本发明实施例的一种桥臂结构中的等效电路及相应的寄生参数图;

[0050]

图3是根据本发明实施例的随栅源极并联辅助电容标幺值变化的阻尼比(ξ)曲线;

[0051]

图4a是根据本发明实施例的随驱动电阻标幺值r

*

变化的g

i

(s)的单位阶跃响应示意图;

[0052]

图4b是根据本发明实施例的随驱动电阻标幺值r

*

变化的g

i

(s)的斜坡信号响应c(t)示意图;

[0053]

图5是根据本发明实施例的随驱动电阻标幺值r

*

变化的栅源电压干扰振荡示意图;

[0054]

图6是根据本发明实施例的驱动电阻为2欧姆、r

*

=0.351的模型预测和实际测量的栅源电压干扰对比示意图;

[0055]

图7是根据本发明实施例的驱动电阻为10欧姆、r

*

=1.754的模型预测和实际测量的栅源电压干扰对比示意图;

[0056]

图8是根据本发明实施例的驱动电阻为15欧姆、r

*

=2.632的模型预测和实际测量的栅源电压干扰对比示意图。

具体实施方式

[0057]

本发明一种实施方式:

[0058]

如图1所示,该方法包括以下步骤:

[0059]

步骤s1:构造干扰路径传递函数的特征多项式d(s);

[0060]

步骤s2:根据特征多项式构造标准二阶系统ct(s)=1/d(s);

[0061]

步骤s3:取sic mosfet的输入电容c

iss

和栅极内电阻r

g

为基准值进行参数标幺化:并联辅助电容驱动回路杂散电感驱动电阻r

*

=r/r

g

;

[0062]

步骤s4:验证杂散电感是否足够小,以保证标准二阶系统ct(s)具有足够的阻尼

v

dc

/t

r

开始下降。在此干扰的激励下,栅源电压v

gs

从稳态值开始下降,当脉冲电压干扰下降结束时(时间为t

r

=40ns),栅源电压干扰到达负向尖峰,可见,该尖峰值随着驱动电阻标幺值r

*

降低而降低。

[0072]

如图5所示,为随驱动电阻标幺值r

*

变化的栅源电压干扰振荡情况。当驱动电阻标幺值r

*

由3降低到0.1过程中,无阻尼自振频率ω

n

逐步降低,导致谐振频率ω

ro

处ct(s)的幅值升高,因此,栅源电压的谐振干扰幅值升高。

[0073]

综合图4a、图4b和图5来看,在本实施例中,为保证足够的谐振抑制比,并防止因为驱动回路截止频率过低导致栅源电压变化过缓,进而造成电压变化率dv/dt、电流变化率di/dt过小,增大开关损耗。设计时应保证ω

n

<0.2ω

ro

,其中ω

ro

代表功率回路谐振角频率。干扰尖峰值与驱动电阻标幺值r

*

成正比,因此,较小的驱动电阻可以降低响应终值,一定程度上抑制干扰尖峰。为了不让干扰电压尖峰过大,本发明推荐响应的终值|c(∞)|<|v

ee

|,其中v

ee

是sicmosfet的关断偏置电压。由此可得驱动电阻标幺值r

*

的取值上限。根据分析所用参数,可得:

[0074][0075]

进而,根据驱动电阻标幺值r

*

的定义,得到驱动电阻9.45<r<10.42(ω)。

[0076]

图6、图7和图8是根据本发明实施例的不同驱动电阻下的模型预测和实际测量的栅源电压干扰对比,在v

dc

=800v的条件下,研究驱动电阻r=2、10、15ω时,栅源电压v

gs

响应漏源电压v

ds

干扰激励波形。从图6、图7和图8可以看出,模型预测波形可以较好的复现实测栅源电压波形;从图中的三个实测栅源电压波形可知:当r

*

<r

*min

时,ω

n

>0.2ω

ro

,栅源电压干扰明显;而当而当r

*

>r

*max

时,|c(∞)|>|v

ee

|时,栅源电压干扰尖峰明显,以上实验结果表明上述所示驱动电阻设计的分析对于电压干扰尖峰以及振荡的分析是十分合理且正确的。

[0077]

为有效控制sic mosfet栅源电压干扰,并保证驱动回路具有适度的过渡过程,本发明推荐sic mosfet驱动参数设计遵循以下三步:首先,验证驱动回路杂散电感标幺值是否足够小,以保证标准二阶系统ct(s)具有足够的阻尼比;其次,设计辅助并联电容标幺值标准二阶系统在具备充足的阻尼比前提下,获得适度的、持续时间较短的过渡过程;最后,设计驱动电阻标幺值r

*

,均衡抑制栅源电压的干扰尖峰和干扰振荡。详细分析如下:

[0078]

(1)验证驱动回路杂散电感标幺值是否足够小,以保证标准二阶系统ct(s)具有足够的阻尼比。

[0079]

根据自动控制原理,为了让驱动回路具有良好的动态特性,避免出现剧烈的暂态振荡,一般希望ct(s)的阻尼比ξ>0.4。考虑极端情况下,驱动电阻趋近于零(即r

*

→

0)的时候,保守估计驱动回路杂散电感是否满足要求,根据阻尼比公式可知,阻尼比需要满足:

[0080][0081]

整理可得:

[0082][0083]

上述表达式是驱动回路杂散电感的设计参考,其中,r

g

是sic mosfet的栅极内电阻。该表达式限定了驱动回路杂散电感的最大值,需要注意的是,该表达式的要求较为严苛,是在驱动电阻为零的极端情况下,保守估计,获得的设计范围,实际应用中,可以根据工程应用环境加以修正;然而,不论如何修正,新取得的参数范围,应当与表达式的推荐范围具有相同的数量级。

[0084]

(2)设计辅助并联电容标幺值标准二阶系统在具备充足的阻尼比前提下,获得适度的、持续时间较短的过渡过程,确保辅助并联电容不会过度影响开关速度。

[0085]

在sic mosfet的驱动回路杂散电感满足(1)的条件下,驱动回路杂散电感足够小,可以认为因此,公式阻尼比公式可进一步简化:

[0086][0087]

由上式可知,阻尼比ξ是栅源极并联辅助电容标幺值的函数,然而并非单调函数,因此需要分情况讨论。首先,当并联辅助电容很小的时候,且因此有:

[0088][0089]

可见,当并联辅助电容很小的时候,阻尼比ξ是栅源极并联辅助电容标幺值的单调减函数。类似的,当并联辅助电容很大的时候,且因此有:

[0090][0091]

可见,当并联辅助电容很大的时候,阻尼比ξ是栅源极并联辅助电容标幺值的单调增函数。综上两种情况,随着并联辅助电容标幺值的增大,阻尼比ξ减小后增大,其存在极小值。极值点出现于偏导数为零的点,因此由

[0092][0093]

可得阻尼比ξ最小的时候,并联辅助电容标幺值:

[0094][0095]

因此,在sic mosfet的驱动回路杂散电感满足(1)的条件下,驱动回路标准二阶系

统ct(s)的阻尼比为:

[0096][0097]

可见,驱动回路标准二阶系统ct(s)将一直处于过阻尼状态,具备充足的阻尼比,不至于引发振荡。然而,需要注意的是,过阻尼状态下,阻尼比过大,将导致系统的过渡时间过长,驱动回路的动态过程过缓。为了让驱动回路获得持续时间适度的过渡过程,在具备充足的阻尼比不至于振荡的前提条件下,阻尼比应当尽量小,本发明推荐并联辅助电容标幺值的设计遵循公式使得阻尼比ξ处于最小值。

[0098]

(3)设计驱动电阻标幺值r

*

,均衡抑制栅源电压的干扰尖峰和干扰振荡,并防止因为驱动回路截止频率过低导致栅源电压变化过缓增大开关损耗。

[0099]

经过(1)和(2)的设计,驱动回路将获得平滑无振荡且过渡时间适度的动态过程,以此为基础,依据无阻尼自振频率以及单位阶跃响应终值标幺值表达式,进一步确定驱动电阻标幺值r

*

的取值范围,研究驱动电阻的设计方法。为保证足够的谐振抑制比,并防止因为驱动回路截止频率过低导致栅源电压变化过缓,进而造成电压变化率dv/dt、电流变化率di/dt过小,增大开关损耗。设计时应保证ω

n

<0.2ω

ro

,其中ω

ro

代表功率回路谐振角频率,采用标幺化表示为:

[0100][0101]

其中,标幺化后的sic mosfet输出电容标幺化后的功率回路杂散电感由无阻尼自振频率表达式可知,ω

n

与驱动电阻标幺值r

*

成反比。在设计的前提下,可得驱动电阻标幺值r

*

的取值下限,即:

[0102][0103]

由上述的单位阶跃响应终值标幺值表达式可知,干扰尖峰值与驱动电阻标幺值r

*

成正比,因此,较小的驱动电阻可以降低响应终值,一定程度上抑制干扰尖峰。为了不让干扰电压尖峰过大,本文推荐响应的终值|c(∞)|<|v

ee

|,其中v

ee

是sic mosfet的关断偏置电压。由此可得驱动电阻标幺值r

*

的取值上限,即:

[0104][0105]

综上,本发明推荐驱动电阻标幺值r

*

的设计取值范围是:

[0106][0107]

综合考虑上述设计原则(1)、(2)、(3),为有效控制sic mosfet栅源电压干扰,并保证驱动回路具有适度的过渡过程,本发明所述一种sicmosfet驱动电路参数优化设计方法,

分别依次设计驱动回路杂散电感标幺值辅助并联电容标幺值驱动电阻标幺r

*

:

[0108]

.

[0109]

虽然以上描述了本发明的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本发明的范围的限定,熟悉本领域的技术人员在依照本发明的精神所作的等效的修饰以及变化,都应当涵盖在本发明的权利要求所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1