一种基于电阻单元级联的去嵌方法

1.本发明涉及一种方法,具体涉及一种基于电阻单元级联的去嵌方法,属于射频器件测试技术领域。

背景技术:

2.为了在电子器件、集成电路设计中提高良品率、降低研发成本,需要对电路器件(如晶体管、电感、电阻,等)建立模型,获得准确的器件测试数据是其中的关键步骤。由于在片测试集成电路器件时探针无法与器件直接相连,需要在器件的输入和输出端口增加焊盘、互连线等嵌入结构。使用相应的去外嵌(简称去嵌)方法,将嵌入结构对器件测试的影响从原始测试数据中去除,才能获取器件本身的测试数据。

3.文献1(h.ito and k.masuy,“a simple through

‑

only de

‑

embedding method for on

‑

wafer s

‑

parameter measurements up to 110ghz,”ieee mtt

‑

s international microwave symposium digest,pp.383

–

386,jun.2008)针对片上传输线去嵌,对待测传输线器件输入/输出端口的嵌入结构建立等效电路模型。使用直通结构的测试散射参数,提取嵌入结构模型的元件参数,计算得到嵌入结构的散射参数并从原始测试数据中剥离。该方法需要对嵌入结构建立精确的等效电路模型,并依赖于使用直通结构测试数据提取模型参数,存在提参多值解问题,进而影响了去嵌精度。

4.为了改善对嵌入结构建立等效电路模型提参困难、精度不高的缺陷,文献2(jun luo,lei zhang,and yan wang,“a distributed de

‑

embedding solution for cmos mm

‑

wave on

‑

wafer measurements based

‑

on double open

‑

short technique,”ieee microw.wireless compon.lett.,vol.23,no.12,pp.686

–

688,dec.2013)提出了一种基于标准传输线方程的去嵌方法。该方法通过获取焊盘

‑

开路/焊盘

‑

短路/互连线

‑

开路/互连线

‑

短路测试结构的测试数据,去除焊盘外嵌寄生,并计算得到嵌入结构中互连线的导纳参数矩阵,然后使用标准传输线方程计算得到传输线的特征阻抗和传播系数等参数。该方法的缺陷是需要使用四种复杂测试结构,占用芯片面积较大,且依赖于获取复杂测试结构准确的测试数据,增大了测试难度。

5.为了改善测试结构复杂,占用芯片面积较大的缺陷,文献3(h.j.saavedra

‑

gomez,j.r.loo

‑

yau,p.moreno,b.e.figueroa

‑

resendiz,and j.a.reynoso

‑

hernandez,“onwafer cmos transistors de

‑

embedding method using two transmission lines of different lengths,”ieee radio frequency integrated circuits symposium(rfic),pp.417

–

420,jun.2012)使用两组片上传输线测试结构的测试散射参数,基于标准传输线方程计算得到传输线的特征阻抗和传播系数参数,进而计算得到传输线的散射参数矩阵。该方法的缺陷是需要简化焊盘的散射参数矩阵以便于计算,进而影响了去嵌精度。

6.综上所述,传统的去嵌方法为了达到较高的去嵌精度,有的技术途径需要使用复杂且数量较多的测试结构,去嵌过程复杂且占用了较大的芯片面积;有的技术途径减少了测试结构的数量,但是对嵌入结构进行简化。迄今尚缺少一种结构简单、测试简便、精度高

的去嵌技术。

技术实现要素:

7.本发明正是针对现有技术中存在的问题,提供一种基于电阻单元级联的去嵌方法,该技术方案提供一种结构简单、测试简便、精度较高的去嵌技术,可以实现传统技术必须依靠复杂结构或不同方式才能分别实现的性能。

8.为了实现上述目的,本发明的技术方案如下,一种基于电阻单元级联的去嵌方法,所述方法包括以下步骤:

9.步骤1:先分别获取两个不同阻值的片上电阻器件测试结构的测试散射参数;

10.步骤2:然后,将两个电阻器件测试结构中的电阻分别划分成几个相邻且相同的电阻单元,所述一个电阻器件的电阻单元比另外一个电阻器件的电阻单元多1个或以上,使用两个电阻器件测试结构的测试散射参数,通过算法计算得到焊盘、互连线以及通孔的散射参数

11.步骤3:最后,将电阻器件测试结构的测试散射参数去除焊盘、互连线以及通孔的散射参数,得到待测电阻器件的散射参数。该技术方案结构简单且不需要开路测试结构、直通测试结构和短路测试结构中的一种,可以实现传统技术必须依靠复杂结构或不同方式才能分别实现的性能。本发明的方法适用于电感、电阻等器件的微波测试及建模。

12.作为本发明的一种改进,步骤2中,将两个不同阻值的电阻器件测试结构中的电阻划分成几个相邻且相同的电阻单元;所述电阻的abcd矩阵参数是由划分成几个相邻电阻单元的abcd矩阵参数相乘。

13.作为本发明的一种改进,步骤2中,两个不同阻值的电阻器件测试结构中电阻的abcd矩阵参数分别记为[a1]和[a2];将第一个电阻器件测试结构中的电阻划分成n个电阻单元,划分成n个电阻单元的abcd矩阵记为[a

1,k

],k=1,2,3,

…

n;将第二个电阻器件测试结构中的电阻划分成n+1个电阻单元,划分成n+1个电阻单元的abcd矩阵记为[a

2,m

],m=1,2,3,

…

n+1;第一和第二个电阻器件测试结构中电阻的abcd矩阵参数表达式分别为

[0014]

[a1]=[a

1,1

][a

1,2

][a

1,3

]

…

[a

1,n

]

[0015]

[a2]=[a

2,1

][a

2,2

][a

2,3

]

…

[a

2,(n+1)

]。

[0016]

作为本发明的一种改进,上述步骤具体如下:

[0017]

步骤1:分别测量第一和第二个电阻器件测试结构的测试散射参数[s

1dut

]和[s

2dut

],并将其变换为abcd矩阵参数[a

1dut

]和[a

2dut

];

[0018]

步骤2:将第一和第二个电阻器件测试结构中的电阻,分别划分为n个和n+1个相邻且相同的电阻单元,每个电阻单元电阻值为r,电阻单元的abcd矩阵参数记为[a];第一和第二个电阻器件测试结构中电阻的abcd矩阵参数表达式分别为

[0019][0020][0021]

第一和第二个电阻器件测试结构的abcd矩阵参数表达式分别为

[0022]

[0023][0024]

其中,[a

in

]代表两个电阻器件测试结构中输入焊盘、输入互连线与输入通孔级联后的abcd矩阵,[a

out

]代表两个电阻器件测试结构中输出通孔、输出互连线与输出焊盘级联后的abcd矩阵;

[0025]

使用关系式和计算得到[a

in

],[a

out

];

[0026]

步骤3:通过公式计算得到两个待测电阻器件的散射参数[s1]和[s2]。

[0027]

相对于现有技术,本发明具有如下优点,该技术方案提供一种基于电阻单元级联的去嵌方法,该方案利用两个电阻器件测试结构的测试散射参数,计算得到焊盘、互连线以及通孔的散射参数并进行去嵌,本发明技术具有的有益特点是结构简单且不需要开路测试结构、直通测试结构和短路测试结构中的一种,可以实现传统技术必须依靠复杂结构或不同方式才能分别实现的性能。

附图说明

[0028]

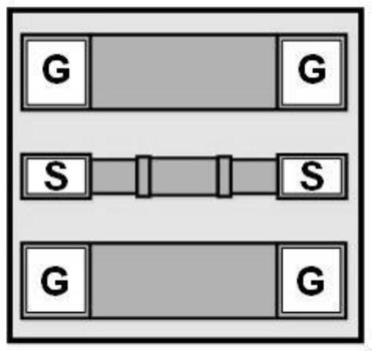

图1是本发明实施例待测器件和嵌入结构示意图。

[0029]

图2是本发明实施例器件测试结构的二端口网络级联示意图。

[0030]

图3是待测器件(50ω电阻)在不同频点上s11,s12参数的实部和虚部,其中,虚线代表开路

‑

直通法,点划线代表标准传输线方程法,实线代表本技术。

[0031]

图4是待测器件(100ω电阻)在不同频点上s11,s12参数的实部和虚部,其中,虚线代表开路

‑

直通法,点划线代表标准传输线方程法,实线代表本技术。

具体实施方式:

[0032]

为了加深对本发明的理解,下面结合附图对本实施例做详细的说明。

[0033]

实施例1:参见图1,一种基于电阻单元级联的去嵌方法,所述方法包括以下步骤:

[0034]

步骤1:先分别获取两个不同阻值的片上电阻器件测试结构的测试散射参数;

[0035]

步骤2:然后,将两个电阻器件测试结构中的电阻分别划分成几个相邻且相同的电阻单元,所述一个电阻器件的电阻单元比另外一个电阻器件的电阻单元多1个或以上,使用两个电阻器件测试结构的测试散射参数,通过算法计算得到焊盘、互连线以及通孔的散射参数

[0036]

步骤3:最后,将电阻器件测试结构的测试散射参数去除焊盘、互连线以及通孔的散射参数,得到待测电阻器件的散射参数。

[0037]

步骤2中,将两个不同阻值的电阻器件测试结构中的电阻划分成几个相邻且相同的电阻单元;所述电阻的abcd矩阵参数是由划分成几个相邻电阻单元的abcd矩阵参数相乘。

[0038]

步骤2中,两个不同阻值的电阻器件测试结构中电阻的abcd矩阵参数分别记为[a1]和[a2];将第一个电阻器件测试结构中的电阻划分成n个电阻单元,划分成n个电阻单元的abcd矩阵记为[a

1,k

],k=1,2,3,

…

n;将第二个电阻器件测试结构中的电阻划分成n+1个

电阻单元,划分成n+1个电阻单元的abcd矩阵记为[a

2,m

],m=1,2,3,

…

n+1;第一和第二个电阻器件测试结构中电阻的abcd矩阵参数表达式分别为

[0039]

[a1]=[a

1,1

][a

1,2

][a

1,3

]

…

[a

1,n

]

[0040]

[a2]=[a

2,1

][a

2,2

][a

2,3

]

…

[a

2,(n+1)

]。

[0041]

其中:

[0042]

步骤1:分别测量第一和第二个电阻器件测试结构的测试散射参数[s

1dut

]和[s

2dut

],并将其变换为abcd矩阵参数[a

1dut

]和[a

2dut

];

[0043]

步骤2:将第一和第二个电阻器件测试结构中的电阻,分别划分为n个和n+1个相邻且相同的电阻单元,每个电阻单元电阻值为r,电阻单元的abcd矩阵参数记为[a];第一和第二个电阻器件测试结构中电阻的abcd矩阵参数表达式分别为

[0044][0045][0046]

第一和第二个电阻器件测试结构的abcd矩阵参数表达式分别为

[0047]

[a

1dut

]=[a

in

][a1][a

out

]=[a

in

][a]

n

[a

out

]

[0048]

[a

2dut

]=[a

in

][a2][a

out

]=[a

in

][a]

n+1

[a

out

]

[0049]

其中,[a

in

]代表两个电阻器件测试结构中输入焊盘、输入互连线与输入通孔级联后的abcd矩阵,[a

out

]代表两个电阻器件测试结构中输出通孔、输出互连线与输出焊盘级联后的abcd矩阵;

[0050]

使用关系式和计算得到[a

in

],[a

out

];

[0051]

步骤3:通过公式计算得到两个待测电阻器件的散射参数[s1]和[s2]。

[0052]

具体实施例:下面结合一个具体示例,说明本发明实施例的具体去嵌过程。

[0053]

由于探针无法与在片测试的集成电路器件直接相连,需要在器件的输入/输出测试端口添加焊盘、互连线等嵌入结构,本发明实施例片上电阻器件测试结构如图1所示。为了获取器件本身的测试散射参数,需要通过去嵌步骤精确去除嵌入结构的影响。

[0054]

针对0.1μm gan工艺,电阻器件测试结构的焊盘、互连线、通孔和器件单元级联形式如图2所示。一种基于电阻单元级联的去嵌方法,包括如下步骤:

[0055]

步骤1:分别测量两个阻值为50ω,100ω的电阻器件测试结构的测试散射参数和并将其变换为abcd矩阵参数和

[0056]

步骤2:将第一和第二个电阻器件测试结构中的电阻,分别划分为1个和2个相邻且相同的电阻单元,每个电阻单元电阻值为r,电阻单元的abcd矩阵参数记为[a];第一和第二个电阻器件测试结构中电阻的abcd矩阵参数表达式为

[0057]

[a1]=[a]

[0058]

[a2]=[a][a]=[a]2[0059]

第一和第二个电阻器件测试结构的abcd矩阵参数表达式为

[0060][0061][0062]

其中,[a

in

]代表两个电阻器件测试结构中输入焊盘、输入互连线与输入通孔级联后的abcd矩阵,[a

out

]代表两个电阻器件测试结构中输出通孔、输出互连线与输出焊盘级联后的abcd矩阵;

[0063]

使用关系式和计算得到[a

in

],[a

out

];将abcd矩阵[a

in

]中各个参数记为a

io

,b

io

,c

io

,d

io

,根据[a

in

]和[a

out

]之间的关系,abcd矩阵[a

out

]中各个参数为d

io

,b

io

,c

io

,a

io

,从而计算得到[a

in

]和[a

out

]的表达式为:

[0064][0065][0066]

步骤3:通过公式计算得到两个待测电阻器件的散射参数[s1]和[s2]。

[0067]

根据所述一种基于电阻单元级联的去嵌步骤,对去嵌后的两个阻值为50ω,100ω的电阻器件,在0

‑

66ghz频率区间内,作不同频点上的s11,s12参数的实部和虚部,曲线分别如图3和图4所示;作为对比,开路

‑

直通法和标准传输线方程法得到的不同频点上的s11,s12参数的实部和虚部,和使用本发明方法得到的不同频点上的s11,s12参数的实部和虚部之间误差较小。说明本发明通过简单的测试结构,可以较高精度地去除器件测试结构中的嵌入寄生效应。

[0068]

需要说明的是上述实施例,并非用来限定本发明的保护范围,在上述技术方案的基础上所作出的等同变换或替代均落入本发明权利要求所保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1