BMC记录系统异常信息的方法、系统、终端及存储介质与流程

bmc记录系统异常信息的方法、系统、终端及存储介质

技术领域

1.本发明涉及服务器技术领域,具体涉及一种bmc记录系统异常信息的方法、系统、终端及存储介质。

背景技术:

2.bmc作为服务器基板管理控制器,本身是一个arm架构的soc,内部有主控制器,协处理器。它除了有各种基本的计算机外围设备,还有用于和主板cpu交互的专用接口,比如peci,lpc,fantach,mailbox等。

3.bmc的软件在这个芯片上运行linux系统,实现了丰富的特性,提升管理效率,有效降低运营成本。常见的功能有:支持ipmi/https/redfish管理接口,故障监控和诊断,基于web界面的用户接口,设备资产管理,安全管理,电源管理等。

4.故障监控和诊断功能主要是提供告警和系统日志。显示主板电源故障,cpu的内核温度,电压硬盘故障,风扇转速及温度故障,mce/aer错误,系统电源故障,总线故障,系统宕机故障等。同时提供对cpu,内存,网卡和硬盘等各类部件的信息查询。对错误日志,部件信息实现一键收集辅助问题定位。

5.这些系统错误日志多是基于硬件的,缺少对主机os的运行错误的记录。主机的os运行错误崩溃后往往会自动重启,os自带的log记录会被覆盖,不利于用户便捷的定位问题。如果bmc软件能提供一些获取os异常信息的功能,将会给用户带来便捷。服务器主机上运行各种复杂的软件,难免会出现内核崩溃情况。linux系统提供了kernel panic机制来处理。操作系统监测到内部致命错误并无法安全处理该错误时,kernel尽可能的把能获取的信息记录下来并存储到磁盘某个位置,然后系统会重启。记录这些错误信息的文件有大小的限制,在系统重启之后有的会被覆盖,不利于定位问题。

技术实现要素:

6.针对现有技术的上述不足,本发明提供一种bmc记录系统异常信息的方法、系统、终端及存储介质,以解决上述技术问题。

7.第一方面,本发明提供一种bmc记录系统异常信息的方法,包括:

8.基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路;

9.通过诊断程序实时读取并缓存操作系统的异常信息;

10.将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。

11.进一步的,基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路,包括:

12.基于pcie通信控制器在基板管理控制器创建pcie接口;

13.在系统主板的pcie接口与基板管理控制器的pcie接口之间建立连接。

14.进一步的,通过诊断程序实时读取并缓存操作系统的异常信息,包括:

15.通过诊断程序读取操作系统的错误日志以及各应用软件的后台错误数据,将所述错误日志和所述后台错误数据缓存至指定路径下。

16.进一步的,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器,包括:

17.按照设定的间隔时间,定期通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径。

18.进一步的,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器,包括:

19.在系统故障后的重启阶段,通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径,以使基板管理控制器存储所述异常信息或将所述异常信息发送至监控终端。

20.第二方面,本发明提供一种bmc记录系统异常信息的系统,包括:

21.通信建立单元,用于基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路;

22.异常采集单元,用于通过诊断程序实时读取并缓存操作系统的异常信息;

23.异常发送单元,用于将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。

24.进一步的,所述通信建立单元用于:

25.基于pcie通信控制器在基板管理控制器创建pcie接口;

26.在系统主板的pcie接口与基板管理控制器的pcie接口之间建立连接。

27.进一步的,所述异常采集单元用于:

28.通过诊断程序读取操作系统的错误日志以及各应用软件的后台错误数据,将所述错误日志和所述后台错误数据缓存至指定路径下。

29.进一步的,异常发送单元用于:

30.按照设定的间隔时间,定期通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径。

31.进一步的,异常发送单元用于:

32.在系统故障后的重启阶段,通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径,以使基板管理控制器存储所述异常信息或将所述异常信息发送至监控终端。

33.第三方面,提供一种终端,包括:

34.处理器、存储器,其中,

35.该存储器用于存储计算机程序,

36.该处理器用于从存储器中调用并运行该计算机程序,使得终端执行上述的终端的方法。

37.第四方面,提供了一种计算机存储介质,所述计算机可读存储介质中存储有指令,当其在计算机上运行时,使得计算机执行上述各方面所述的方法。

38.本发明的有益效果在于,本发明提供的bmc记录系统异常信息的方法、系统、终端及存储介质,基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的

pcie通信链路,通过诊断程序实时读取并缓存操作系统的异常信息,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。本发明令bmc可以和系统主板有更多交互,实现了系统异常信息的可塑性,对于主机异常不能启动的情况下,提供了更多的收集信息的手段,便于用户定位问题。

39.此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

附图说明

40.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

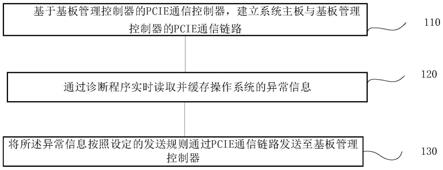

41.图1是本发明一个实施例的方法的示意性流程图。

42.图2是本发明一个实施例的方法的示意性功能架构图。

43.图3是本发明一个实施例的系统的示意性框图。

44.图4为本发明实施例提供的一种终端的结构示意图。

具体实施方式

45.为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

46.下面对本发明中出现的关键术语进行解释。

47.bmc,执行伺服器远端管理控制器,英文全称为baseboard management controller.为基板管理控制器。它可以在机器未开机的状态下,对机器进行固件升级、查看机器设备、等一些操作。在bmc中完全实现ipmi功能需要一个功能强大的16位元或32位元微控制器以及用于数据储存的ram、用于非挥发性数据储存的快闪记忆体和韧体,在安全远程重启、安全重新上电、lan警告和系统健康监视方面能提供基本的远程可管理性。除了基本的ipmi功能和系统工作监视功能外,通过利用2个快闪记忆体之一储存以前的bios,mbmc还能实现bios快速元件的选择和保护。例如,在远程bios升级後系统不能启动时,远程管理人员可以切换回以前工作的bios映像来启动系统。一旦bios升级後,bios映像还能被锁住,可有效防止病毒对它的侵害。

48.i2c总线是由philips公司开发的一种简单、双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送信息。主器件用于启动总线传送数据,并产生时钟以开放传送的器件,此时任何被寻址的器件均被认为是从器件.在总线上主和从、发和收的关系不是恒定的,而取决于此时数据传送方向。如果主机要发送数据给从器件,则主机首先寻址从器件,然后主动发送数据至从器件,最后由主机终止数据传送;如果主机要接收从器件的数据,首先由主器件寻址从器件.然后主机接收从器件发送的数据,最后由主机终止接收过程。在这种情况下.主机负责产生定时时钟和终止数据传送。

49.bios是英文"basic input output system"的缩略词,直译过来后中文名称就是"

基本输入输出系统"。在ibm pc兼容系统上,是一种业界标准的固件接口。它是一组固化到计算机内主板上一个rom芯片上的程序,它保存着计算机最重要的基本输入输出的程序、开机后自检程序和系统自启动程序,它可从cmos中读写系统设置的具体信息。其主要功能是为计算机提供最底层的、最直接的硬件设置和控制。此外,bios还向作业系统提供一些系统参数。系统硬件的变化是由bios隐藏,程序使用bios功能而不是直接控制硬件。现代作业系统会忽略bios提供的抽象层并直接控制硬件组件。

50.cpu中央处理器(central processing unit,简称cpu)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。

51.pci-express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3gio”,是由英特尔在2001年提出的,旨在替代旧的pci,pci-x和agp总线标准。pcie属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(qos)等功能。pcie交由pci-sig(pci特殊兴趣组织)认证发布后才改名为“pci-express”,简称“pci-e”。它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。pci express也有多种规格,从pci expressx1到pci express x32,能满足将来一定时间内出现的低速设备和高速设备的需求。pci-express的接口是pcie 3.0接口,其比特率为8gbps,约为上一代产品带宽的两倍,并且包含发射器和接收器均衡、pll改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。pcie闪存卡的供应商包括:intel、ibm、lsi、ocz、三星(计划中)、sandisk、stec、supertalent和东芝(计划中)等,而针对海量的数据增长使得用户对规模更大、可扩展性更强的系统所应用,pcie 3.0技术的加入最新的lsi megaraid控制器及hba产品的出色性能,就可以实现更大的系统设计灵活性。

52.图1是本发明一个实施例的方法的示意性流程图。其中,图1执行主体可以为一种bmc记录系统异常信息的系统。

53.如图1所示,该方法包括:

54.步骤110,基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路;

55.步骤120,通过诊断程序实时读取并缓存操作系统的异常信息;

56.步骤130,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。

57.为了便于对本发明的理解,下面以本发明bmc记录系统异常信息的方法的原理,结合实施例中对系统异常信息进行记录的过程,对本发明提供的bmc记录系统异常信息的方法做进一步的描述。

58.具体的,请参考图2,所述bmc记录系统异常信息的方法包括:

59.s1、基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路。

60.基于pcie通信控制器在基板管理控制器创建pcie接口;在系统主板的pcie接口与基板管理控制器的pcie接口之间建立连接。

61.以bmc芯片aspeed2500内部的x-dma控制器为基础。该控制器可以通过pcie总线在

主机内存和bmc内存之间传递数据。常见的bmc芯片内部有dma控制器,通过内部总线对外提供了pcie gen2接口。这样在物理上可以链接host端的pcie总线,实现主机系统主板和bmc之间的数据传递。芯片内部提供了host,bmc端访问的基址存储在寄存器内。驱动软件方面,linux内核drivers/soc/aspeed目录下有几个模块,其中aspeed-xdma.c中提供了完整的驱动程序。加载完驱动后,可根据应用设计上层接口。

62.驱动程序完成初始化后,提供给主板端用户的读写操作接口。用户读写操作可采用poll模式或者中断模式,不同的方法提供了不同的接口。系统主板的上层用户应用程序打开xdma设备,通过aspeed_xdma_write向bmc写数据,aspeed_xdma_poll从bmc读数据。

63.s2、通过诊断程序实时读取并缓存操作系统的异常信息。

64.通过诊断程序读取操作系统的错误日志以及各应用软件的后台错误数据,将所述错误日志和所述后台错误数据缓存至指定路径下。

65.具体的,服务器上运行系统应用,不同的应用根据自己的需要开发用户程序作为诊断程序。授予诊断程序的运行权限以及开机自启权限。

66.s3、将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。

67.按照设定的间隔时间,定期通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径。或者在系统故障后的重启阶段,通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径,以使基板管理控制器存储所述异常信息或将所述异常信息发送至监控终端。

68.系统发生异常时,用户程序获取异常记录并写pcie设备,通过ddr控制器把信息写到ddr(内存)或者flash上。待系统重启后,通过读pcie设备,用户程序把保存在ddr中的信息获取并解析。如果系统不能正常启动,存在ddr或者flash上的信息可以在bmc侧导出。用户程序也可以定时写入系统的日志信息到bmc的ddr中,当应用发生异常时系统侧应用程序调用读接口获取信息或者bmc侧读取运行日志。

69.本实施例提供的bmc记录系统异常信息的方法,基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路,通过诊断程序实时读取并缓存操作系统的异常信息,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。本发明令bmc可以和系统主板有更多交互,实现了系统异常信息的可塑性,对于主机异常不能启动的情况下,提供了更多的收集信息的手段,便于用户定位问题。

70.鉴于操作系统监测到内部致命错误并无法安全处理该错误时,kernel尽可能的把能获取的信息记录下来并存储到磁盘某个位置,然后系统会重启。记录这些错误信息的文件有大小的限制,在系统重启之后有的会被覆盖,不利于定位问题。本实施例就是提出一种系统,在系统崩溃时候,用户的应用程序把日志信息发送到bmc的存储空间里,待系统重启之后可以从bmc读取来查看,或者直接在bmc上导出查看。

71.如图3所示,该系统300包括:

72.通信建立单元310,用于基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路;

73.异常采集单元320,用于通过诊断程序实时读取并缓存操作系统的异常信息;

74.异常发送单元330,用于将所述异常信息按照设定的发送规则通过pcie通信链路

发送至基板管理控制器。

75.可选地,作为本发明一个实施例,所述通信建立单元用于:

76.基于pcie通信控制器在基板管理控制器创建pcie接口;

77.在系统主板的pcie接口与基板管理控制器的pcie接口之间建立连接。

78.在实际应用中,以bmc芯片aspeed2500内部的x-dma控制器为基础。该控制器可以通过pcie总线在主机内存和bmc内存之间传递数据。常见的bmc芯片内部有dma控制器,通过内部总线对外提供了pcie gen2接口。这样在物理上可以链接host端的pcie总线,实现主机系统主板和bmc之间的数据传递。芯片内部提供了host,bmc端访问的基址存储在寄存器内。驱动软件方面,linux内核drivers/soc/aspeed目录下有几个模块,其中aspeed-xdma.c中提供了完整的驱动程序。加载完驱动后,可根据应用设计上层接口。驱动程序完成初始化后,提供给主板端用户的读写操作接口。用户读写操作可采用poll模式或者中断模式,不同的方法提供了不同的接口。系统主板的上层用户应用程序打开xdma设备,通过aspeed_xdma_write向bmc写数据,aspeed_xdma_poll从bmc读数据。

79.可选地,作为本发明一个实施例,所述异常采集单元用于:

80.通过诊断程序读取操作系统的错误日志以及各应用软件的后台错误数据,将所述错误日志和所述后台错误数据缓存至指定路径下。

81.服务器上运行系统应用,不同的应用根据自己的需要开发用户程序作为诊断程序。授予诊断程序的运行权限以及开机自启权限。

82.可选地,作为本发明一个实施例,异常发送单元用于:

83.按照设定的间隔时间,定期通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径。

84.这种方式可以实现数据的及时备份,同时也可实现用户从bmc实时调取异常信息,在一些异常信息不会造成系统崩溃等严重问题时也能够进行查看。

85.可选地,作为本发明一个实施例,异常发送单元用于:

86.在系统故障后的重启阶段,通过pcie通信链路将异常信息发送至预先存储的基板管理控制器存储路径,以使基板管理控制器存储所述异常信息或将所述异常信息发送至监控终端。

87.系统发生异常时,用户程序获取异常记录并写pcie设备,通过ddr控制器把信息写到ddr(内存)或者flash上。待系统重启后,通过读pcie设备,用户程序把保存在ddr中的信息获取并解析。如果系统不能正常启动,存在ddr或者flash上的信息可以在bmc侧导出。

88.本发明令bmc可以和系统主板有更多交互,实现了系统异常信息的可塑性,对于主机异常不能启动的情况下,提供了更多的收集信息的手段,便于用户定位问题。

89.图4为本发明实施例提供的一种终端400的结构示意图,该终端400可以用于执行本发明实施例提供的bmc记录系统异常信息的方法。

90.其中,该终端400可以包括:处理器410、存储器420及通信单元430。这些组件通过一条或多条总线进行通信,本领域技术人员可以理解,图中示出的服务器的结构并不构成对本发明的限定,它既可以是总线形结构,也可以是星型结构,还可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

91.其中,该存储器420可以用于存储处理器410的执行指令,存储器420可以由任何类

型的易失性或非易失性存储终端或者它们的组合实现,如静态随机存取存储器(sram),电可擦除可编程只读存储器(eeprom),可擦除可编程只读存储器(eprom),可编程只读存储器(prom),只读存储器(rom),磁存储器,快闪存储器,磁盘或光盘。当存储器420中的执行指令由处理器410执行时,使得终端400能够执行以下上述方法实施例中的部分或全部步骤。

92.处理器410为存储终端的控制中心,利用各种接口和线路连接整个电子终端的各个部分,通过运行或执行存储在存储器420内的软件程序和/或模块,以及调用存储在存储器内的数据,以执行电子终端的各种功能和/或处理数据。所述处理器可以由集成电路(integrated circuit,简称ic)组成,例如可以由单颗封装的ic所组成,也可以由连接多颗相同功能或不同功能的封装ic而组成。举例来说,处理器410可以仅包括中央处理器(central processing unit,简称cpu)。在本发明实施方式中,cpu可以是单运算核心,也可以包括多运算核心。

93.通信单元430,用于建立通信信道,从而使所述存储终端可以与其它终端进行通信。接收其他终端发送的用户数据或者向其他终端发送用户数据。

94.本发明还提供一种计算机存储介质,其中,该计算机存储介质可存储有程序,该程序执行时可包括本发明提供的各实施例中的部分或全部步骤。所述的存储介质可为磁碟、光盘、只读存储记忆体(英文:read-only memory,简称:rom)或随机存储记忆体(英文:random access memory,简称:ram)等。

95.因此,本发明基于基板管理控制器的pcie通信控制器,建立系统主板与基板管理控制器的pcie通信链路,通过诊断程序实时读取并缓存操作系统的异常信息,将所述异常信息按照设定的发送规则通过pcie通信链路发送至基板管理控制器。本发明令bmc可以和系统主板有更多交互,实现了系统异常信息的可塑性,对于主机异常不能启动的情况下,提供了更多的收集信息的手段,便于用户定位问题,本实施例所能达到的技术效果可以参见上文中的描述,此处不再赘述。

96.本领域的技术人员可以清楚地了解到本发明实施例中的技术可借助软件加必需的通用硬件平台的方式来实现。基于这样的理解,本发明实施例中的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中如u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质,包括若干指令用以使得一台计算机终端(可以是个人计算机,服务器,或者第二终端、网络终端等)执行本发明各个实施例所述方法的全部或部分步骤。

97.本说明书中各个实施例之间相同相似的部分互相参见即可。尤其,对于终端实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例中的说明即可。

98.在本发明所提供的几个实施例中,应该理解到,所揭露的系统和方法,可以通过其它的方式实现。例如,以上所描述的系统实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,系统或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

99.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

100.另外,在本发明各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

101.尽管通过参考附图并结合优选实施例的方式对本发明进行了详细描述,但本发明并不限于此。在不脱离本发明的精神和实质的前提下,本领域普通技术人员可以对本发明的实施例进行各种等效的修改或替换,而这些修改或替换都应在本发明的涵盖范围内/任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应所述以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1