用于编码和解码的装置和方法与流程

用于编码和解码的装置和方法

1.相关申请的交叉引用

2.本技术基于并要求于2021年3月10日在韩国知识产权局提交的韩国专利申请no.10-2021-0031486和于2021年5月31日在韩国知识产权局提交的韩国专利申请no.10-2021-0070262的优先权,这些申请的公开内容通过引用整体结合于此。

技术领域

3.本发明构思涉及装置和方法,并且更具体地,涉及用于编码和解码以实现具有最小开销的最大转换避免编码(maximum transition avoidance coding)的装置和方法。

背景技术:

4.使计算系统更强大并且更功率高效的努力可导致开发接口通信并在不增加功耗的情况下提高吞吐量,同时降低理想情况下的功耗。传统的系统是用脉冲幅度调制4电平(pam-4)信令来实现的。pam-4用于将2比特流转换为具有4电平的单个多电平信号。pam-4信令系统可使用最大转换避免(mta)编码以用于去除接口线上的pam-4符号之间的最大电压转换。mta编码可减少会导致信号失真的符号间干扰(isi)和串扰。

5.在由计算系统执行的各种操作中,用于数据写入和/或读取的存储器访问操作是重要的。至少部分地基于存储器的输入/输出结构来执行存储器访问操作,并且当存储器带宽增加到32比特或更多时,可通过使用数据调制方法来访问存储器。例如,当使用pam-4信令时,由于mta编码所需的信号线的数量的增加和/或芯片面积的增加,可能产生大的开销。因此,需要一种通过使用应用了mta的pam-4信令以最小开销实现的用于收发32比特数据的装置和方法。

技术实现要素:

6.本发明构思提供了一种用于编码和解码的装置和方法,以实现具有最小开销的最大转换避免编码。

7.该装置包括用于数据总线的发送器,其中,发送器包括编码器,编码器被配置为将要被传送至数据总线的数据突发转换为由符号构成的码字。编码器包括表示数据突发和符号之间的相关性的逻辑电路。逻辑电路包括:根据码字映射的数量被分类的多个子块查找表,其中,码字映射表示数据突发中的一些比特值与符号之间的相关性;以及组合查找表,其基于数据突发的每一个中的其余比特值,根据多个子块查找表选择性地互连编码结果。编码器被配置为通过使用组合查找表和多个子块查找表将与数据突发对应的码字提供给数据总线。

8.一种发送数据的方法包括:接收要被发送至数据线的m(m是自然数)比特的数据突发;将m比特的数据突发中的p(p为自然数并且m>p)比特的值发送至数据总线反相(dbi)信号线;通过对q比特执行q:(q+k)(q是自然数,k是等于或大于1的自然数)比特编码来生成dbi信号线的码字,其中q比特是dbi信号线上的p比特的总和;以及通过对数据突发中的每

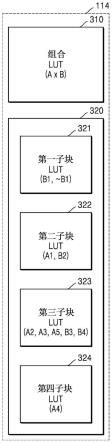

一个的其余(m-p)比特执行(m-p):m比特编码来生成数据线的码字。

9.一种包括用于数据总线的接收器的装置,其中,接收器包括解码器,解码器被配置为将由通过数据总线接收的符号构成的码字转换为数据突发。解码器包括表示符号与数据突发之间的相关性的逻辑电路。逻辑电路包括:码字解码查找表,其被配置为提供查找表映射,查找表映射指定与码字中的每一个的符号对应的多个子块查找表;根据码字映射的数量对多个子块查找表进行分类,其中,码字映射表示符号与数据突发中的一些比特值之间的相关性;以及组合查找表,其基于由查找表映射指定的子块查找表的组合,选择性地互连多个子块查找表。解码器通过使用码字解码查找表、多个子块查找表和组合查找表来恢复与码字对应的数据突发。

附图说明

10.从以下结合附图的详细描述中,本发明构思的实施例将被更清楚地理解,在附图中:

11.图1是根据实施例的发送器和接收器的示意性框图;

12.图2是由图1中的pam-4编码器使用的7:8比特编码的示图;

13.图3是用于解释图1中的pam-4编码器的查找表的示图;

14.图4和图5a至图5c是使用组合查找表和子块查找表的码字编码的示图;

15.图6是图1中的pam-4编码器的操作方法的流程图;

16.图7是图1中的pam-4解码器的查找表的示图;

17.图8是图7中的码字解码查找表的示图;

18.图9是图1中的pam-4解码器的操作方法的流程图;

19.图10是通过使用图2的7:8比特编码的32比特的数据突发的编码方法的示图;

20.图11是用于解释根据实施例的数据突发的编码方法的曲线图;

21.图12至图14是根据图11的编码方法的32比特的数据突发结构的示图;

22.图15是根据实施例的包括编码装置和解码装置的存储器系统的第一示例的框图;

23.图16是根据实施例的存储器装置的一部分的框图;以及

24.图17是根据实施例的包括编码装置和解码装置的存储器系统的第二示例的框图。

具体实施方式

25.图1是根据实施例的发送器110和接收器120的示意性框图。

26.参照图1,接收器120可经由信道线130与发送器110通信。信道线130可包括多条信号线,多条信号线将发送器110物理地或电气地连接到接收器120。发送器110、接收器120和信道线130可支持pam-4信令,pam-4信令将2比特流转换为具有4电平的单个多电平信号。

27.发送器110可包括pam-4编码器112,用于将待发送至接收器120的数据突发转换成pam-4符号。pam-4编码器112可对数据突发执行编码并生成pam-4符号。发送器110还可包括用于驱动信道线130的pam-4符号的驱动器。发送器110可经由信道线130将pam-4符号发送至接收器120。

28.pam-4编码器112可包括表示数据突发与pam-4符号之间的相关性的逻辑电路114。逻辑电路114可包括被配置为具有最小开销的查找表。查找表可实现为存储数据突发和

pam-4符号之间的相关性的寄存器(或存储元件)。pam-4编码器112可使用查找表并将数据突发转换成pam-4符号。

29.接收器120可接收pam-4符号,并且可包括用于对接收的pam-4符号进行解码的pam-4解码器122。pam-4解码器122可包括被配置为对pam-4符号进行解码并且恢复2比特流的数据突发的逻辑电路124。逻辑电路124可包括被配置为对pam-4符号进行解码并且恢复2比特流的数据突发的查找表。查找表可实现为存储pam-4符号与数据突发之间的相关性的寄存器。pam-4解码器122可使用查找表并将pam-4符号恢复到数据突发。pam-4解码器122的查找表的一部分可被配置为与pam-4编码器112的查找表相同。

30.图2是由图1中的pam-4编码器112使用的7:8比特编码的示图。

31.参照图2,示出了用户数据202和经编码的数据204之间的7:8比特编码200。用户数据202可被称为原始数据。对于用户数据202和经编码的数据204,每个dq[i]行可表示串行数据线。

[0032]

在用户数据202中,16比特的数据突发可布置在每条串行数据线或每个dq[i]行上,并且列可包括16比特的数据突发中的顺序的2比特的位置。例如,每个数据突发的第二比特和第三比特可由被标记为列的d[2:3]表示。每个16比特的数据突发可由两个半个数据突发表示,每半个数据突发包括8比特。例如,在串行数据线dq[0]上,16比特的数据突发可被划分成第一半数据突发(或d0[0]:d0[7:1])和第二半数据突发(或d0[8]:d0[15:9])。每半个数据突发还可被划分成一对1比特:7比特。例如,在串行数据线dq[0]上,第一半数据突发或d0[0]:d0[7:1]可被划分成1比特值的d0[0]和7比特值的d0[7:1]。

[0033]

在经编码的数据204中,dq[i]行可表示串行数据线,数据总线反相(dbi)行可表示dbi信号线,并且它们的列可包括表示符号s[i]的比特串。例如,s[0]可表示每条串行数据线上的第一2比特的pam-4符号,并且s[1]可表示第二2比特的pam-4符号。

[0034]

7:8比特编码200可将在任何1条串行数据线上的任何比特位置处的一对1比特的数据值编码为dbi信号线上的pam-4符号。例如,串行数据线dq[0]上的数据d0[0]和d0[8]可被编码为dbi信号线上的2比特的pam-4符号,而串行数据线dq[1]上的数据d1[0]和数据d1[8]可被编码为dbi信号线上的2比特的pam-4符号。

[0035]

根据实施例,在7:8比特编码200中,dbi信号线上的2比特的pam-4符号可将其它串行数据线上的一对1比特的数据值编码为dbi信号线上的pam-4符号。例如,串行数据线dq[0]的数据d0[0]和串行数据线dq[1]的数据d1[0]可被编码为dbi信号线上的2比特的pam-4符号。类似地,串行数据线dq[2]的数据d2[0]和串行数据线dq[3]的数据d3[0]可被编码为dbi信号线上的2比特的pam-4符号。

[0036]

在7:8比特编码200中,第一半数据突发和第二半数据突发中的每一个中的未被用作的dbi信号线的pam-4符号的剩余7比特可被编码为与其对应的串行数据线上的4个pam-4符号。该4个pam-4符号可具有8比特,并且可被称为码字。例如,用户数据d0[7:1]可被编码为串行数据线dq[0]上的码字c0[7:0]。用于用户数据的每7比特的码字可被表示为pam-4符号中的4个pam-4符号。用户数据d0[7:1]可被编码为码字c0[7:0],码字c0[7:0]包括符号s[0]、s[1]、s[2]和s[3]。

[0037]

在7:8比特编码200中,串行数据线dq[i]中的每一条上的用于第一半数据突发中的7比特的码字ci[7:0]和串行数据线dq[i]中的每一条上的用于第二半数据突发中的7比

特的码字ci[15:8]之间的空间可被称为块边界(bb)。

[0038]

7:8比特编码200可通过使用查找表将7比特的数据值映射到与其对应的码字。如图3所示,查找表可包括组合查找表(lut)310和包括多个子块lut 321至324的lut集320。组合lut 310可根据多个子块lut 321至324选择性地互连编码结果。

[0039]

另一方面,在7:8比特编码200中,根据pam-4符号s[0]、s[1]、s[2]和s[3]的8比特编码,可存在256个模式,并且可从256个模式中选择128个模式用于用户数据的7比特编码。可将选择的128个模式提供至7比特的用户数据的码字。查找表中的与未被选择的128个模式相关的寄存器可不被使用,并且可用作查找表的开销。

[0040]

在以下描述的实施例中,为了减少查找表的开销,多个子块lut 321至324被布置为彼此相邻(即,互连)以构成1个lut集320。子块lut 321至324中的每一个可包括多个子块lut a1至a5、b1至b4以及~b1,这些子块根据码字映射的数量被分类。组合lut 310可由lut映射构成,lut映射根据7比特的用户数据值的类型选择性地组合子块lut a1至a5、b1至b4以及~b1。lut可被构造为支持mta,并且将参照图1描述pam-4符号与符号比特之间的映射。表1是用于描述的目的非限制性示例。

[0041]

[表1]

[0042][0043]

参照表1,2比特的pam-4符号可经由信道线(图1中的130)被发送至表示为0、1、2或3的4个电压电平。作为示例,可将电平3的pam-4符号设置为最高电压电平,并且可将电平0的pam-4符号设置为最低电压电平。

[0044]

图3是图1中的pam-4编码器112的查找表的示图,并且图4和图5a至图5c是使用图3中的组合lut 310和子块lut a1至a5、b1至b4以及~b1的码字编码的示图。图3至图5c描述了由7:8比特编码器和/或解码器使用的lut,然而这些实施例是出于描述目的的非限制性示例。根据实施例,可通过使用图3到图5c中的lut来实现29:32比特编码器和/或解码器。

[0045]

参照图3,pam-4编码器112的逻辑电路114可包括组合lut 310以及在lut集320内部互连的第一子块lut 321、第二子块lut 322、第三子块lut 323和第四子块lut 324。第一子块lut 321可包括包含最大数量的码字映射(例如,8个码字映射)的子块lut b1和子块lut~b1。子块lut~b1可被配置为提供相对于子块lut b1反转的码字映射。子块lut~b1可被配置为支持要组合的子块lut中的码字的最后1个符号和第一个符号之间的mta。第二子块lut 322可包括例如各自包含4个码字映射的子块lut a1和子块lut b2。第三子块lut 323可包括例如各自包含两个码字映射的子块lut a2、子块lut a3、子块lut a5、子块lut b3和子块lut b4。第四子块lut 324可包括例如包含1个码字映射的子块lut a4。参照图5a至图5c详细描述了子块lut a1至a5、b1至b4以及~b1。

[0046]

参照图3和图4,组合lut 310可设置子块lut a1至a5、b1至b4以及~b1,这些子块根据用户数据b[6:0]的类型被组合,以提供与7比特的用户数据b[6:0]对应的码字映射。用

户数据b[6:0]可对应于参照图2描述的半个数据突发的用户数据d0[7:1]。

[0047]

作为示例,当7比特的用户数据b[6:0]的b5:b6比特值是00时,子块lut a1和子块lut b1可被设置为组合。子块lut a1可提供与b0:b1比特值对应的码字映射。子块lut a1可包括对应于2比特的4个码字映射,并且可被包括在第二子块lut 322中。子块lut b1可提供与b2:b3:b4比特值对应的码字映射。子块lut b1可包括对应于3比特的8个码字映射,并且可被包括在第一子块lut 321中。因此,可提供由与7比特的用户数据b[6:0]的b5:b6比特值(或00)对应的组合符号编码a1

×

b1构成的32(4

×

8=32)个码字。

[0048]

作为示例,当7比特的用户数据b[6:0]的b4:b5:b6比特值是001时,子块lut a1和子块lut b2可被设置为组合。子块lut a1可提供与b0:b1比特值对应的码字映射。子块lut b2可提供与b2:b3比特值对应的码字映射。子块lut b2可包括对应于2比特的4个码字映射,并且可被包括在第二子块lut 322中。因此,可提供由与7比特的用户数据b[6:0]的b4:b5:b6比特值(或001)对应的组合符号编码a1

×

b2构成的16(4

×

4=16)个码字。

[0049]

当7比特的用户数据b[6:0]的b4:b5:b6比特值是101时,子块lut a2和子块lut b1可被设置为组合。子块lut a2可提供与b0比特值对应的码字映射。子块lut a2可包括与1比特对应的两个码字映射,并且可被包括在第三子块lut 323中。子块lut b1可提供与b1:b2:b3比特值对应的码字映射。因此,可提供由与7比特的用户数据b[6:0]的b4:b5:b6比特值(或101)对应的组合符号编码a2

×

b1构成的16(2

×

8=16)个码字。

[0050]

当7比特的用户数据b[6:0]的b4:b5:b6比特值是010时,子块lut a3和子块lut b1可被设置为组合。子块lut a3可提供与b0比特值对应的码字映射。子块lut a3可包括与1比特对应的两个码字映射,并且可被包括在第三子块lut 323中。子块lut b1可提供与b1:b2:b3比特值对应的码字映射。因此,可提供由与7比特的用户数据b[6:0]的b4:b5:b6比特值(或010)对应的组合符号编码a3

×

b1构成的16(2

×

8=16)个码字。

[0051]

当7比特的用户数据b[6:0]的b4:b5:b6比特值是110时,子块lut a5和子块lut~b1可被设置为组合。子块lut a5可提供与b0比特值对应的码字映射。子块lut a5可包括与1比特对应的两个码字映射,并且可被包括在第三子块lut 323中。子块lut~b1可提供与b1:b2:b3比特值对应的码字映射。子块lut~b1可包括与3比特对应的8个码字映射,并且可被包括在第一子块lut 321中。因此,可提供由与7比特的用户数据b[6:0]的b4:b5:b6比特值(或110)对应的组合符号编码a5

×

~b1构成的16(2

×

8=16)个码字。

[0052]

作为示例,当7比特的用户数据b[6:0]的b3:b4:b5:b6比特值是0011时,子块lut a1和子块lut b3可被设置为组合。子块lut a1可提供与b0:b1比特值对应的码字映射。子块lut b3可提供与b2比特值对应的码字映射。子块lut b3可包括与1比特对应的两个码字映射,并且可被包括在第三子块lut 323中。因此,可提供由与7比特的用户数据b[6:0]的b3:b4:b5:b6比特值(或0011)对应的组合符号编码a1

×

b3构成的8(4

×

2=8)个码字。

[0053]

作为示例,当7比特的用户数据b[6:0]的b3:b4:b5:b6比特值是1011时,子块lut a2和子块lut b2可被设置为组合。子块lut a2可提供与b0比特值对应的码字映射。子块lut b2可提供与b1:b2比特值对应的码字映射。因此,可提供由与7比特的用户数据b[6:0]的b3:b4:b5:b6比特值(或1011)对应的组合符号编码a2

×

b2构成的8(2

×

4=8)个码字。

[0054]

作为示例,当7比特的用户数据b[6:0]的b3:b4:b5:b6比特值是0111时,子块lut a4和子块lut b1可被设置为组合。子块lut a4可包括1个码字映射,并且可被包括在第四子

块lut 324中。子块lut b1可提供与b0:b1:b2比特值对应的码字映射。因此,可提供由与7比特的用户数据b[6:0]的b3:b4:b5:b6比特值(或0111)对应的组合符号编码a4

×

b1构成的8(1

×

8=8)个码字。

[0055]

作为示例,当7比特的用户数据b[6:0]的b2:b3:b4:b5:b6比特值是01111时,子块lut a2和子块lut b3可被设置为组合。子块lut a2可提供与b0比特值对应的码字映射。子块lut b3可提供与b1比特值对应的码字映射。因此,可提供由与7比特的用户数据b[6:0]的b2:b3:b4:b5:b6比特值(或01111)对应的组合符号编码a2

×

b3构成的4(2

×

2=4)个码字。

[0056]

当7比特的用户数据b[6:0]的b2:b3:b4:b5:b6比特值是11111时,子块lut a3和子块lut b4可被设置为组合。子块lut a3可提供与b0比特值对应的码字映射。子块lut b4可提供与b1比特值对应的码字映射。子块lut b4可包括与1比特对应的两个码字映射,并且可被包括在第三子块lut 323中。因此,可提供由与7比特的用户数据b[6:0]的b2:b3:b4:b5:b6比特值(或11111)对应的组合符号编码a3

×

b4构成的4(2

×

2=4)个码字。

[0057]

参照图5a,子块lut a1和子块lut a2中的每一个可选择性地与子块lut b1、子块lut b2和子块lut b3组合。可执行码字编码,使得当2比特值为00时,子块lut a1被转换为符号电平01,当2比特值为01时,子块lut a1被转换为符号电平11,当2比特值为10时,子块lut a1被转换为符号电平02,并且当2比特值为11时,子块lut a1被转换为符号电平21。可执行码字编码,使得当1比特值为0时,子块lut a2被转换为符号电平12,并且当1比特值为1时,子块lut a2被转换为符号电平22。子块查找表a1和a2可被配置为第一个符号电平0、1或2与最后1个符号电平1或2的组合。

[0058]

可执行码字编码,使得当3比特值为000时,子块lut b1被转换为符号电平00,当3比特值为001时,子块lut b1被转换为符号电平01,当3比特值为010时,子块lut b1被转换为符号电平10,当3比特值为011时,子块lut b1被转换为符号电平11,当3比特值为100时,子块lut b1被转换为符号电平02,当3比特值为101时,子块lut b1被转换为符号电平20,当3比特值为110时,子块lut b1被转换为符号电平21,并且当3比特值为111时,子块lut b1被转换为符号电平12。可执行码字编码,使得当2比特值为00时,子块lut b2被转换为符号电平22,当2比特值为01时,子块lut b2被转换为符号电平31,当2比特值为10时,子块lut b2被转换为符号电平13,并且当2比特值为11时,子块lut b2被转换为符号电平23。可执行码字编码,使得当1比特值是0时,子块lut b3被转换为符号电平32,并且当1比特值是1时,子块lut b3被转换为符号电平33。子块lut b1至lut b3可被配置为第一个符号电平0、1、2或3与最后1个符号电平0、1、2或3的组合。

[0059]

在图5a中,可支持mta,使得在子块lut a1和子块lut a2以及子块lut b1、子块lut b2和子块lut b3的每个码字中的符号之间,从电平0到电平3或者从电平3到电平0不发生最大转换(mt)事件。此外,可支持mta,使得mt事件不发生在子块lut a1和子块lut a2的码字的最后1个符号与子块lut b1、子块lut b2和子块lut b3的码字的第一个符号之间。

[0060]

参照图5b,子块lut a3和子块lut a4中的每一个可选择性地与子块lut b1和子块lut b4组合。可执行码字编码,使得当1比特值为0时,子块lut a3被转换为符号电平00,并且当1比特值为1时,子块lut a3被转换为符号电平10。子块lut a4可提供1个符号电平20。子块lut a3和子块lut a4可被配置为第一个符号电平0、1或2与最后1个符号电平0的组合。

[0061]

子块lut b1的配置可与参照图5a描述的相同。可执行码字编码,使得当1比特值为

0时,子块lut b4被转换为符号电平22,并且当1比特值为1时,子块lut b4被转换为符号电平13。子块lut b1和子块lut b4可被配置为第一个符号电平0、1或2与最后1个符号电平0、1、2或3的组合。

[0062]

在图5b中,子块lut a3和子块lut a4以及子块lut b1和子块lut b4可支持每个码字中的符号之间的mta。此外,可支持mta,使得mt事件不发生在子块lut a3和子块lut a4的码字的最后1个符号与子块lut b1和子块lut b4的码字的第一个符号之间。

[0063]

参照图5c,子块lut a5可选择性地与子块lut~b1组合。可执行码字编码,使得当1比特值为0时,子块lut a5被转换为符号电平13,并且当1比特值为1时,子块lut a5被转换为符号电平23。子块lut a5可被配置为第一个符号电平1或2与最后1个符号电平3的组合。

[0064]

子块lut~b1可提供其中参照图5a描述的子块lut b1的符号电平被反转的码字。可执行码字编码,使得当3比特值为000时,子块lut~b1被转换为符号电平33,当3比特值为001时,子块lut~b1被转换为符号电平32,当3比特值为010时,子块lut~b1被转换为符号电平23,当3比特值为011时,子块lut~b1被转换为符号电平22,当3比特值为100时,子块lut~b1被转换为符号电平31,当3比特值为101时,子块lut~b1被转换为符号电平13,当3比特值为110时,子块lut~b1被转换为符号电平12,并且当3比特值为111时,子块lut~b1被转换为符号电平21。子块lut~b1可被配置为第一个符号电平1、2或3与最后1个符号电平1、2或3的组合,并且其中可不存在符号电平0。原因在于,因为子块lut a5的最后1个符号电平为3,所以可通过从子块lut~b1的第一个符号电平中去除符号电平0来支持mta。

[0065]

参照图3至图5c,7比特的用户数据可被编码为码字。例如,当7比特的用户数据(或b0:b1:b2:b3:b4:b5:b6比特值)是0010000时,根据b5:b6比特值00,可从组合lut 310选择组合符号编码a1

×

b1。根据b0:b1比特值00,可选择子块lut a1的符号电平01,并且根据b2:b3:b4比特值100,可选择子块lut b1的符号电平02。因此,7比特的用户数据0010000可被转换为组合符号的码字0102。

[0066]

例如,如果假设7比特的用户数据的b0:b1:b2:b3:b4:b5:b6比特值是0101011。根据b3:b4:b5:b6比特值1011,可从组合lut 310选择组合符号编码a2

×

b2。根据b0比特值0,可选择子块lut a2的符号电平12,并且根据b1:b2比特值10,可选择子块lut b2的符号电平13。因此,7比特的用户数据0101011可被转换为组合符号的码字1213。

[0067]

例如,当7比特的用户数据(或b0:b1:b2:b3:b4:b5:b6比特值)是1101010时,根据b4:b5:b6比特值010,可从组合lut 310选择组合符号编码a3

×

b1。根据b0比特值1,可选择子块lut a3的符号电平10,并且根据b1:b2:b3比特值101,可选择子块lut b1的符号电平20。因此,7比特的用户数据1101010可被转换为组合符号的码字1020。

[0068]

例如,当7比特的用户数据(或b0:b1:b2:b3:b4:b5:b6比特值)是0000110时,根据b4:b5:b6比特值110,可从组合lut 310选择组合符号编码a5

×

~b1。根据b0比特值0,可选择子块lut a5的符号电平13,并且根据b1:b2:b3比特值000,可选择子块lut~b1的符号电平33。因此,7比特的用户数据0000110可被转换为组合符号的码字1333。

[0069]

图6是图1中的pam-4编码器的操作方法600的流程图。

[0070]

参照图6以及图1至图5c,pam-4编码器112可接收要被发送至串行数据线dq[i]的用户数据16比特的数据突发(s601)。pam-4编码器112可将16比特的数据突发划分成第一半数据突发(或d0[0]:d0[7:1])和第二半数据突发(或d0[8]:d0[15:9])(s602),并且将每半

b4,并且可表示与和子块lut a3或子块lut a4组合的子块lut b1和子块lut b4中的每一个对应的用户数据比特值。

[0080]

例如,可参照lut映射802将码字1020解码为7比特的用户数据比特。因为已经参照先前码字10指定子块lut a3,所以可将与子块lut a3对应的用户数据比特值设置为1。可参照lut映射802将当前码字20指定给与子块lut a3组合的子块lut b1,并且可将与子块lut b1对应的用户数据比特值设置为101。可将码字1020转换为用户数据比特值1101。可参照组合lut(图4中的310)将组合的子块lut a3

×

b1转换为用户数据比特值010。因此,可将码字1020恢复为其中将用户数据比特值1101和010组合的7比特的用户数据比特值1101010。

[0081]

lut映射803可表示与子块lut a5组合的子块lut~b1。

[0082]

例如,可参照lut映射803将码字1333解码为7比特的用户数据比特。当子块lut a5已经参照先前码字13被指定时,可将与子块lut a5对应的用户数据比特值设置为0。可参照lut映射803将当前码字33指定给与子块lut a5组合的子块lut~b1,并且可将与子块lut~b1对应的用户数据比特值设置为000。可将码字1333转换为用户数据比特值0000。可参照组合lut(图4中的310)将组合的子块lut a5

×

~b1转换为用户数据比特值110。因此,可将码字1333恢复为其中将用户数据比特值0000和110组合的7比特的用户数据比特值0000110。

[0083]

图9是图1中的pam-4解码器122的操作方法900的流程图。

[0084]

参照图9以及图1至图8,pam-4解码器122可经由串行数据线dq[i]接收码字(s901)。pam-4解码器122可执行8:7比特解码,使得码字被转换为7比特的用户数据(s902)。可通过使用码字解码lut 710、组合lut 310、以及在lut集320中互连的第一子块lut 321至第四子块lut 324来执行8:7比特解码。可通过8:7比特解码来生成与码字对应的7比特的用户数据。

[0085]

pam-4解码器122可经由dbi信号线接收pam-4符号的1比特的用户数据(s903),可通过将接收的1比特的用户数据与解码的用户数据组合来恢复第一半数据突发,并且可恢复用于串行数据线dq[i]的第二半数据突发(s904)。pam-4解码器122可通过将第一半数据突发与第二半数据突发组合来恢复完整的数据突发(s905)。

[0086]

图10是通过使用图2的7:8比特编码200的32比特的数据突发的编码方法的示图。

[0087]

参照图2和图10,32比特的数据突发可布置在每条串行数据线dq[i]上,并且32比特的数据突发中的每一个可表示4个8比特的四分之一数据突发。每个四分之一数据突发还可被划分为一对1比特:7比特,并且可通过执行参照图2描述的7:8比特编码200来支持mta。每个四分之一数据突发的1比特值可被编码到dbi信号线上的pam-4符号,并且当4个四分之一数据突发中的每一个的1比特在8条串行数据线dq[i]中的每一条上被发送至dbi信号线时,总共32比特可被发送至dbi信号线。

[0088]

为了也在dbi信号线上支持mta,32比特中的仅28比特可用于7:8比特编码200。未用于dbi信号线上的7:8比特编码200的四比特可经由离散信号线(例如,错误检测码(edc)信号线)被编码为符号。因此,图10的32比特的数据突发的编码方法可导致出现需要额外信号线的开销。

[0089]

图11是用于解释根据实施例的用于数据突发的编码方法的曲线图。

[0090]

参照图1和图11,pam-4编码器112可对要被发送至数据线的m比特的数据突发执行(m-p):m(m是自然数且p小于m)比特编码。pam-4编码器112可将m比特的p比特值发送至dbi

信号线,并且对于作为dbi信号线上的p比特的总和的q比特,可执行q:(q+k)(其中,k≥1)比特编码并生成dbi信号线的码字。pam-4编码器112可对每个数据突发的其余(m-p)比特执行(m-p):m比特编码,并且生成用于数据线的码字。

[0091]

pam-4编码器112可基于与数据突发的m比特对应的码字总数、在符号之间没有mt事件的码字中的具有在最高符号电平处的最后一个符号的码字的数量、具有在中间电平处的最后符号的码字的数量、具有在最低符号电平处的最后符号的码字的数量、以及具有既不在最高符号电平处也不在最低符号电平处的第一个符号的码字的数量,来确定p比特。因此,(m-p):m比特编码以及q:(q+k)比特编码可被实现为mta编码,使得不发生符号之间的mt事件。

[0092]

pam-4编码器112可被设计为在pam-4符号编码期间针对32比特的数据突发具有3比特的最小开销。当基于lut直接设计29:32比特编码器和/或解码器时,可能需要若干千兆字节(gb)容量的表。为了减少表的大小,参照图3至图5c、图7和图8描述的实施例可应用于29:32比特编码器和/或解码器。因此,可减少要被包括在29:32比特编码器和/或解码器中的表的大小。例如,当通过使用下面的公式1至公式7执行pam-4符号编码时,pam-4编码器112可根据码字长度(或pam-4符号的数量)n来计算开销比特的数量。在32比特的数据突发的情况下,码字长度(或pam-4符号的数量)n可以是16。

[0093]

pam-4编码器112可定义变量hn、mn和ln,以计算对于码字长度n没有mt事件的模式。hn可以是在没有mt事件的情况下具有电平3的最后1个符号的符号n的码字的数量,mn可以是在没有mt事件的情况下具有电平1或电平2的最后1个符号的符号n的码字的数量,并且ln可以是在没有mt事件的情况下具有电平0的最后1个符号的符号n的码字的数量。可通过使用公式1来获得表示变量hn、mn和ln之间的关系的递归关系。

[0094]

[公式1]

[0095]hn+1

=hn+mn[0096]mn+1

=2mn+2hn+2lm[0097]

l

n+1

=ln+mn[0098]

在这种情况下,h1=1,m1=2,和l1=1,其中,n表示当前符号,并且(n+1)表示后续符号。

[0099]

tn是用于码字长度n的码字总数,其可通过使用公式1来计算,并在公式2和3中示出。

[0100]

[公式2]

[0101][0102]

在这种情况下,n表示当前符号,并且(n-1)表示先前符号。

[0103]

[公式3]

[0104]

tn=hn+mn+ln[0105]

作为根据公式2和公式3的码字总数的tn可对应于在块边界(图2中的bb)上不考虑mta的情况,即,对要分配给第一符号的符号电平没有约束。在块边界bb上,也可有必要支持

mta以防止在先前码字的最后1个符号(n-1)和当前码字的第一个符号n之间的mt事件。

[0106]

[公式4]

[0107][0108]

[公式5]

[0109][0110]

可通过基于公式3的tn和公式5的t

′n使用公式6和公式7来计算开销比特的数量x。

[0111]

[公式6]

[0112]

x=2

n-[log tn]

[0113]

[公式7]

[0114]

x=2n-[log t

′n]

[0115]

通过使用公式6和公式7获得的、参照码字长度n具有整数值的开销比特的数量x可在图11中表示为曲线1100。如曲线1100所示,码字长度(或pam-4符号的数量)n为16可对应于开销比特的数量3(1103)。

[0116]

在图11中的曲线1100上,根据图2的7∶8比特编码200的码字长度(或pam-4符号的数量)n为4可对应于开销比特的数量1(1101),并且开销比特的数量1可对应于被发送至dbi信号线的每个半个数据突发的1比特。此外,当将7∶8比特编码200应用于参照图10所述的32比特的数据突发时,可理解,开销比特的数量是4(1102)。相反,当通过使用公式1到公式7对32比特的数据突发执行pam-4符号编码时,开销比特的数量可被减少到3(1103)。因此,当32比特的数据突发的3比特从8条串行数据线dq[i]中的每一条被发送至dbi信号线时,总共24比特可被发送至dbi信号线。

[0117]

图12至图14是根据图11的编码方法的32比特的数据突发结构的示图。

[0118]

参照图1和图12,当pam-4编码器112执行参照图11描述的编码方法并将32比特的数据突发的3比特从8条串行数据线dq[i]中的每一条发送至dbi信号线时,总共24比特可被发送至dbi信号线。pam-4编码器112可将串行数据线dq[i]中的每一条的3比特中的第一比特值1201发送至dbi信号线。之后,串行数据线dq[i]中的每一条的3比特中的第二比特值1202可被发送至dbi信号线,并且随后,第三比特值1203可被发送至dbi信号线。pam-4编码器112可将dbi信号线上的24比特划分成8个3比特的组,并且对每个3比特的组执行3:4比特编码。将参照图14描述3:4比特编码。

[0119]

参照图13,当pam-4编码器112通过执行参照图11描述的编码方法将32比特的数据突发的3比特从8条串行数据线dq[i]中的每一条发送到dbi信号线时,总共24比特可被发送到dbi信号线。pam-4编码器112可将串行数据线dq[i]中的每一条的3比特值1300至1307发送到dbi信号线。pam-4编码器112可对dbi信号线上的3比特值1300到1307执行3:4比特编码。

[0120]

参照图14,3:4比特编码1400可将dbi信号线上的3比特值000转换为具有符号比特0000和符号电平00的码字。3:4比特编码1400可执行码字编码,使得dbi信号线上的3比特值001被转换为符号比特0001和符号电平01,dbi信号线上的3比特值010被转换为符号比特

0100和符号电平10,dbi信号线上的3比特值011被转换为符号比特0101和符号电平11,dbi信号线上的3比特值100被转换为符号比特0011和符号电平02,dbi信号线上的3比特值101被转换为符号比特1100和符号电平20,dbi信号线上的3比特值110被转换为符号比特1101和符号电平21,dbi信号线上的3比特值111被转换为符号比特0111和符号电平12。在3:4比特编码1400中,具有最高电压电平的电平3的pam-4符号的可被不包括在码字中。因此,3:4比特编码1400可支持dbi信号线上的mta。

[0121]

参照图12和图13描述的32比特的数据突发结构可不需要诸如edc信号线的附加信号线,该附加信号线是在图10的7:8比特编码200中支持dbi信号线上的mta所需要的。此外,edc信号线可被配置为用于串行数据线dq[i]上的数据dq的错误检测。pam-4编码器112可通过生成用于数据dq的校验和或循环冗余校验(crc)并将特定crc比特发送到edc信号线来提供性能改进。因此,pam-4编码器112可通过执行图11的编码方法将串行数据线dq[i]中的每一条的32比特的数据突发中的3比特发送到dbi信号线,并且通过对dbi信号线执行3:4比特编码1400来支持dbi信号线上的mta,来满足其性能改进。

[0122]

图15是根据实施例的包括编码装置和解码装置的存储器系统1500的第一示例的框图。

[0123]

参照图15,存储器系统1500可包括存储器控制器1510和存储器装置1520。存储器系统1500可以是集成电路、电子装置或系统、智能电话、平板个人计算机(pc)、计算机、服务器、工作站、便携式通信终端、个人数字助理(pda)、便携式多媒体播放器(pmp)、诸如其它已知计算机的计算装置、虚拟机或其虚拟计算装置等。可替换地,存储器系统1500可包括包含在诸如图形卡的计算系统中的一些组件。

[0124]

存储器控制器1510可经由信道或存储器总线1530被连接以与存储器装置1520进行通信。为简单起见,在附图中,时钟clk、命令/地址ca和数据dq被示出为经由存储器控制器1510与存储器装置1520之间的1条信号线提供,但实际上可经由多条信号线或总线提供。

[0125]

clk信号可经由存储器总线1530的clk信号线从存储器控制器1510被发送到存储器装置1520。ca信号可经由存储器总线1530的ca总线从存储器控制器1510被发送到存储器装置1520。芯片选择(cs)信号可经由存储器总线1530的cs信号线从存储器控制器1510被发送到存储器装置1520。被激活为逻辑高的cs信号可指示经由ca总线发送的ca信号为命令。数据dq可经由存储器总线1530的dq总线从存储器控制器1510被发送到存储器装置1520或从存储器装置1520被发送到存储器控制器1510,并且dq总线可包括双向信号线。

[0126]

存储器控制器1510可包括向存储器装置1520发送数据dq的数据发送器1512,并且数据发送器1512可包括被配置为将要被发送至存储器装置1520的写入数据突发转换成pam-4符号的pam-4编码器112。pam-4编码器112可包括图1中的逻辑电路114、组合lut 310以及第一子块lut 321至第四子块lut 324,这些子块lut在lut集320内部互连,如参照图3至图5c所描述的。pam-4编码器112可被配置为基于参照图6描述的编码的操作方法600、参照图11至图14描述的数据突发结构、以及dbi mta码字,将写入数据突发编码为pam-4符号。存储器控制器1510可经由dq总线将被编码的pam-4符号作为数据dq发送到存储器装置1520。

[0127]

存储器装置1520可根据存储器控制器1510的控制写入或读取数据dq。存储器装置1520可包括存储器单元阵列1522及数据输入缓冲器1524。

[0128]

存储器单元阵列1522可包括多条字线和多条位线,以及在字线与位线交叉的点处形成的多个存储器单元。存储器单元阵列1522的存储器单元可包括易失性存储器单元(例如,动态随机存取存储器(ram)(dram)单元、静态ram(sram)单元等)、非易失性存储器单元(例如,闪速存储器单元、电阻式ram(rram)单元、相变ram(pram)单元、磁性ram(mram)单元等)或任何已知的不同类型的存储器单元。

[0129]

存储器装置1520可被配置为接收并解码经由dq总线发送到数据输入缓冲器1524的pam-4符号。数据输入缓冲器1524可包括被配置为将pam-4符号恢复为写入数据突发的pam-4解码器122。pam-4解码器122可包括图1中的逻辑电路124、参照图7和图8描述的组合lut 310、lut集320、以及码字解码lut 710。pam-4解码器122可被配置为基于参照图9描述的解码的操作方法900将pam-4符号解码为写入数据突发。数据输入缓冲器1524可提供要被写入到存储器单元阵列1522中的已解码的写入数据突发。

[0130]

图16是根据实施例的存储器装置1520的一部分的框图。

[0131]

参照图16,存储器装置1520可包括存储器单元阵列1522、行解码器1601、字线(wl)驱动器1602、列解码器1603、输入/输出(i/o)门电路1604、mrs 1605、控制逻辑电路1606、地址缓冲器1607、数据输入缓冲器1524、和数据输出缓冲器1526。

[0132]

存储器单元阵列1522可包括以按行和列布置的矩阵形式提供的多个存储器单元。存储器单元阵列1522可包括连接到存储器单元的多条字线wl和多条位线bl。多条字线wl可连接到存储器单元的行,并且多条位线bl可连接到存储器单元的列。

[0133]

行解码器1601可选择连接到存储器单元阵列1522的多条字线wl中的任何1条。行解码器1601可对从地址缓冲器1607接收的行地址row_addr进行解码,并且选择与行地址row_addr对应的任何1条字线wl,并且然后,可连接到激活所选择的字线wl的字线驱动器1602。列解码器1603可选择多条位线bl中的某些位线bl。列解码器1603可对从地址缓冲器1607接收的列地址col_addr进行解码,并且产生列选择信号,并且然后,可将由列选择信号选择的位线bl连接到输入/输出门电路1604。输入/输出门电路1604可包括存储由列选择信号选择的位线bl的读取数据的读取数据锁存器,以及用于将写入数据写入到存储器单元阵列1522中的写入驱动器。存储在输入/输出门电路1604的读取数据锁存器中的读取数据可经由数据输出缓冲器1526被提供到dq总线。写入数据可经由连接到dq总线的数据输入缓冲器1524并且经由输入/输出门电路1604的写入驱动器被施加到存储器单元阵列1522。

[0134]

控制逻辑电路1606可接收clk信号和命令cmd,并产生控制存储器装置1520的操作时序和/或存储器操作的控制信号ctrls。控制逻辑电路1606可通过使用控制信号ctrls从存储器单元阵列1522读取数据并将数据写入到存储器单元阵列1522中。

[0135]

为了设置存储器装置1520的操作条件,mrs 1605可存储由控制逻辑电路1606使用以用于构成存储器装置1520的操作的信息。mrs 1605可包括用于设置存储器装置1520以及存储控制参数的参数代码的寄存器的操作条件的各种操作。存储器装置1520可经由ca总线接收参数代码。控制逻辑电路1606可向存储器装置1520的电路提供控制信号ctrls,使得控制逻辑电路1606按照由mrs 1605存储的操作和控制参数所配置的那样进行操作。

[0136]

图17是根据实施例的包括编码装置和解码装置的存储器系统1700的第二示例的框图。

[0137]

参照图17,存储器系统1700与图15的存储器系统1500的不同之处可在于,存储器

控制器1710还包括数据接收器1714,数据接收器1714包括pam-4解码器122,并且存储器装置1720还包括数据输出缓冲器1526,数据输出缓冲器1526包括pam-4编码器112。

[0138]

当将从存储器单元阵列1522输出的读取数据突发发送到存储器控制器1710时,存储器装置1720可被配置为将读取数据突发编码为pam-4符号并且经由数据输出缓冲器1526发送经编码的pam-4符号。数据输出缓冲器1526可包括被配置为将读取数据转换为pam-4符号的pam-4编码器112。

[0139]

存储器控制器1710可被配置为接收并解码经由dq总线发送至数据接收器1714的pam-4符号。数据接收器1714可包括pam-4解码器122,pam-4解码器122被配置为将pam-4符号恢复为读取数据突发。

[0140]

尽管已经参照本发明构思的实施例具体示出和描述了本发明构思,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可在其中进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1