脉动阵列以及包括脉动阵列的加速器

脉动阵列以及包括脉动阵列的加速器

1.相关申请的交叉引用

2.本技术基于并要求于2021年5月3日在韩国知识产权局提交的韩国专利申请no.10-2021-0057124的优先权,所述韩国专利申请的公开内容通过引用全部包含于此。

技术领域

3.本公开涉及脉动阵列(systolic array)以及包括脉动阵列的加速器。

背景技术:

4.包括脉动阵列的加速器用于执行基于卷积神经网络(cnn)的运算,诸如,卷积运算。脉动阵列可以包括以矩阵设置的多个处理元件。例如,脉动阵列可以包括多个硬件结构,多个硬件结构包括以矩阵布置的数据处理单元(dpu)。通常,脉动阵列的矩阵的大小可以固定以执行卷积运算。

技术实现要素:

5.本公开示例性实施例提供了一种能够通过可变地重新配置脉动阵列的矩阵的大小来执行卷积运算的脉动阵列以及包括脉动阵列的加速器。

6.本公开不限于上述目的,本领域技术人员将基于以下对本公开的描述清楚地理解其他未提及的目的。

7.根据本公开的一方面,提供一种脉动阵列,包括多个处理元件,所述多个处理元件以n

×

n矩阵被设置,所述多个处理元件被配置为执行以下操作:对第一输入n

×

n矩阵的行向量的第一输入数据和第一权重n

×

n矩阵的列向量的第一权重数据进行第一卷积运算,以生成n个第一输出数据,或者将所述多个处理元件划分为k个部分脉动阵列,所述k个部分脉动阵列中的每一者包括以m

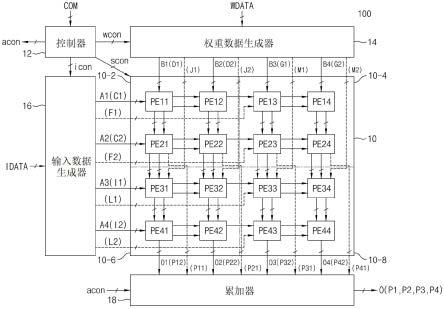

×

m矩阵设置的多个子处理元件,和对k个第二输入m

×

m矩阵的行向量的第二输入数据和k个第二权重m

×

m矩阵的列向量的第二权重数据执行第二卷积运算,以生成m个第二输出数据,每个所述第二输入m

×

m矩阵对应所述k个部分脉动阵列之一,每个所述第二权重m

×

m矩阵对应所述k个部分脉动阵列之一,其中,n是大于或等于4的整数,其中,k是大于或等于4的整数,并且其中,m为小于n的整数,并且m大于或等于2。

8.根据本公开的另一方面,提供一种加速器,包括脉动阵列、累加器、输入数据生成器、以及权重数据生成器;所述脉动阵列包括以n

×

n矩阵设置的多个处理元件,所述多个处理元件被配置为执行以下操作:响应于控制信号,对第一输入n

×

n矩阵的n个行向量的第一输入数据和第一权重n

×

n矩阵的n个列向量的第一权重数据进行第一卷积运算,以生成n个第一输出数据,或者将所述多个处理元件划分为k个部分脉动阵列,所述k个部分脉动阵列中的每一者包括以m

×

m矩阵设置的多个子处理元件,和对k个第二输入m

×

m矩阵的行向量的第二输入数据和k个第二权重m

×

m矩阵的列向量的第二权重数据执行第二卷积运算,以生成m个第二输出数据,每个所述第二输入m

×

m矩阵对应所述k个部分脉动阵列之一,每个所述第二权重m

×

m矩阵对应所述k个部分脉动阵列之一,其中,n为大于或等于4的整数,其

中,k为大于或等于4的整数,其中,m为小于n的整数,并且m大于或等于2;所述累加器被配置为:响应于所述控制信号,累加所述n个第一输出数据以生成第一卷积结果数据,或者累加从所述k个部分脉动阵列中的每一者生成的所述m个第二输出数据,以生成k个第二卷积结果数据;所述输入数据生成器被配置为:响应于所述控制信号,生成所述第一输入n

×

n矩阵的所述n个行向量的所述第一输入数据,或生成所述k个第二输入m

×

m矩阵中的每一者的m个行向量的所述第二输入数据;所述权重数据生成器被配置为:响应于所述控制信号,生成所述第一权重n

×

n矩阵的所述n个列向量的所述第一权重数据,或者生成所述k个第二权重m

×

m矩阵中的每一者的m个列向量的所述第二权重数据。

附图说明

9.图1是根据本公开示例实施例的加速器的框图。

10.图2是示出根据本公开示例实施例的处理元件的结构的框图。

11.图3是示出根据本公开示例实施例的第一输入矩阵、第一权重矩阵、处理元件的第一部分累加结果和脉动阵列的第一输出数据的图。

12.图4是示出根据本公开示例实施例的第一输入数据和第一权重数据的输入序列以及脉动阵列的第一输出数据的输出序列的图。

13.图5a至图5d是示出根据本公开示例实施例的脉动阵列的第一卷积运算的图。

14.图6a至图6d是示出根据本公开示例实施例的第二输入矩阵、第二权重矩阵、处理元件的第四部分累加结果以及部分脉动阵列的第二输出数据的图。

15.图7是示出根据本公开示例实施例的第二输入数据和第二权重数据的输入序列以及部分脉动阵列的第二输出数据的输出序列的图。

16.图8a至图8d是示出根据本公开示例实施例的部分脉动阵列的第二卷积运算的图。

具体实施方式

17.在下文中,将参照附图描述根据本公开实施例的脉动阵列和包括该脉动阵列的加速器。

18.图1是根据本公开示例实施例的加速器的框图。加速器100可以包括脉动阵列10、控制器12、权重数据生成器14、输入数据生成器16和累加器18。脉动阵列10可以包括以矩阵(例如,4

×

4矩阵)布置的16个处理元件pe11至pe44。脉动阵列10可以分为四个部分脉动阵列10-2、10-4、10-6和10-8,并且四个部分脉动阵列10-2、10-4、10-6和10-8各自可以包括均以2

×

2矩阵布置的四个处理元件pe11、pe12、pe21和pe22,pe13、pe14、pe23和pe24,pe31、pe32、pe41和pe42,以及pe33、pe34、pe43和pe44。根据各种示例实施例,脉动阵列可以包括多个硬件结构,这些硬件结构包括以矩阵布置的数据处理单元(dpu)。例如,处理元件可以是硬件电子部件和/或电子电路。

19.将描述图1中所示的每个块的功能。

20.响应于脉动阵列控制信号scon,脉动阵列10可以对第一输入4

×

4矩阵a的行向量的第一输入数据a1至a4以及第一权重4

×

4矩阵b的列向量的第一权重数据b1至b4执行第一卷积运算,以生成四个第一输出数据o1至o4,或者四个部分脉动阵列10-2、10-4、10-6和10-8可以对四个第二输入2

×

2矩阵c、f、i和l的行向量的第二输入数据c1和c2、f1和f2、i1和

i2、l1和l2以及第二权重2

×

2矩阵d、g、j和m的行向量的第二权重数据d1和d2、g1和g2、j1和j2、m1和m2执行第二卷积运算,以分别生成输出数据p11和p21、p31和p41、p12和p22、以及p32和p42。

21.脉动阵列10可以接收第一输入数据a1至a4和第一权重数据b1至b4,16个处理元件pe11至pe44可以执行第一卷积运算以生成四个第一输出数据o1至o4。

22.在第一卷积运算期间,在4

×

4处理元件pe11至pe44当中,设置在第一列中的处理元件pe11、pe21、pe31和pe41可以分别接收第一输入矩阵a的四个行向量的第一输入数据a1、a2、a3和a4,设置在第一行中的处理元件pe11、pe12、pe13和pe14可以分别接收第一权重矩阵b的列向量的第一权重数据b1、b2、b3和b4,除了设置在第一列中的处理元件pe11、pe21、pe31和pe41之外的处理元件可以分别接收通过设置在左侧的前端处理元件施加的第一输入数据a1、a2、a3和a4,除了设置在第一行中的处理元件pe11、pe12、pe13和pe14之外的处理元件可以分别接收通过设置在上侧(例如,上游侧)的前端处理元件施加的第一权重数据b1、b2、b3、b4。此外,4

×

4的处理元件pe11至pe44可以分别将第一输入数据a1、a2、a3、a4与第一权重数据b1、b2、b3、b4相乘以获得第一相乘结果,可以累加第一相乘结果以获得第一部分累加结果,可以将第一部分累加结果与从设置在上侧的前端处理元件发送的第二部分累加结果相加以获得第三部分累加结果,并且可以向设置在下侧(即,下游侧)的后端处理元件发送第三部分累加结果。

23.部分脉动阵列10-2可以接收第二输入数据c1和c2以及第二权重数据d1和d2,并且四个处理元件pe11、pe12、pe21和pe22可以执行第二卷积运算以生成两个第二输出数据p11和p21。部分脉动阵列10-4可以接收第二输入数据f1和f2以及第二权重数据g1和g2,并且四个处理元件pe13、pe14、pe23和pe24可以执行第二卷积运算以生成两个第二输出数据p31和p41。部分脉动阵列10-6可以接收第二输入数据i1和i2以及第二权重数据j1和j2,并且四个处理元件pe31、pe32、pe41和pe42可以执行第二卷积运算以生成两个第二输出数据p12和p22。部分脉动阵列10-8可以接收第二输入数据l1和l2以及第二权重数据m1和m2,并且四个处理元件pe33、pe34、pe43和pe44可以执行第二卷积运算以生成两个第二输出数据p32和p42。

24.作为示例,在第二卷积运算期间,在部分脉动阵列10-2、10-4、10-6和10-8当中,在部分脉动阵列10-4和10-8的2

×

2处理元件pe13、pe14、pe23和pe24以及pe33、pe34、pe43和pe44的第一列中设置的处理元件pe13和pe23以及pe33和pe43(不包括设置在4

×

4处理元件pe11至pe44的第一列中的四个处理元件pe11、pe21、pe31和pe41)可以不分别接收通过设置在左侧的前端处理元件发送的第二输入数据c1和c2以及i1和i2,而是可以分别接收第二输入2

×

2矩阵f和l的行向量的第二输入数据f1和f2以及l1和l2。在部分脉动阵列10-2、10-4、10-6和10-8当中,在部分脉动阵列10-6和10-8的2

×

2处理元件pe31、pe32、pe41和pe42以及pe33、pe34、pe43和pe44的第一行中设置的处理元件pe31和pe32以及pe33和pe43(不包括设置在4

×

4处理元件pe11至pe44的第一行中的四个处理元件pe11、pe12、pe13和pe14)可以不分别接收通过设置在上侧的前端处理元件发送的第二权重数据d1和d2以及g1和g2,而是可以分别接收第二权重2

×

2矩阵j和m的列向量的第二权重数据j1和j2以及m1和m2。在部分脉动阵列10-2、10-4、10-6和10-8的2

×

2处理元件pe11至pe22、pe13至pe24、pe31至pe42以及pe33至pe44当中,除了设置在第一列中的处理元件pe11和pe21、pe13和pe23、pe31和pe41、

以及pe33和pe43之外的处理元件可以分别接收通过设置在左侧的前端处理元件施加的第二输入数据c1和c2、f1和f2、i1和i2、以及l1和l2。在部分脉动阵列10-2、10-4、10-6和10-8的2

×

2处理元件pe11至pe22、pe13至pe24、pe31至pe42、以及pe33至pe44当中,除了设置在第一行中的处理元件pe11和pe12、pe13和pe14、pe31和pe32、以及pe33和pe34之外的处理元件可以分别接收通过设置在上侧的前端处理元件施加的第二权重数据d1和d2、g1和g2、j1和j2、以及m1和m2。部分脉动阵列10-2、10-4、10-6和10-8的2

×

2处理元件可以分别将第二输入数据c1和c2、f1和f2、i1和i2、l1和l2与第二权重数据d1和d2、g1和g2、j1和j2、m1和m2相乘以获得第二相乘结果,可以累加第二相乘结果以获得第四部分累加结果,可以将第四部分累加结果和从设置在上侧的前端处理元件发送的第五部分累加结果进行累加以获得第六部分累加结果,并且可以向设置在下侧的后端处理元件发送第六部分累加结果,或者可以不发送第六部分累加结果。

25.作为另一示例,在第二卷积运算期间,第二权重矩阵d、g、j和m的第二权重数据d1和d2、g1和g2、j1和j2、以及m1和m2可以分别预先存储在部分脉动阵列10-2、10-4、10-6和10-8的2

×

2处理元件pe11至pe22、pe13至pe24、pe31至pe42以及pe33至pe44中。在这种情况下,与图1所示的不同,在部分脉动阵列10-2、10-4、10-6和10-8当中,在部分脉动阵列10-6和10-8的2

×

2处理元件pe31至pe42以及pe33至pe44的第一行中设置的处理元件pe31和pe32以及pe33和pe34(不包括设置在4

×

4处理元件pe11至pe44的第一行中的四个处理元件pe11、pe12、pe13和pe14)可以分别接收通过设置在上侧的前端处理元件发送的第二权重数据j1和j2以及m1和m2。也就是说,可以应用第二权重矩阵d和g的第二权重数据d1和d2以及g1和g2,然后可以应用第二权重矩阵j和m的第二权重数据j1和j2以及m1和m2。

26.响应于命令信号com,控制器12可以生成脉动阵列控制信号scon、输入数据控制信号icon、权重数据控制信号wcon和累加器控制信号acon。例如,脉动阵列控制信号scon、输入数据控制信号icon和权重数据控制信号wcon可以是与权重矩阵的大小相关的控制信号。

27.权重数据生成器14可以存储从外部施加的权重数据wdata,并且可以响应于权重数据控制信号wcon生成第一权重数据b1至b4、或者第二权重数据d1和d2、g1和g2、j1和j2以及m1和m2。权重数据生成器14可以在权重矩阵的大小为4

×

4的情况下生成第一权重数据b1至b4,并且可以在权重矩阵的大小为2

×

2的情况下生成第二权重数据d1和d2、g1和g2、j1和j2、以及m1和m2。作为实施例,权重数据生成器14可以是存储器。存储器可以是动态随机存取存储器(dram)。

28.输入数据生成器16可以存储从外部施加的输入数据idata,并且可以响应于输入数据控制信号icon生成第一输入数据a1至a4、或者第二输入数据c1和c2、i1和i2、f1和f2以及l1和l2。输入数据生成器16可以在输入矩阵的大小为4

×

4的情况下生成第一输入数据a1至a4,并且可以在输入矩阵的大小为2

×

2的情况下生成第二输入数据c1和c2、i1和i2、f1和f2、以及l1和l2。作为实施例,输入数据生成器16可以是存储器。权重数据生成器14和输入数据生成器16可以被配置为单个存储器。存储器可以是dram。

29.响应于累加器控制信号acon,累加器18可以累加第一输出数据o1至o4以生成第一卷积结果数据o,或者可以累加第二输出数据p11和p21、p12和p22、p31和p41、以及p32和p42以生成四个第二卷积结果数据p1、p2、p3和p4。尽管在图1所示的实施例中,脉动阵列10被示出为以4

×

4矩阵配置,但是脉动阵列10可以以n

×

m矩阵配置(n和m中的每一者是等于或大

于5的整数,并且n和m彼此相同或不同)。此外,虽然示出了将脉动阵列10划分为被配置为执行第二卷积运算的四个部分脉动阵列10-2、10-4、10-6和10-8的结构,但是脉动阵列10可以划分为被配置为执行第二卷积运算的多于四个的部分脉动阵列。

30.图2是示出根据本公开示例实施例的处理元件的结构的框图。处理元件200可以包括:复用器(mux)52和54,寄存器(r)56、58和64,乘法器(mul)60,部分累加器(pacc)62,以及解复用器(demux)66。复用器52和54以及解复用器66均可以是选择器。

31.将参照图1和图2描述图2中所示的每个块的功能。

32.响应于脉动阵列控制信号scon,复用器52可以在第一卷积运算期间选择和输出施加到第一端子s1的第一输入数据v,并且可以在第二卷积运算期间选择和输出施加到第二端子s2的第二输入数据w。根据示例实施例,在第一卷积运算中,输入数据v可以是从输入数据生成器16输出的第一输入数据a1、a2、a3和a4,或者通过设置在左侧的前端处理元件发送的输入数据。根据示例实施例,在第二卷积运算中,输入数据w可以是从输入数据生成器16输出的第二输入数据c1和c2、i1和i2、f1和f2以及l1和l2,或者通过设置在左侧的前端处理元件发送的输入数据。

33.作为示例,除了图1中所示的设置在第三列中的处理元件pe13、pe23、pe33和pe43的复用器52之外,其他处理元件的复用器52的第一端子s1和第二端子s2可以相互连接。作为另一示例,除了图1中所示的设置在第三列中的处理元件pe13、pe23、pe33和pe43之外的每个处理元件可以不包括复用器52。

34.响应于脉动阵列控制信号scon,复用器54可以在第一卷积运算期间选择和输出施加到第一端子的第一权重数据x,并且可以在第二卷积运算期间选择和输出施加到第二端子s2的第二权重数据y。根据示例实施例,在第一卷积运算中,第一权重数据x可以是从权重数据生成器14输出的第一权重数据b1、b2、b3和b4,或者通过设置在上游方向中的前端处理元件发送的权重数据。根据示例实施例,权重数据y可以是从权重数据生成器14输出的第二权重数据d1和d2、j1和j2、g1和g2以及m1和m2,或者通过设置在上游方向中的前端处理元件发送的第二权重数据。

35.作为示例,除了图1中所示的设置在第三行中的处理元件pe31、pe32、pe33和pe34的复用器54之外,其他处理元件的复用器54的第一端子s1和第二端子s2可以相互连接。作为另一示例,除了图1中所示的设置在第三行中的处理元件pe31、pe32、pe33和pe34之外的每个处理元件可以不包括复用器54。作为又一示例,在应用第二权重数据d1和d2以及g1和g2然后应用第二权重数据j1和j2以及m1和m2的情况下,如上所述,各处理元件pe11至pe44可以不包括复用器54。另外,在第二权重数据存储在所有处理元件pe11至pe44中的情况下,权重数据可以不施加到寄存器58。

36.寄存器56可以存储从复用器52输出的输入数据。存储的输入数据可以被发送到设置在下侧的后端处理元件。

37.寄存器58可以存储从复用器54输出的权重数据。存储的权重数据可以被发送到设置在下侧的后端处理元件。

38.乘法器60可以在第一卷积运算期间将从寄存器56输出的第一输入数据与从寄存器58输出的第一权重数据相乘以生成第一相乘结果,并且可以在第二卷积运算期间将从寄存器56输出的第二输入数据与从寄存器58输出的第二权重数据相乘以生成第二相乘结果。

39.部分累加器62可以在第一卷积运算期间累加从乘法器60输出的第一相乘结果以生成第一部分累加结果,并且可以将第一部分累加结果和从设置在上侧的前端处理元件发送的第二部分累加结果z进行累加以获得第三部分累加结果,并且可以在第二卷积运算期间累加从乘法器60输出的第二相乘结果以生成第四部分累加结果,并且可以将第四部分累加结果和第五部分累加结果z进行累加以获得第六部分累加结果。

40.寄存器64可以存储从部分累加器62输出的第三部分累加结果或第六部分累加结果。

41.响应于脉动阵列控制信号scon,解复用器66可以向设置在下侧的后端处理元件或累加器18发送从寄存器64输出的第三部分累加结果或第六部分累加结果。

42.图3是示出根据本公开示例实施例的第一输入矩阵、第一权重矩阵、处理元件的第一部分累加结果和脉动阵列的第一输出数据的图。

43.参照图3,作为4

×

4矩阵的第一输入矩阵a可以包括第一行向量的第一输入数据a1(a11、a12、a13和a14)、第二行向量的第一输入数据a2(a21、a22、a23和a24)、第三行向量的第一输入数据a3(a31、a32、a33和a34)以及第四行向量的第一输入数据a4(a41、a42、a43和a44)。

44.作为4

×

4矩阵的第一权重矩阵b可以包括第一列向量的第一权重数据b1(b11、b21、b31和b41)、第二列向量的第一权重数据b2(b12、b22、b32和b42)、第三列向量的第一权重数据b3(b13、b23、b33和b43)、以及第四列向量的第一权重数据b4(b14、b24、b34和b44)。

45.部分累加矩阵r指示处理元件pe11至pe44的第一部分累加结果r11至r44。也就是说,可以通过处理元件pe11获得第一部分累加结果r11(r11=a11

×

b11+a12

×

b21+a13

×

b31+a14

×

b41),并且第一部分累加结果r11可以生成为第三部分累加结果r11。可以通过处理元件pe21获得第一部分累加结果r21(r21=a21

×

b11+a22

×

b21+a23

×

b31+a24

×

b41),并且第一部分累加结果r11和从处理元件pe11生成的第三部分累加结果r11可以相加以生成第三部分累加结果r11+r21。可以通过处理元件pe31获得第一部分累加结果r31(r31=a31

×

b11+a32

×

b21+a33

×

b31+a34

×

b41),并且第一部分累加结果r31和从处理元件pe21生成的第三部分累加结果r11+r21可以相加以生成第三部分累加结果r11+r21+r31。可以通过处理元件pe41获得第一部分累加结果r41(r41=a41

×

b11+a42

×

b21+a43

×

b31+a44

×

b41),并且第一部分累加结果r41和从处理元件pe31生成的第三部分累加结果r11+r21+r31可以相加以生成第三部分累加结果r11+r21+r31+r41作为输出数据o1。可以使用相同的方法获得其他部分累加结果并且可以生成输出数据o2、o3和o4。

46.累加器18可以将输出数据o1、o2、o3和o4相加以生成第一卷积结果数据o。

47.图4是示出根据本公开示例实施例的第一输入数据和第一权重数据的输入序列以及脉动阵列的第一输出数据的输出序列的图。

48.参照图3和图4,第一行向量的第一输入数据a1(a11至a14)和第一列向量的第一权重数据b1(b11至b41)在第一周期t1开始被应用,第二行向量的第一输入数据a2(a21至a24)和第二列向量的第一权重数据b2(b12至b42)在第二周期t2开始被应用,第三行向量的第一输入数据a3(a31至a34)和第三列向量的第一权重数据b3(b13至b43)在第三周期t3开始被应用,并且第四行向量的第一输入数据a4(a41至a44)和第四列向量的第一权重数据b4(b14至b44)在第四周期t4开始被应用。从第一周期t1至第七周期t7,第一输入数据a1(a11至

a14)、a2(a21至a24)、a3(a31至a34)和a4(a41至a44)可以在逐个延迟一个周期的状态下被顺序地应用,第一权重数据b1(b11至b41)、b2(b12至b42)、b3(b13至b43)和b4(b14至b44)在逐个延迟一个周期的状态下被顺序地应用。从第七周期t7至第十周期t10,第一输出数据o1、o2、o3和o4可以在逐个延迟一个周期的状态下被顺序地生成。

49.图5a至图5d是示出根据本公开示例实施例的脉动阵列的第一卷积运算的图。在第三周期t3、第四周期t4、第五周期t5、第六周期t6、第八周期t8和第九周期t9的操作被省略。

50.参照图5a,在第一周期t1,处理元件pe11可以将第一输入数据a11与第一权重数据b11相乘(a11

×

b11)以获得第一相乘结果r111。

51.参照图5b,在第二周期t2,处理元件pe11可以将第一输入数据a12与第一权重数据b21相乘(a12

×

b21)以获得第一相乘结果r112,并且可以将第一相乘结果r111与第一相乘结果r112相加。处理元件pe12可以将第一输入数据a11与第一权重数据b12相乘(a11

×

b12)以获得第一相乘结果r121。处理元件pe21可以将第一输入数据a21与第一权重数据b11相乘(a21

×

b11)以获得第一相乘结果r211。

52.参照图5c,在第七周期t7,处理元件pe41可以将第一输入数据a44与第一权重数据b41相乘(a44

×

b41)以获得第一相乘结果r414,可以将第一相乘结果r414与在第六周期t6获得的第一相乘结果相加以获得第一部分累加结果r41,并且可以将第一部分累加结果r41与从处理元件pe31发送的第二部分累加结果r11+r21+r31相加,以生成第三部分累加结果r11+r21+r31+r41作为输出数据o1。其他处理元件也可以通过其操作来获得图5c中所示的结果。

53.参照图5d,在第十周期t10,处理元件pe44可以将第一输入数据a44与第一权重数据b44相乘(a44

×

b44)以获得第一相乘结果r444,可以将第一相乘结果r444与在第九周期t9获得的第一相乘结果相加以获得第一部分累加结果r44,并且可以将第一部分累加结果r44与从处理元件pe34发送的第二部分累加结果r14+r24+r34相加,以生成第三部分累加结果r14+r24+r34+r44作为输出数据o4。

54.图6a至图6d是示出根据本公开示例实施例的第二输入矩阵、第二权重矩阵、处理元件的第四部分累加结果以及部分脉动阵列的第二输出数据的图。

55.参照图1和图6a,作为2

×

2矩阵的部分脉动阵列10-2的第二输入矩阵c可以包括第一行向量的第二输入数据c1(c11和c12)和第二行向量的第二输入数据c2(c21和c22)。作为2

×

2矩阵的部分脉动阵列10-2的第二权重矩阵d可以包括第一列向量的第二权重数据d1(d11和d21)和第二列向量的第二权重数据d2(d12和d22)。矩阵e指示由处理元件pe11、pe12、pe21和pe22获得的第四部分累加结果e11至e22。可以通过处理元件pe11获得第四部分累加结果e11(e11=c11

×

d11+c12

×

d21),并且第四部分累加结果e11可以生成为第六部分累加结果。可以通过处理元件pe21获得第四部分累加结果e21(e21=c21

×

d11+c22

×

d21),并且第四部分累加结果e21与第五部分累加结果e11可以相加以生成第六部分累加结果e11+e21作为第二输出数据p11。可以通过处理元件pe12获得第四部分累加结果e12(e12=c11

×

d12+c12

×

d22),并且第四部分累加结果e12可以生成为第六部分累加结果。可以通过处理元件pe22获得第四部分累加结果e22(e22=c21

×

d12+c22

×

d22),并且第四部分累加结果e22与从处理元件pe12输出的第五部分累加结果e12相加以生成第六部分累加结果e12+e22作为第二输出数据p21。

56.参照图1和图6b,作为2

×

2矩阵的部分脉动阵列10-4的第二输入矩阵f可以包括第一行向量的第二输入数据f1(f11和f12)和第二行向量的第二输入数据f2(f21和f22)。作为2

×

2矩阵的部分脉动阵列10-4的第二权重矩阵g可以包括第一列向量的第二权重数据g1(g11和g21)和第二列向量的第二权重数据g2(g12和g22)。矩阵h指示由处理元件pe13、pe14、pe23和pe24获得的第四部分累加结果h11至h22。可以通过处理元件pe13获得第四部分累加结果h11(h11=f11

×

g11+f12

×

g21),并且第四部分累加结果h11可以生成为第六部分累加结果。可以通过处理元件pe23获得第四部分累加结果h21(h21=f21

×

g11+f22

×

g21),并且第四部分累加结果h21与从处理元件pe13输出的第五部分累加结果h11可以相加以生成第六部分累加结果h11+h21作为第二输出数据p31。可以通过处理元件pe14获得第四部分累加结果h12(h12=f11

×

g12+f12

×

g22),并且第四部分累加结果h12可以生成为第六部分累加结果。可以通过处理元件pe24获得第四部分累加结果h22(h22=f21

×

g12+f22

×

g22),并且第四部分累加结果h22与从处理元件pe14输出的第五部分累加结果h12可以相加以生成第六部分累加结果h12+h22作为第二输出数据p41。

57.参照图1和图6c,作为2

×

2矩阵的部分脉动阵列10-6的第二输入矩阵i可以包括第一行向量的第二输入数据i1(i11和i12)和第二行向量的第二输入数据i2(i21和i22)。作为2

×

2矩阵的部分脉动阵列10-6的第二权重矩阵j可以包括第一列向量的第二权重数据j1(j11和j21)和第二列向量的第二权重数据j2(j12和j22)。矩阵k指示处理元件pe31、pe32、pe41和pe42获得的第四部分累加结果k11至k22。可以通过处理元件pe31获得第四部分累加结果k11(k11=i11

×

j11+i12

×

j21),并且第四部分累加结果k11可以生成为第六部分累加结果。可以通过处理元件pe41获得第四部分累加结果k21(k21=i21

×

j11+i22

×

j21),并且第四部分累加结果k21与从处理元件pe31输出的第五部分累加结果k11可以相加以生成第六部分累加结果k11+k21作为第二输出数据p12。可以通过处理元件pe32获得第四部分累加结果k12(k12=i11

×

j12+i12

×

j22),并且第四部分累加结果k12可以生成为第六部分累加结果。可以通过处理元件pe42获得第四部分累加结果k22(k22=i21

×

j12+i22

×

j22),并且第四部分累加结果k22与从处理元件pe32输出的第五部分累加结果k12可以相加以生成第六部分累加结果k12+k22作为输出数据p22。

58.参照图1和图6d,作为2

×

2矩阵的部分脉动阵列10-8的输入矩阵l可以包括第一行向量的第二输入数据l1(ll1和ll2)和第二行向量的第二输入数据l2(l21和l22)。作为2

×

2矩阵的部分脉动阵列10-8的第二权重矩阵m可以包括第一列向量的第二权重数据m1(m11和m21)和第二列向量的第二权重数据m2(m12和m22)。矩阵n指示处理元件pe33、pe34、pe43和pe44获得的第四部分累加结果n11至n22。可以通过处理元件pe33获得第四部分累加结果n11(n11=l11

×

m11+l12

×

m21),并且第四部分累加结果n11可以生成为第六部分累加结果。可以通过处理元件pe43获得第四部分累加结果n21(n21=l21

×

m11+l22

×

m21),并且第四部分累加结果n21与从处理元件pe33输出的第五部分累加结果n11可以相加以生成第六部分累加结果n11+n21作为第二输出数据p32。可以通过处理元件pe34获得第四部分累加结果n12(n12=l11

×

m12+l12

×

m22),并且第四部分累加结果n12可以生成为第六部分累加结果。可以通过处理元件pe44获得第四部分累加结果n22(n22=l21

×

m12+l22

×

m22),并且第四部分累加结果n22与从处理元件pe34输出的第五部分累加结果n12可以相加以生成第六部分累加结果n12+n22作为输出数据p42。

59.图7是示出根据本公开示例实施例的第二输入数据和第二权重数据的输入序列以及部分脉动阵列的第二输出数据的输出序列的图。

60.参照图6a至图7,第二输入矩阵c、f、i和l的第一行向量的第二输入数据c1、f1、i1和l1以及第二权重矩阵d、g、j和m的第一列向量的第二权重数据d1、j1、g1和m1在第一个周期t1开始被应用,第二输入矩阵c、f、i和l的第二行向量的第二输入数据c2、f2、i2和l2以及第二权重矩阵d、g、j和m的第二列向量的第二权重数据d2、g2、j2和m2在第二周期t2开始被应用。从第一周期t1至第三周期t3,第二输入数据c1(c11和c12)、f1(f11和f12)、i1(i11和i12)、l1(l11和l12)、c2(c21和c22)、f2(f21和f22)、i2(i21和i22)和l2(l21和l22)可以在逐个延迟一个周期的状态下被顺序地应用,并且第二权重数据d1(d11和d21)、j1(j11)和j21)、g1(g11和g21)、m1(m11和m21)、d2(d12和d22)、j2(j12和j22)和g2(g12和g22)可以在逐个延迟一个周期的状态下被顺序地应用。在第三周期t3,可以同时生成第二输出数据p12、p11、p32和p31。在第四周期t4,可以同时生成第二输出数据p22、p21、p42和p41,并且可以在逐个延迟一个周期的状态下顺序地生成第二输出数据p12、p11、p32和p31以及第二输出数据p22、p21、p42和p41。

61.图8a至图8d是示出根据本公开示例实施例的部分脉动阵列的第二卷积运算的图。

62.参照图8a,在第一周期t1,处理元件pe11可以将第二输入数据c11与第二权重数据d11相乘(c11

×

d11)以获得第二相乘结果r111'。处理元件pe13可以将第二输入数据g11与第二权重数据f11相乘(g11

×

f11)以获得第二相乘结果r131'。处理元件pe31可以将第二输入数据i11与第二权重数据j11相乘(i11

×

j11)以获得第二相乘结果r311'。处理元件pe33可以将第二输入数据l11与第二权重数据m11相乘(l11

×

m11)以获得第二相乘结果r331'。

63.参照图8b,在第二周期t2,处理元件pe11可以将第二输入数据c12与第二权重数据d21相乘(c12

×

d21)以获得第二相乘结果r112',并且可以将第二相乘结果r111'与第二相乘结果r112'相加以获得第四部分累加结果e11。处理元件pe12可以将第二输入数据c11与第二权重数据d12相乘(c11

×

d12)以获得第二相乘结果r121'。处理元件pe21可以将第二输入数据c21与第二权重数据d11相乘(c21

×

d11)以获得第二相乘结果r211'。部分脉动阵列10-4至10-8的处理元件也可以通过其操作获得图8b所示的结果。

64.参照图8c,在第三周期t3,处理元件pe12可以将第二输入数据c11与第二权重数据d22(c11

×

d22)相乘以获得第四相乘结果r122',并且可以将第四相乘结果r121'与第四相乘结果r122'相加以获得第四部分累加结果e12。处理元件pe21可以将第二输入数据c22与第二权重数据d21相乘(c22

×

d21)以获得第二相乘结果r212',可以将第二相乘结果r211'与第二相乘结果r212'相加以获得第四部分累加结果e21,并且可以将第四部分累加结果e11与第五部分累加结果e21相加以生成第六部分累加结果e11+e21作为输出数据p11。处理元件pe22可以将第二输入数据c21与第二权重数据d12相乘(c21

×

d12)以获得第四相乘结果r221'。部分脉动阵列10-4至10-8的处理元件也可以通过其操作获得图8c所示的结果。

65.参照图8d,在第四周期t4,处理元件pe22可以将第二输入数据c22与第二权重数据d22相乘(c22

×

d22)以获得第二相乘结果r222',可以将第二相乘结果r221'与第二相乘结果r222'相加以获得第四部分累加结果e22,并且可以将第四部分累加结果e22与第五部分累加结果e12相加以生成第六部分累加结果作为输出数据p21。部分脉动阵列10-4至10-8的处理元件也可以通过其操作获得图8d所示的结果。

66.根据示例实施例,图3所示的第一输入矩阵a可以被分为四个部分,其是图6a至图6d所示的第二输入矩阵c、f、i、l,第一权重矩阵b可以被分为四个部分,其是图6a至图6d的第二权重矩阵d、g、j和m,四个部分脉动阵列10-2、10-4、10-6和10-8执行第二卷积运算以分别生成第二输出数据p11和p21、p31和p41、p12和p22、以及p32和p42,并且八个第二输出数据p11、p21、p31、p41、p12、p22、p32和p42可以由累加器18相加以生成输出数据。在这种情况下,生成的输出数据可以与第一输入矩阵a和第一权重矩阵b的第一卷积结果数据o相同。也就是说,可以在减少卷积运算时间的同时生成相同的卷积结果数据。

67.在上述示例实施例中,第一输入数据和第二输入数据可以是图像数据,第一权重数据和第二权重数据可以是过滤数据。此外,在上述示例实施例中,加速器可以被包括在半导体存储装置中。

68.在本公开示例实施例中,在卷积运算期间,可以依据权重矩阵的大小可变地重新配置脉动阵列的矩阵的大小,从而可以同时执行卷积运算。也就是说,在权重矩阵的大小小于脉动阵列的矩阵的大小的情况下,部分脉动阵列可以并行执行卷积运算,从而可以减少运算时间。因此,可以提高包括脉动阵列的加速器的性能。

69.尽管已经参照附图描述了本发明构思的示例实施例,但是本领域技术人员将理解,可以进行各种修改而不脱离本发明构思的范围并且不改变其本质特征。因此,上述实施例应仅被认为是描述性的,而不是为了限制的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1