内存控制器、内存、内存控制方法及相关设备与流程

本发明实施例涉及数据存取领域,尤其涉及一种内存控制器、内存、内存控制方法及相关设备。

背景技术:

1、内存(memory,mem)又叫存储器,其作用是用于暂时存放中央处理器(centralprocessing unit,cpu)中的运算数据,以及与硬盘等外部存储器交换数据。而在计算机系统中,内存控制器(memory controller,mc)用于管理与规划cpu与mem之间的数据传输。一般而言,衡量mem性能有两个重要的参数:带宽和延时,其中,延时是指从mc对mem发送读命令到mem返回读数据之间的时间间隔。

2、然而,由于mc和mem之间的数据通道是读写分时复用的,当数据通道在传输写数据时无法传输读数据,导致mem的时延严重。

3、如何解决上述问题,是本领域技术人员正在研究的热点。

技术实现思路

1、本技术提供一种内存控制器、内存、内存控制方法及相关设备,可以有效减小内存的时延。

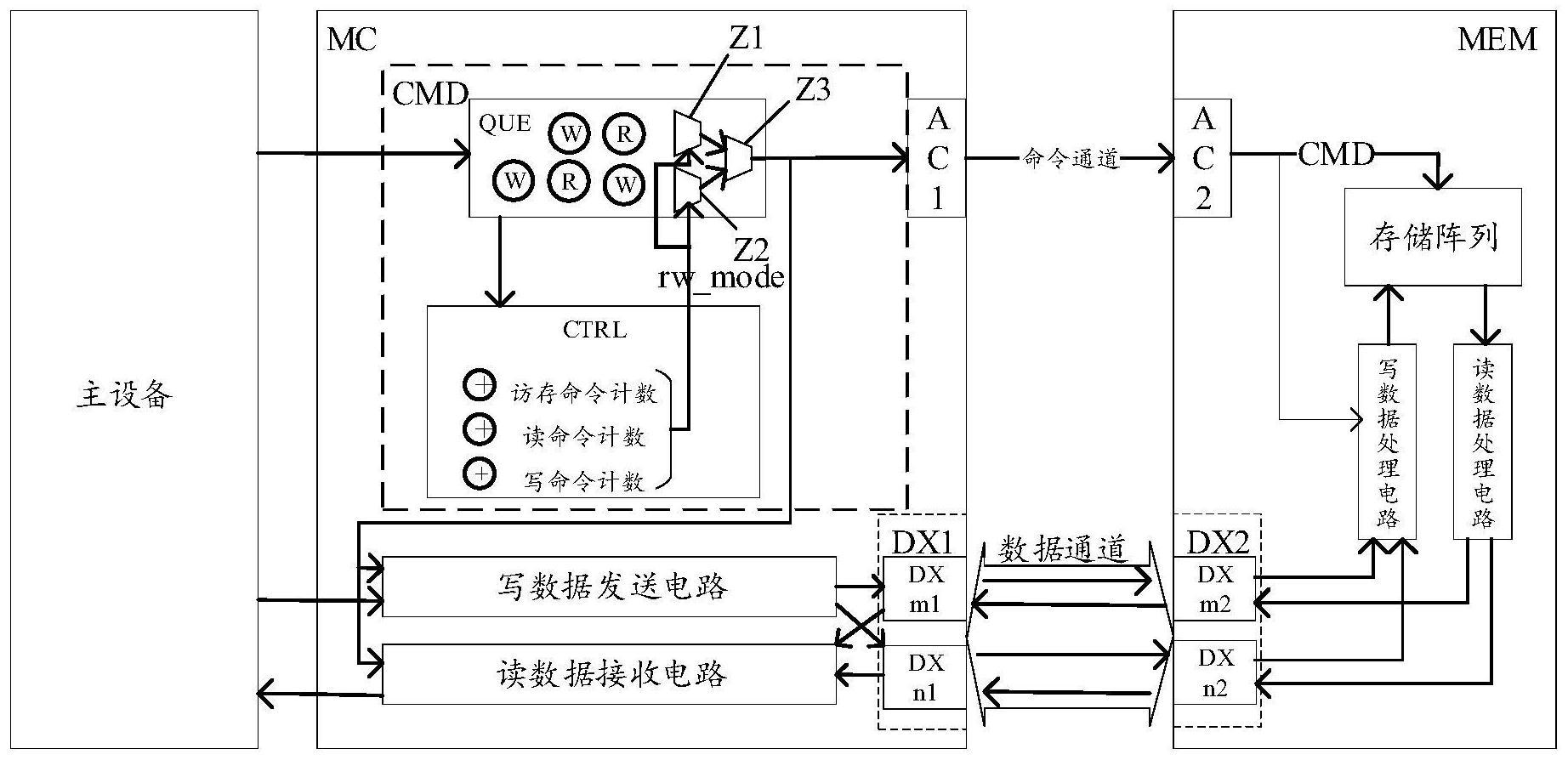

2、第一方面,本技术提供了一种内存控制器,该内存控制器包括第一数据通道接口,第一命令通道接口和第一处理电路。

3、第一数据通道接口用于通过数据通道与内存进行数据通信。上述数据通道的位宽为x。其中,数据通道的x位中的m位宽为第一通道,数据通道的x位中的n位宽为第二通道,x为大于或等于2的整数,m、n均为大于或等于1的整数。

4、第一数据通道接口的工作模式包括第一模式和第二模式中的至少一种。

5、第一模式为第一通道为接收通道且第二通道为发送通道。

6、第二模式为第一通道为接收通道且第二通道为发送接收分时复用通道。

7、而第一命令通道接口用于通过命令通道与内存进行命令通信。

8、第一处理电路,用于确定第一数据通道接口的目标工作模式,目标工作模式包括第一模式和第二模式中的至少一种。接收访存命令,通过第一命令通道接口将访存命令发送至内存。通过目标工作模式下的第一数据通道接口执行与访存命令对应的访存操作。

9、具体地,x位的数据通道中的m位宽、n位宽分别为第一通道、第二通道,第一通道、第二通道的数据位不存在重复,例如,数据通道具有十六位,第一位至第八位为第一通道,第九位至第十六位为第二通道。又例如,数据通道具有六十四位,第一位至第八位为第一通道,第五十七位至第六十四位为第二通道。而访存命令包括读取内存的第一数据的读命令和/或向内存写入第二数据的写命令。

10、本方案中,通过将内存控制器和内存之间的数据通道拆分得到任意位宽组合的两个数据通道,即第一通道和第二通道。而且第一数据通道接口具有第一模式和第二模式中的至少一种工作模式,使得第一通道和第二通道两个通道支持并行传输读写数据,因此,相比现有技术,可以有效降低内存的时延。

11、在第一方面的一种可能的实施方式中,上述内存控制器还包括写数据发送电路和/或读数据接收电路。其中,写数据发送电路用于接收第二数据,并根据第一处理电路的指示将第二数据通过目标工作模式下的第一数据通道接口发送至内存。而读数据接收电路用于根据第一处理电路的指示通过目标工作模式下的第一数据通道接口接收内存发送的第一数据。

12、本方案中,设置写数据发送电路和/或读数据接收电路以辅助完成访存操作。

13、在第一方面的一种可能的实施方式中,第一数据通道接口的工作模式还包括第三模式、第四模式、第五模式、第六模式和第七模式中的至少一种。

14、第三模式为第一通道为第一接收通道、且第二通道为第二接收通道。第一通道和第二通道为彼此独立的两个接收通道,第一接收通道和第二接收通道可以分别服务于不同的读命令。例如,第一接收通道用于接收读命令a对应的读数据,第二接收通道用于接收读命令b对应的读数据。

15、第四模式为第一通道和第二通道合并作为一个接收通道。第一通道和第二通道合二为一作为一个接收通道,即内存控制器和内存之间的数据通道作为接收通道,第一通道和第二通道共同服务同一个读命令。例如,第一通道和第二通道用于接收读命令a对应的读数据。

16、第五模式为第一通道为第一发送通道、且第二通道为第二发送通道。第一通道和第二通道为彼此独立的两个发送通道,第一发送通道和第二发送通道可以分别服务于不同的写命令。例如,第一发送通道用于发送写命令c对应的写数据,第二发送通道用于发送写命令d对应的写数据。

17、第六模式为第一通道和第二通道合并作为一个发送通道。第一通道和第二通道合二为一作为一个发送通道,即内存控制器和内存之间的数据通道作为发送通道,第一通道和第二通道共同服务同一个写命令。例如,第一通道和第二通道用于发送写命令c对应的写数据。

18、第七模式为第一通道为发送通道、且第二通道为发送接收分时复用通道。此时,第二通道可以分时作为发送通道和接收通道,第二通道具体的复用通道控制逻辑可以为现有技术中已有的控制逻辑,不做特别限定。

19、本方案中,还提供第一数据通道接口的多种工作模式,以满足内存控制器和内存之间不同的通信需求。例如,当访存命令均为读命令时,可以采用第三模式或第四模式。当访存命令均为写命令时,可以采用第五模式或第六模式。而当访存命令中写命令的含量大于设定阈值或者访存命令中读命令的含量小于设定阈值时,可以采用第七模式。

20、在第一方面的一种可能的实施方式中,内存控制器耦接于主设备和内存之间。而第一处理电路具体用于:接收来自主设备的模式切换命令,模式切换命令用于指示第一数据通道接口的工作模式。根据模式切换命令确定目标工作模式。

21、本方案中,内存控制器可以接受主设备对第一数据通道接口的工作模式的指定,内存控制器通过在主设备指定的工作模式下的第一数据通道接口完成访存命令对应的访存操作。

22、在第一方面的一种可能的实施方式中,第一处理电路具体用于:确定第一参数,第一参数用于指示第一预设时间段内的访存命令中读命令的含量。根据第一参数和至少一个第一参数阈值确定目标工作模式。

23、本方案中,内存控制器还可以根据第一参数来确定第一数据通道接口的目标工作模式,以根据访存命令的实际情况动态调整目标工作模式。

24、在第一方面的一种可能的实施方式中,第一参数包括以下各项中的任一项:第一预设时间段内读命令的个数、第一比例、读带宽、或第二比例。

25、其中,第一比例为第一预设时间段内,读命令与访存命令的总个数之比。读带宽为第一预设时间段内读命令的数据量。第二比例为读带宽与读写总带宽之比,读写总带宽为第一预设时间段内访存命令的数据量。

26、在第一方面的一种可能的实施方式中,第一处理电路具体用于:确定第二参数,第二参数用于指示第二预设时间段内的访存命令中写命令的含量。根据第二参数和至少一个第二参数阈值确定目标工作模式。

27、本方案中,内存控制器还可以根据第二参数来确定第一数据通道接口的目标工作模式,以根据访存命令的实际情况动态调整目标工作模式。

28、在第一方面的一种可能的实施方式中,第二参数包括以下各项中的任一项:第二预设时间段内写命令的个数、第三比例、写带宽、或第四比例。

29、其中,第三比例为第二预设时间段内,写命令与访存命令的总个数之比。写带宽为第二预设时间段内写命令的数据量。第四比例为写带宽与读写总带宽之比,读写总带宽为第二预设时间段内访存命令的数据量。

30、在第一方面的一种可能的实施方式中,第一处理电路包括队列池、第一仲裁引擎、第二仲裁引擎。

31、其中,队列池用于接收访存命令,访存命令包括至少一个读命令和至少一个写命令。

32、当目标工作模式为第一模式时,第一处理电路具体用于:通过第一仲裁引擎对至少一个读命令进行仲裁处理确定需要执行的第一读命令;以及通过第二仲裁引擎对至少一个写命令进行仲裁处理确定需要执行的第一写命令。

33、当目标工作模式为第二模式时,第一处理电路具体用于:通过第一仲裁引擎对至少一个读命令进行仲裁处理确定需要执行的第二读命令;以及通过第二仲裁引擎对至少一个读命令和至少一个写命令进行仲裁处理确定需要执行的目标命令,目标命令为第二写命令或第三读命令。

34、本方案中,在第一数据通道接口的第一模式或第二模式下时,第一处理电路通过第一仲裁引擎和第二仲裁引擎分别进行命令仲裁,以将队列池中的访存命令分配在第一通道或第二通道上执行。

35、在第一方面的一种可能的实施方式中,第一处理电路还包括第三仲裁引擎。

36、当目标工作模式为第一模式时,第一处理电路具体用于通过第三仲裁引擎对第一读命令和第一写命令进行仲裁处理以确定发送至内存的目标发送命令。

37、或者,

38、当目标工作模式为第二模式时,第一处理电路用于通过第三仲裁引擎对第二读命令和目标命令进行仲裁处理以确定发送至内存的目标发送命令。

39、本方案中,内存控制器和内存之间的访存命令为串行发送的方式,以使内存按顺序响应访存命令,有效提升访存命令的响应效率。

40、在第一方面的一种可能的实施方式中,当目标工作模式为第一模式,且目标发送命令为第一读命令时,第一处理电路通过第一通道接收第一读命令对应的读数据。当目标工作模式为第一模式,且目标发送命令为第一写命令时,第一处理电路通过第二通道发送第一写命令对应的写数据。

41、当目标工作模式为第二模式,且目标发送命令为第二读命令时,第一处理电路通过第一通道接收第二读命令对应的读数据。当目标工作模式为第二模式,且目标发送命令为目标命令时,第一处理电路通过第二通道发送目标命令对应的写数据,或者,第一处理电路通过第二通道接收目标命令对应的读数据。

42、在第一方面的一种可能的实施方式中,目标发送命令包括通道指示信息或第一模式指示信息,通道指示信息用于指示传输目标发送命令对应的数据的目标通道,目标通道为第一通道或第二通道,第一模式指示信息用于指示目标工作模式。

43、本方案中,通过在目标发送命令中增加通道指示信息,以使内存知晓在哪个目标通道上传输目标发送命令对应的数据,有效提升命令响应速度。另外,也可以通过在目标发送命令中携带第一模式指示信息,以使内存知晓数据通道在处理该目标发送命令时应该采用的目标工作模式,有利于提升目标发送命令的处理速度。

44、在第一方面的一种可能的实施方式中,第一处理电路,还用于:

45、通过第一命令通道接口向内存发送配置命令,配置命令包括目标工作模式。

46、本方案中,内存控制器还可以通过向内存发送配置命令,以告知内存第一数据通道接口的目标工作模式,使得内存控制器和内存之间可以配合工作,进而完成访存命令对应的访存操作。

47、在第一方面的一种可能的实施方式中,第一处理电路,具体用于:

48、根据访存命令确定目标工作模式;访存命令包括第二模式指示信息,第二模式指示信息用于指示目标工作模式。

49、本方案中,通过在访存命令中携带的第二模式指示信息,内存控制器可以确定数据通道在处理该访存命令时的目标工作模式,有利于提升访存命令的处理速度。

50、第二方面,本技术还提供一种内存控制方法,应用于内存控制器。该内存控制器包括用于通过数据通道与内存进行数据通信的第一数据通道接口。

51、其中,数据通道的位宽为x,x位的数据通道中的m位宽为第一通道,x位的数据通道中的n位宽为第二通道,x为大于或等于2的整数,m、n均为大于或等于1的整数。

52、第一数据通道接口的工作模式包括第一模式和第二模式中的至少一种,第一模式为第一通道为接收通道且第二通道为发送通道,第二模式为第一通道为接收通道且第二通道为发送接收分时复用通道。

53、上述内存控制方法包括:确定第一数据通道接口的目标工作模式,目标工作模式包括第一模式和第二模式中的至少一种;接收访存命令,将访存命令发送至内存;通过目标工作模式下的第一数据通道接口执行与访存命令对应的访存操作。

54、在第二方面的一种可能的实施方式中,访存命令包括读取内存的第一数据的读命令和/或向内存写入第二数据的写命令。

55、在第二方面的一种可能的实施方式中,内存控制方法还包括:

56、接收第二数据,并将第二数据通过目标工作模式下的第一数据通道接口发送至内存。

57、和/或,

58、通过目标工作模式下的第一数据通道接口接收内存发送的第一数据。

59、在第二方面的一种可能的实施方式中,第一数据通道接口的工作模式还包括第三模式、第四模式、第五模式、第六模式和第七模式中的至少一种。

60、第三模式为第一通道为第一接收通道、且第二通道为第二接收通道。

61、第四模式为第一通道和第二通道合并作为一个接收通道。

62、第五模式为第一通道为第一发送通道、且第二通道为第二发送通道。

63、第六模式为第一通道和第二通道合并作为一个发送通道。

64、第七模式为第一通道为发送通道、且第二通道为发送接收分时复用通道。

65、在第二方面的一种可能的实施方式中,内存控制器耦接于主设备和内存之间,确定数据通道的目标工作模式,包括:

66、接收来自主设备的模式切换命令,模式切换命令用于指示第一数据通道接口的工作模式。根据模式切换命令确定目标工作模式。

67、在第二方面的一种可能的实施方式中,确定数据通道的目标工作模式,包括:

68、确定第一参数,第一参数用于指示第一预设时间段内的访存命令中读命令的含量。根据第一参数和至少一个第一参数阈值确定目标工作模式。

69、在第二方面的一种可能的实施方式中,第一参数包括以下各项中的任一项:第一预设时间段内读命令的个数、第一比例、读带宽、或第二比例。

70、其中,第一比例为第一预设时间段内,读命令与访存命令的总个数之比。读带宽为第一预设时间段内读命令的数据量。第二比例为读带宽与读写总带宽之比,读写总带宽为第一预设时间段内访存命令的数据量。

71、在第二方面的一种可能的实施方式中,确定数据通道的目标工作模式,包括:

72、确定第二参数,第二参数用于指示第二预设时间段内的访存命令中写命令的含量。根据第二参数和至少一个第二参数阈值确定目标工作模式。

73、在第二方面的一种可能的实施方式中,第二参数包括以下各项中的任一项:第二预设时间段内写命令的个数、第三比例、写带宽、或第四比例。

74、其中,第三比例为第二预设时间段内,写命令与访存命令的总个数之比。写带宽为第二预设时间段内写命令的数据量。第四比例为写带宽与读写总带宽之比,读写总带宽为第二预设时间段内访存命令的数据量。

75、在第二方面的一种可能的实施方式中,内存控制器还包括队列池、第一仲裁引擎、第二仲裁引擎。其中,队列池,用于接收访存命令,访存命令包括至少一个读命令和至少一个写命令。

76、进一步地,内存控制方法还包括:当目标工作模式为第一模式时,通过第一仲裁引擎对至少一个读命令进行仲裁处理确定需要执行的第一读命令;以及通过第二仲裁引擎对至少一个写命令进行仲裁处理确定需要执行的第一写命令。

77、当目标工作模式为第二模式时,通过第一仲裁引擎对至少一个读命令进行仲裁处理确定需要执行的第二读命令;以及通过第二仲裁引擎对至少一个读命令和至少一个写命令进行仲裁处理确定需要执行的目标命令,目标命令为第二写命令或第三读命令。

78、在第二方面的一种可能的实施方式中,内存控制器还包括第三仲裁引擎,内存控制方法还包括:

79、当目标工作模式为第一模式时,通过第三仲裁引擎对第一读命令和第一写命令进行仲裁处理以确定发送至内存的目标发送命令。

80、或者,

81、当目标工作模式为第二模式时,通过第三仲裁引擎对第二读命令和目标命令进行仲裁处理以确定发送至内存的目标发送命令。

82、在第二方面的一种可能的实施方式中,内存控制方法还包括:

83、当目标工作模式为第一模式,且目标发送命令为第一读命令时,通过第一通道接收第一读命令对应的读数据。当目标工作模式为第一模式,且目标发送命令为第一写命令时,通过第二通道发送第一写命令对应的写数据。

84、当目标工作模式为第二模式,且目标发送命令为第二读命令时,通过第一通道接收第二读命令对应的读数据。当目标工作模式为第二模式,且目标发送命令为目标命令时,通过第二通道发送目标命令对应的写数据,或者,通过第二通道接收目标命令对应的读数据。

85、在第二方面的一种可能的实施方式中,目标发送命令包括通道指示信息或第一模式指示信息,通道指示信息用于指示传输目标发送命令对应的数据的目标通道,目标通道为第一通道或第二通道,第一模式指示信息用于指示目标工作模式。

86、在第二方面的一种可能的实施方式中,内存控制方法还包括:

87、向内存发送配置命令,配置命令包括目标工作模式。

88、在第二方面的一种可能的实施方式中,确定数据通道的目标工作模式,包括:根据访存命令确定目标工作模式;访存命令包括第二模式指示信息,第二模式指示信息用于指示目标工作模式。

89、第三方面,本技术还提供一种内存,内存耦合于内存控制器。该内存包括第二数据通道接口、第二命令通道接口和第二处理电路。

90、第二数据通道接口用于通过数据通道与内存控制器的第一数据通道接口进行数据通信。数据通道的位宽为x,其中,x位的数据通道中的m位宽为第一通道,x位的数据通道中的n位宽为第二通道,x为大于或等于2的整数,m、n均为大于或等于1的整数。第一数据通道接口的工作模式包括第一模式和第二模式中的至少一种。第一模式为第一通道为接收通道且第二通道为发送通道。第二模式为第一通道为接收通道且第二通道为发送接收分时复用通道。

91、第二命令通道接口用于接收来自内存控制器的访存命令。

92、第二处理电路用于通过第二数据通道接口执行与访存命令相应的访存操作。

93、在第三方面的一种可能的实施方式中,访存命令包括读取内存的第一数据的读命令和/或向内存写入第二数据的写命令。

94、在第三方面的一种可能的实施方式中,内存还包括存储阵列,第二处理电路包括读数据处理电路和/或写数据处理电路。

95、读数据处理电路,用于响应读命令从存储阵列中获取读命令对应的读数据,并将读数据通过第二数据通道接口发送至内存控制器。

96、写数据处理电路,用于响应写命令通过第二数据通道接口获取写命令对应的写数据,并将写数据写入存储阵列中。

97、在第三方面的一种可能的实施方式中,第一数据通道接口的工作模式还包括第三模式、第四模式、第五模式、第六模式和第七模式中的至少一种。

98、第三模式为第一通道为第一接收通道、且第二通道为第二接收通道。

99、第四模式为第一通道和第二通道合并作为一个接收通道。

100、第五模式为第一通道为第一发送通道、且第二通道为第二发送通道。

101、第六模式为第一通道和第二通道合并作为一个发送通道。

102、第七模式为第一通道为发送通道、且第二通道为发送接收分时复用通道。

103、在第三方面的一种可能的实施方式中,访存命令包括通道指示信息或第一模式指示信息,通道指示信息用于指示传输访存命令对应的数据的目标通道,目标通道为第一通道或第二通道,第一模式指示信息用于指示所述目标工作模式。其中,本实施方式中的访存命令为第一方面中的目标发送命令。

104、在第三方面的一种可能的实施方式中,第二命令通道接口,还用于接收来自内存控制器的配置命令,配置命令包括第一数据通道接口的目标工作模式。

105、第四方面,本技术还提供一种电子设备,包括:如第一方面所述的内存控制器和第三方面所述的内存。

106、第五方面,本技术还提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行以实现如第二方面所述的内存控制方法。

107、第六方面,本技术还提供一种包含指令的计算机程序产品,当所述计算机程序产品在计算机上运行时,使得计算机执行第二方面所述的内存控制方法。

108、第七方面,提供一种芯片,所述芯片包括处理器与数据接口,所述处理器通过所述数据接口读取存储器上存储的指令,执行第二方面所述的内存控制方法。

109、可选地,作为一种实现方式,所述芯片还可以包括存储器,所述存储器中存储有指令,所述处理器用于执行所述存储器上存储的指令,当所述指令被执行时,所述处理器用于执行第二方面所述的内存控制方法。

- 还没有人留言评论。精彩留言会获得点赞!