一种基于非易失存储器的加密存算一体的实现方法

1.本发明涉及存储领域,用存储器计算并进行加密和纠错,具体而言,是利用 存储器本身的随机噪声对存算一体计算的结果加密并纠错。

背景技术:

2.在如今的大数据时代,对算力的要求大大增加,传统冯诺依曼架构中计算和 存储分开的设计使得计算所需的能耗和速度很大一部分耗费在数据运输中,造成 不必要的访存延迟和访存功耗。因而能够同时在存储器中完成存储和计算的存算 一体架构,拥有着极大的优势。而传统的存算一体架构设计常集中于功耗和速度 上的提升,极少涉及信息安全的领域。

3.许多新兴的非易失性存储器,例如忆阻器(rram)、相变存储器(pcm)和 铁电存储器(feram)以及传统的闪存,均已被证明可以较好地应用在人工智能 领域,减少数据传输过程中的时间和功耗损失。非易失存储器具有随机电报噪声, 该噪声具有随机性和不可预测性,可以将噪声导致的电流跳变应用在计算中,达 到加密的效果。

技术实现要素:

4.针对现有技术的缺陷,本发明提供一种基于非易失存储器的加密存算一体的 实现方法,利用闪存本身的随机电报噪声对计算进行加密,实现加密存算一体。

5.为了解决所述技术问题,本发明采用的技术方案是:一种基于非易失存储器 的加密存算一体的实现方法,本方法使用非易失存储器构成加密存算一体架构, 非易失存储器同时承担处理数据和加密的功能,加密时,先将存储器编程到正确 的存储状态,然后以编程电流积分值与真实电流积分值的差作为密钥,正式加密 计算时,将计算中的向量和矩阵分别映射为非易失存储器的栅极脉冲时间和编程 后的器件漏极电流,根据加密规则与解密规则进行加密和解密。

6.进一步的,在非易失存储器的亚阈值区进行密钥生成。

7.进一步的,采用ac测量方法加速加密过程,ac测量方法有两个栅极电压, 分别为前置电压和测量电压,前置电压和测量电压交替施加,使得非易失存储器 随机电报噪声的发射和捕获时间随着施加频率的增加而降低。

8.进一步的,所述非易失存储器包括闪存、铁电晶体管、阻变存储器和相变存 储器。

9.进一步的,加密规则为:

[0010][0011]

其中i

t

表示编程后的器件漏极电流,δi

t

表示密钥,t表示非易失存储器的栅 极脉

冲时间,qr表示加密结果,m、n表示非易失存储器阵列的行数和列数;

[0012]

解密规则为:

[0013][0014]

其中ir表示真实电流值,cr表示解密结果。

[0015]

本发明的有益效果:本发明利用非易失存储器的随机电报噪声对计算进行加 密,在解密的同时还达到了纠错的效果。随机电报噪声由于随机性和不可预测性, 在真随机数发生器和硬件指纹等领域有着丰富的应用。

附图说明

[0016]

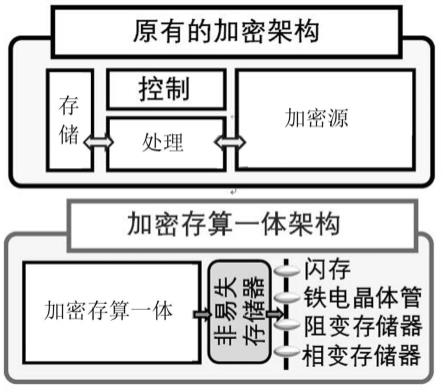

图1是加密存算一体架构的示意图;

[0017]

图2是器件电流与器件编程操作示意图;

[0018]

图3是实施例1所述加密过程与解密过程示意图;

[0019]

图4是器件驱动电压不同对电报噪声幅值带来的影响示意图;

[0020]

图5是存储器工作在线性区和亚阈值区的对比示意图;

[0021]

图6是器件2比特存储的电流积分分布示意图;

[0022]

图7是dc测试结果及ac测试模式示意图;

[0023]

图8是ac测试结果示意图;

[0024]

图9是本发明加密解密后的结果示意图;

[0025]

图10是本发明在不同架构、不同矩阵尺寸下加密解密的结果示意图。

具体实施方式

[0026]

下面结合附图和具体实施例对本发明作进一步的说明。

[0027]

实施例1

[0028]

本实施例公开一种基于非易失存储器的加密存算一体的实现方法,如图1 所示,本方法使用非易失存储器构成加密存算一体架构,加密源和处理器均在存 储器内部处理,无需额外加密电路,非易失存储器同时承担处理数据和加密的功 能。非易失存储器可以采用闪存、铁电晶体管、阻变存储器和相变存储器中的一 种,本实施例采用闪存进行说明。

[0029]

晶体管电流受内部缺陷的影响,电流会产生一定的跳变,使得编程后的电流 积分和真实的电流积分有所不同,从而设计加密算法。图2(a)是对闪存进行编程 的操作流程图。图2(b)是闪存操作时的编程、擦除、读取电压脉冲示意图,图2 (c)展示了闪存的阵列设计,且闪存电流存在一定的跳动,编程的目标电流为起初 读取到的电流,真正的电流如图所示,闪存内部的缺陷导致了这种电流跳变,也 就是随机电报噪声,以致每个时段的电流均不一致,但在一段积分时间内,电流 的积分量是固定的。利用编程后的电流积分值与真实的电流积分值的差作为密钥, 从而设计加密算法。

[0030]

基于此,本实施例所述基于非易失存储器的加密存算一体的实现方法将加密 计

算中的向量和矩阵分别映射为非易失存储器的栅极脉冲时间和编程后的器件 漏极电流,以非易失存储器漏极的电流真实值与编程电流值积分的差作为密钥, 根据加密规则与解密规则进行加密和解密。

[0031]

具体如图3所示,将器件编程到正确的态后,也将真实电流积分量与目标电 流积分量(编程电流积分量)的差别记录为密钥。在正式进行矩阵向量乘法时, 由于噪声的存在,计算得到的是噪声也一同进行积分的加密后的结果,只有经过 密钥处理后,才能得到准确的计算结果,也就是目标电流的积分量。

[0032]

加密规则为:

[0033][0034]

其中i

t

表示编程后的器件漏极电流,δi

t

表示密钥,t表示非易失存储器的栅 极脉冲时间,qr表示加密结果,m、n表示非易失存储器阵列的行数和列数;

[0035]

解密规则为:

[0036][0037]

其中ir表示真实电流值,cr表示解密结果。

[0038]

所述亚阈值区,即晶体管工作处于栅极电压略高于阈值电压的状态,具体是 栅极电压与阈值电压的差值小于0.2v,此时漏极电流较小且随机电报噪声幅度较 大,真实电流的积分量与目标电流的积分量有较大的差距,即足以改变存储态, 影响计算结果的差距。图4(a)示了不同驱动电压下电报噪声幅值趋势的变化。 相比线性区,亚阈值区的电报噪声幅值大大增大,且越靠近阈值电压,电报噪声 幅值越大。图4(b)详细解释了在近阈值区电报噪声更大的这种趋势,意味着近 阈值区更大的电报噪声更利于加密设计。因此选取亚阈值区进行密钥生成。图4 (a)和图4(b)中,v

th

表示阈值电压,vd表示漏极电压,id表示漏极电流。

[0039]

图5显示了亚阈值区与线性区在功耗、器件可靠性、电报噪声三个维度的性 能对比,由图可以得知,亚阈值区除了电报噪声δid/id较大,并且功耗更低,因 此选取亚阈值区进行计算。图5中,v

over

表示处于亚阈值区或者线性区的漏极电 压。

[0040]

图6(a)展示了计算时电流调整的态分布。该计算采用4个不同的态(不同的 电流大小)进行计算,其中p0为编程态,p1、p2、p3由于器件噪声产生的电流 跳动,积分值呈一定的分布(虽然相同态的编程电流相同)。因而会出现态之间 跨越的现象,因而计算结果变化。图6(b)展示了阵列中不同器件积分量的积累 之间的差异,也就是计算误差的大小,可以看到均在5%的波动范围内。

[0041]

所述ac测量,不同于传统栅极和漏极电压都固定的测量方法,栅极电压有 两个,

分为前置电压和测量电压,前置电压和测量电压交替施加,使得晶体管随 机电报噪声的发射和捕获时间随着施加频率的增加而大大降低,计算受缺陷发射 和捕获时间的影响较小。

[0042]

图7(a)是电报噪声的dc测试方法产生的最小发射和捕获时间之和。图7(b) 展示了ac测量的脉冲时序。由于积分时间受发射时间和捕获时间的影响,可以 使用ac的方法进行加速,ac方法分为低前置电压和高前置电压。两种方法的测 量电压均相同,根据前置时间段电压的高低区分。

[0043]

图8(a)是ac测试方法的测试结果,可以直观地观察到虽然测试时间相同, 但电报噪声出现的速度更快。图8(b)展示了随着测试频率的增加,发射时间和捕 获时间之和大大降低,从而减少缺陷出现的时间,加速计算。

[0044]

图9展示了32比特浮点数架构和32比特整型架构在加密和解密后的效果。 32比特浮点数加密后的结果波动更大。

[0045]

图10展示了不同矩阵大小下32比特浮点数和32比特整型的加密及解密统 计结果。加密时,32比特浮点数的波动更大。但经过解密,32比特浮点数的精 度更高。

[0046]

以上描述的仅是本发明的基本原理和优选实施例,本领域技术人员根据本发 明做出的改进和替换,属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1