一种用于微处理器缓冲区溢出的硬件检测与防御机制

1.本发明属于处理器硬件安全与大规模数字集成电路领域,特别涉及一种硬件检测与防御技术。

背景技术:

2.缓冲区溢出攻击指的是:在处理器中由于程序没有检查缓冲区边界条件或边界检查机制被绕过,而导致写入缓冲区的数据超过了所分配的缓冲区边界,从而覆盖相邻的内存区域,导致存储在处理器缓冲区的局部变量被篡改,甚至有使得处理器控制流被劫持的危险。一般来说,缓冲区溢出分为栈溢出与堆溢出。栈溢出主要有两种情况:(1)局部数据过大,超过了编译器为其申请的栈空间,导致栈向上溢出,覆盖已存在的数据;(2)函数递归次数过多,导致栈空间快速的向下生长,从而覆盖了heap堆、bss段与data段的数据。堆溢出是一种内存向上溢出的行为,与栈溢出(1)的情况类似。缓冲区溢出攻击可造成处理器运行崩溃、访问控制丢失、控制流被劫持等危害。

3.目前针对处理器缓冲区溢出检测与防御方法主要有四种:

4.(1)设置堆栈canaries值,当缓冲区溢出覆盖返回地址时,通过检测canaries值是否被篡改实现缓冲区溢出攻击的检测,如“a.de,a.basu,s.ghosh and t.jaeger,"hardware assisted buffer protection mechanisms for embedded risc-v,"in ieee transactions on computer-aided design of integrated circuits and systems,vol.39,no.12,pp.4453-4465,dec.2020,doi:10.1109/tcad.2020.2984407.”利用物理不可克隆函数(puf)与真随机数生成器(trng)生成随机canaries值;

5.(2)对处理器运行中的返回地址进行保护,防止处理器遭受到更为严重的控制流劫持攻击,如“d.asmit,s ghosh.heapsafe:securing unprotected heaps in risc-v.arxiv abs/2105.08712 2021.”通过给返回地址增加安全标签位来保证返回地址的安全性,“张雨昕,芮志清,李威威,等.pec-v:基于risc-v协处理器的内存溢出防御机制.计算机系统应用,2021,30(11):9.”利用puf将返回地址进行加密/解密,“wang.y,wu.j,yue.t,ning.z and zhang.f.rettag:hardware-assisted return address integrity on risc-v.proceedings of the 15th european workshop on systems security.2022”通过在处理器硬件层面给返回地址添加加密的指针验证码来保证处理器返回地址的完整性;

6.(3)保证处理器程序控制流完整性,在程序运行时确保遵循构建的程序控制流图,以实现对控制流劫持攻击的防御,如“shrivastava.k r,concessao.k j,hota.c.code tamper-proofing using dynamic canaries.2019 25th asia-pacific conference on communications(apcc).pp.238-243.2019”通过使用动态canaries值在函数调用点和返回点进行一系列xor计算来确保控制流的完整性;

7.(4)在处理器硬件层面实现缓冲区的边界检查,如“s.chiamwongpaet and k.piromsopa,boundary bit:architectural bound checking for buffer-overflow protection,ecti-cit transactions,vol.14,no.2,pp.162

–

173,sep.2020.”通过编译器

设置一个边界位来界定一个对象,然后在每次内存访问时,硬件将使用边界位动态检查对象的边界;

8.上述目前针对处理器缓冲区溢出检测与防御方法(1)、(2)、(3)只能检测出处理器函数返回地址遭受到了缓冲区溢出攻击,无法实现缓冲区数组越界这一溢出行为的检测,且其防御措施会导致处理器停止运行,(2)中对返回地址加密/解密的方法会导致处理器崩溃跑飞。方法(4)的缺点在于:(a)其边界位的设置是通过编译器实现,存在绕过该机制的危险;(b)每次内存访问都需要花费一定的时间完成访问对象边界的扫描,影响处理器运行性能。

技术实现要素:

9.为解决上述技术问题,本发明提出一种用于微处理器缓冲区溢出的硬件检测与防御机制,基于微处理器指令的自定义扩展与微处理器中程序控制流图的实时构建,实现在微处理器的硬件层面完成缓冲区溢出行为的实时检测与返回地址的实时保护,根据实时检测结果屏蔽处理器当前执行指令访存缓冲区的权限。

10.本发明采用的技术方案为:一种用于微处理器缓冲区溢出的硬件检测与防御机制,包括:缓冲区溢出检测电路一、缓冲区溢出检测电路二、以及缓冲区溢出防御电路;

11.缓冲区溢出检测电路一基于微处理器指令的自定义扩展实现缓冲区溢出提前一个时钟周期的预先检测;缓冲区溢出检测电路二基于微处理器中程序控制流图实现返回地址篡改攻击提前一个时钟周期的预先检测;

12.缓冲区溢出防御电路根据缓冲区溢出检测电路一或缓冲区溢出检测电路二的检测结果,完成对当前处理器执行指令访存缓冲区权限的恢复或屏蔽。

13.本发明的有益效果:本发明通过基于微处理器指令的自定义扩展的缓冲区溢出检测电路,结合微处理器编译器与硬件电路实现针对缓冲区溢出攻击提前一个时钟周期的预先检测,并且可实时对数组越界的溢出行为进行实时检测;通过基于微处理器中程序控制流图实时构建的缓冲区溢出检测电路,使用纯硬件的方式保证该检测机制不会被攻击者绕过,同时针对缓冲区溢出攻击覆盖函数返回地址这一恶意行为可提前一个时钟周期得到预先检测结果;通过缓冲区溢出防御电路,可根据两个缓冲区溢出检测电路的预先检测结果,在缓冲区溢出攻击执行完毕之前,屏蔽当前处理器执行指令访存缓冲区的权限,无效化微处理器遭受到的缓冲区溢出攻击,保证处理器可无视缓冲区溢出攻击继续正常执行程序;本发明具备以下优点:

14.(1)本发明通过基于微处理器指令的自定义扩展的缓冲区溢出检测电路,结合微处理器编译器与硬件电路实现针对缓冲区溢出攻击提前一个时钟周期的预先检测,并且可实时对数组越界的溢出行为进行实时检测;

15.(2)本发明通过基于微处理器中程序控制流图实时构建的缓冲区溢出检测电路,使用纯硬件的方式保证该检测机制不会被攻击者绕过,同时针对缓冲区溢出攻击覆盖函数返回地址这一恶意行为可提前一个时钟周期得到预先检测结果;

16.(3)本发明通过缓冲区溢出防御电路,可根据两个缓冲区溢出检测电路的预先检测结果,在缓冲区溢出攻击执行完毕之前,屏蔽当前处理器执行指令访存缓冲区的权限,无效化微处理器遭受到的缓冲区溢出攻击,保证处理器可不受缓冲区溢出攻击影响地正常运

行;

17.(4)本发明简单高效,无需占用的太多的硬件资源,只需要对微处理器内核进行微小修改,同时连续实时地采集微处理器译码阶段的指令及其有效信号、回写阶段的数据地址,便可轻易部署在微处理器中。

附图说明

18.图1为本发明提出的机制的功能结构框图。

19.图2为本发明提出的机制的部署在开源riscv处理器pulpino中的简图。

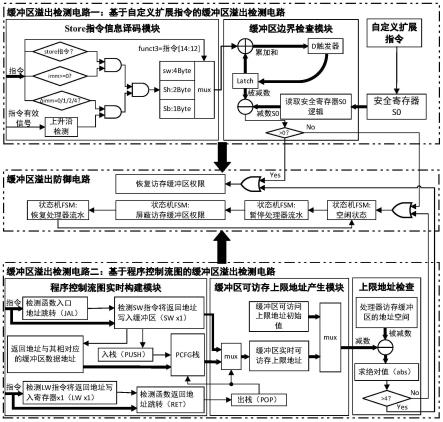

20.图3为测试本发明有效性而设计的缓冲区溢出攻击示意图。

21.图4为在基线处理器与部署本发明提出的机制的处理器上执行缓冲区溢出攻击示例的对照仿真结果图。

22.图5为使用本发明缓冲区溢出检测电路一对缓冲区溢出攻击进行实时检测仿真部分结果。

23.图6为使用本发明缓冲区溢出检测电路二对缓冲区溢出攻击进行实时检测仿真部分结果;

24.图7为本发明部署在riscv处理器pulpino上的面积资源消耗对比图。

具体实施方式

25.为便于本领域技术人员理解本发明的技术内容,下面结合附图对本发明内容进一步阐释。

26.实施例1

27.本实施例结合附图1对本发明的内容进行详细介绍:

28.如图1所示,一种用于微处理器缓冲区溢出的硬件检测与防御机制,包括两个缓冲区溢出检测电路、一个缓冲区溢出防御电路,两个缓冲区溢出检测电路通过连续实时采集并处理分析微处理器译码阶段的指令、指令有效信号、回写阶段访存缓冲区的数据地址,分别实现缓冲区溢出与返回地址篡改攻击提前一个时钟周期的预先检测,最后将检测结果输入给缓冲区防御电路完成对当前处理器执行指令访存缓冲区权限的屏蔽,以完成缓冲区溢出攻击提前一个时钟周期的预先防御。

29.缓冲区溢出检测电路一基于微处理器指令的自定义扩展实现缓冲区溢出提前一个时钟周期的预先检测;

30.缓冲区溢出检测电路二基于微处理器中程序控制流图实现返回地址篡改攻击提前一个时钟周期的预先检测。

31.如图1所示,缓冲区溢出检测电路一包括:store指令信息译码模块、缓冲区边界检查模块、自定义扩展指令以及安全寄存器;缓冲区溢出检测电路一对缓冲区溢出的检测过程为:

32.首先,根据微处理器指令的可自定义扩展性,通过修改处理器编译工具链部分源码与内核译码阶段、执行阶段的硬件逻辑,实现如图1所示的自定义扩展指令。自定义扩展指令在微处理器中执行可产生缓冲区溢出检测电路一的驱动信号与进行硬件层面边界检查所需的当前函数所申请的缓冲区空间大小参考值ref_bs。在编写c代码时,将自定义扩展

指令添加到可能发生缓冲区溢出的函数(如:gets()、fgets()、strcpy()、strncpy()、strlen()等)前,即可实现对函数进行硬件层面的缓冲区空间边界检查。

33.其次,实时采集微处理器译码阶段的指令与指令有效信号,根据store指令信息译码模块实时分析当前采集的有效指令(指令有效信号为高电平期间对应的指令即为有效指令)是否为store指令类型、指令所携带的立即数imm是否大于或等于0、store指令所携带立即数相较于上一个store指令所携带立即数的增量

△

imm是否为0/1/2/4,若同时满足以上条件则根据指令的funct3编码产生当前store指令即将消耗缓冲区空间的大小值yi,反之则将yi置为0,其中i为1到n,n表示连续检测到符合条件的有效指令的最计数值;

34.最后,缓冲区边界检查模块实时计算在当前函数段中缓冲区空间消耗大小值rt_bs,其中同时读取存储在安全寄存器s0中的函数所申请缓冲区空间大小值ref_bs,实时与rt_bs进行比较,若ref_bs-rt_bs≥0则在当前函数段不存在缓冲区溢出攻击,反之则存在缓冲区溢出攻击。

35.如图1所示,缓冲区溢出检测电路二包括:程序控制流图实时构建模块、缓冲区可访存上限地址产生模块、以及上限地址检查;缓冲区溢出检测电路二对返回地址篡改攻击的检测过程为:

36.首先,根据处理器指令流信息完成程序控制流图(program control flow graph,pcfg)实时构建,其步骤为:(1)实时采集微处理器译码阶段的指令与指令有效信号;(2)在采集到的有效指令中检测函数入口地址跳转指令(jal),且jal指令的目标寄存器(rd)为x1;(3)在(2)完成的基础上,再检测sw指令,且sw指令的源寄存器(rs2)为x1;(4)在(3)完成的基础上,将函数返回地址与其相对应的缓冲区数据地址进行入栈操作(push);(5)在采集到的有效指令中检测lw指令,且lw指令的目标寄存器(rd)为x1;(6)在(5)完成的基础上,再检测函数返回地址跳转指令jalr;(7)在(6)完成的基础上,将对栈的数据进行出栈操作(pop)。

37.其次,根据pcfg栈实时产生当前函数段缓冲区可访存的上限地址max_a,当程序控制流图实时构建模块处于push操作时,缓冲区实时可访存上限地址为将当前返回地址存入缓冲区所对应的数据地址;当程序控制流图实时构建模块处于pop操作时,缓冲区实时可访存上限地址为pcfg栈pop出的数据地址;根据指示pcfg栈是否开始构建的信号从缓冲区可访问上限地址初始值与缓冲区实时可访存上限地址中选择当前函数段缓冲区可访存的上限地址max_a。

38.最后,由上限地址检查模块实时采集处理器回写阶段访存缓冲区的数据地址rt_a,并实时与由缓冲区可访存上限地址产生模块的缓冲区可访存上限地址max_a进行比较,若|max_a-rt_a|》4则在处理器运行的当前函数段不存在对存储缓冲区的返回地址的溢出覆盖攻击,反之则存在对返回地址的溢出覆盖攻击,||表示求绝对值。

39.如图1所示,缓冲区溢出防御电路包括有限状态机fsm与store指令访存缓冲区权限控制逻辑,缓冲区溢出防御电路根据缓冲区溢出检测电路一或缓冲区溢出检测电路二的检测结果,完成对当前处理器执行store指令访存缓冲区权限的屏蔽,具体实现过程为:

40.首先,在有限状态机fsm的空闲状态时,等待两个缓冲区溢出检测电路的实时检测结果,当存在缓冲区溢出攻击时,有限状态机fsm跳转至下一状态,反之维持store指令访存

缓冲区的权限;

41.其次,有限状态机fsm跳转至下一状态完成对微处理器所有流水进行暂停处理,以开源riscv处理器pulpino为例,包括取值阶段、译码阶段、执行阶段、回写阶段;

42.然后,有限状态机fsm跳转至下一状态完成对处理器当前函数段所执行的store类型指令访存缓冲区权限的屏蔽。

43.最后,有限状态机fsm跳转至下一状态完成对微处理器所有先前暂停的流水的恢复处理,同时有限状态机fsm跳转至空闲状态。

44.实施例2

45.所述对当前处理器执行指令访存缓冲区权限的屏蔽的方式为:将由处理器回写阶段根据store指令产生的写处理器缓冲区的使能信号强制拉低。

46.实施例3

47.所述本发明提出的机制可分别实现针对缓冲区溢出与返回地址篡改攻击的提前一个时钟周期的预先检测与防御的原因在于:两个缓冲区溢出检测电路均是采集处理器译码与回写阶段的信息给出检测结果的,缓冲区溢出防御电路是在将处理器回写阶段实施的,而缓冲区溢出与返回地址篡改攻击的攻击点是在缓冲区数据重写时刻,该时刻相较于处理器回写阶段滞后一个时钟周期。

48.实施例4

49.本实施例结合附图2,来说明本发明部署的轻易性:

50.如图2所示,本发明的两个缓冲区溢出检测电路是通过连续实时地采集微处理器译码阶段的指令及其有效信号与回写阶段的数据地址挂接在处理器流水线上的;本发明的缓冲区溢出防御电路是通过修改处理器回写阶段根据store指令产生的写处理器缓冲区的使能信号的方式实现挂接在处理器流水线上的。

51.实施例5

52.本实施例结合附图3-6,来说明本发明的有效性:

53.以开源riscv处理器pulpino为实验验证平台,对照地在基线处理器与部署本发明提出的机制的处理器运行如图3所示的缓冲区溢出攻击示例。其运行结果如图4所示:基线处理器在执行完缓冲区示例代码时遭受到了控制流劫持,在处理器中执行函数method11,其函数返回地址被溢出覆盖为函数shellcode的入口地址,从而导致处理器在执行完method11后,处理器控制流被劫持执行shellcode;部署本发明提出的机制的处理器在执行缓冲区示例代码时,由于本发明提出的机制的存在,因此处理器未受到缓冲区溢出攻击的影响,可正确无误地运行。

54.获取本发明提出的机制中的两种缓冲区溢出检测电路在执行缓冲区溢出攻击示例代码时的仿真波形,如图5、6所示。

55.对图5的分析:由信号security_regs_rdata_i可知,自定义扩展指令下传的当前函数段所申请的缓冲区大小为ref_bs=0x14byte,根据信号stack_use_total可知,根据缓冲区边界检查模块实时计算的缓冲区空间实际消耗值由0x递增到0x18,当rt_bs=0x18byte,此时大于ref_bs,即ref_bs-rt_bs=-4《0,根据stack_remain_space=0xffff_fffc可知,当前执行函数段所申请的缓冲区即将发生溢出行为,根据is_buffer_overflow_o=1’b1可知,基于riscv处理器指令的自定义扩展的缓冲区溢出检测电路成功检测到缓冲

区溢出攻击;

56.对图6的分析:由信号limit_addr_reg可知,当前执行函数段所能访存的上限地址为max_a=0x107fdc,根据信号sw_dtcm_addr可知,实时采集回写阶段访存缓冲区的数据地址存在rt_a=0x107fd8与rt_a=0x107fdc的情况,即|max_a-rt_a|=4or 0≤4,因此存在缓冲区溢出攻击,根据信号is_buffer_overflow_2o=1’b1可证实存在缓冲区溢出攻击。

57.实施例6

58.本实施例结合附图7,来说明本发明面积资源消耗较小的优势:

59.将本发明部署在pulpino中的机制通过dc(design compiler)综合获取面积情况,并与pulpino的dc综合面积进行比较,如图7所示。其中dc综合采用的工艺库为台积电130nm,时钟周期为6ns。

60.对图7的分析:本发明在台积电130nm工艺库下的dc综合面积占pulpino面积的9.1%;缓冲区检测电路一的dc综合面积占pulpino面积的0.48%;缓冲区检测电路二占pulpino面积的8.64%;缓冲区防御电路的dc综合面积占pulpino面积的0.01%;其中缓冲区检测电路二由于实时创建的程序控制流动态栈的存在,导致面积消耗较高,但不大于处理器总面积的9%。

61.综上,本发明提出了一种用于微处理器缓冲区溢出的硬件检测与防御机制。通过基于微处理器指令的自定义扩展的缓冲区溢出检测电路,结合微处理器编译器与硬件电路实现针对缓冲区溢出攻击提前一个时钟周期的预先检测,并且可实时对数组越界的溢出行为进行实时检测;通过基于微处理器中程序控制流图实时构建的缓冲区溢出检测电路,使用纯硬件的方式保证该检测机制不会被攻击者绕过,同时针对缓冲区溢出攻击覆盖函数返回地址这一恶意行为可提前一个时钟周期得到预先检测结果;通过缓冲区溢出防御电路,可根据两个缓冲区溢出检测电路的预先检测结果,在缓冲区溢出攻击执行完毕之前,屏蔽当前处理器执行指令访存缓冲区的权限,无效化微处理器遭受到的缓冲区溢出攻击,保证处理器可不受缓冲区溢出攻击影响地正常运行;本发明简单高效,无需占用的太多的硬件资源,只需要对微处理器内核进行微小修改并可轻易部署在微处理器中。

62.本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的权利要求范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1