基于量子门线路模型的超导量子芯片EDA架构

基于量子门线路模型的超导量子芯片eda架构

技术领域

1.本发明涉及超导量子芯片设计领域,具体涉及基于量子门线路模型的超导量子芯片eda架构。

背景技术:

2.实现量子计算的物理平台需要有编码量子比特的物理载体,使不同的量子比特之间可以可控耦合,并对噪声有一定的屏蔽能力。目前研发的主要量子计算机的方案有超导、离子阱、量子点、拓扑和金刚石色心等。超导技术路线的优点是可与现有的微纳加工技术兼容、易于扩展以及量子线路具有可设计性等。因此,超导量子芯片在近年来快速发展。2019年,google报道53位比特处理器“悬铃木”在量子随机线路采样问题中的首次实验,验证了量子计算的优越性。2021年发布路线图,预测2029年实现百万位量子比特和可纠错量子计算。2020年,ibm发布了65比特的“蜂鸟”处理器。2021年,ibm推出了127量子比特“老鹰”处理器。2021年五月,中科大团队在超导量子计算上取得重要进展,发布“祖冲之”62比特处理器,演示了二维量子随机游走算法。从上述超导量子芯片的发展中可以发现,超导量子芯片的比特数目越来越多。超导量子芯片版图的复杂性也会随着比特数目的增加而增大。

3.传统的芯片设计可以采用eda工具进行辅助设计,对于量子芯片,当量子比特规模越来越大,人工布线手动画图将变得越来越复杂。所以使用eda工具辅助设计人员构建物理版图成为重要研究方向;ibm公司在2021年3月份正式推出了开源量子芯片设计自动化工具qiskit metal。这是第一款面向超导设备的自动化设计工具。也是全球首款面向超导量子芯片的自动化设计工具。2021年6月17日,芬兰量子硬件初创公司iqm公布了其开源软件工具kqcircuits,以实现超导量子处理器的自动化设计。kqcircuits是由芬兰阿尔托大学和iqm公司使用klayout设计程序,联合开发的python库。

4.随着量子比特数目的增加,以上两款eda工具将存在如下的问题:对于qiskit-metal,这款工具不能从解决实际问题的算法出发,设计对应实现该算法的专用芯片。此外它是利用现有的芯片组件(量子比特、读取谐振腔、控制线)直接构建版图的布局,并没有向用户展示整个芯片的等效电路。从而在设计上自由度低只能进行模板内固定的算法芯片设计。

5.对于kqcircuits,它可以通过拖拽现有物理组件或者代码编辑方式构建芯片版图,是一种“傻瓜式”的芯片设计方法,它的模拟仿真部分也并不完善。

6.为了应对量子比特数目的增加其电路复杂度增加的问题,以及达成实现不同算法的专用量子芯片电路设计,亟需一种自由度高,能够针对实现不同算法的专用量子芯片设计eda框架。

技术实现要素:

7.本发明为解决上述问题,提供了一种基于量子门线路模型的超导量子芯片eda架

构,针对要实现的算法,设计算法门线路模型,通过分析拆解算法门线路模型得到量子芯片物理拓扑结构,进而通过映射、优化得到等效电路,最终生成gds版图,实现为运行某个特定算法,所设计硬件载体量子芯片的目的,从算法门线路模型到实际物理(gds)版图,完成自动化生成,解决了设计时电路复杂的问题。

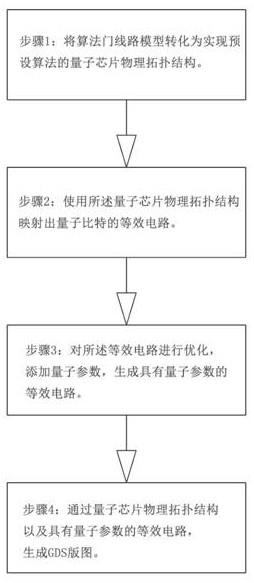

8.为了实现上述目的,本发明提出了一种基于量子门线路模型的超导量子芯片eda架构,包括:步骤1:将算法门线路模型转化为实现预设算法的量子芯片物理拓扑结构;步骤2:使用所述量子芯片物理拓扑结构映射出量子比特的等效电路;步骤3:对所述等效电路进行优化,添加量子参数,生成具有量子参数的等效电路,所述量子参数包括量子比特的工作频率,非谐性、约瑟夫森结常温电阻值;步骤4:通过量子芯片物理拓扑结构以及具有量子参数的等效电路,生成gds版图。

9.本发明提出了从实际算法问题设计专用量子芯片eda工具的架构,量子芯片设计自由度高,采用从算法门线路到芯片物理拓扑结构的映射方法,将算法门线路中包含的算法信息转换为量子芯片物理拓扑结构,从而量子芯片物理拓扑结构包含算法门线路中的算法信息,而后将该量子芯片物理拓扑结构与等效电路进行映射完成量子芯片的电路设计,最终生成实际光刻gds版图,得到与算法相对应的用于实现该算法的量子芯片gds版图,在该框架下大大提高了量子芯片设计的自由度,以及简化了人工参与设计的部分,起到了减少电路设计复杂度的效果。

10.进一步地,所述步骤1具体包括:步骤1.1:使用程序编译方法将算法门线路模型进行分解得到构成算法门线路功能的基础门组;步骤1.2:对所述基础门组进行程序编译处理,解析出量子比特的数量以及量子比特之间的相互作用关系;其中,基础门组中算法线路的数量代表了量子比特的数量,基础门组的门操作代表了量子比特之间存在相互作用关系;步骤1.3:通过量子比特的数量以及量子比特之间的相互作用关系得到量子芯片的物理拓扑结构。

11.将算法门线路模型拆解成构成该算法的基础门组,通过解析每一个基础门组,得到量子比特的数量以及量子比特之间的相互作用关系,用基础门组中算法线路的数量表示量子比特的数量,用基础门组的门操作表示量子比特之间的相互作用关系,从而得到该算法门线路模型下的量子芯片的主要设计参数,该设计参数采用量子芯片的物理拓扑结构表示,实现了算法门线路模型到量子芯片的物理拓扑结构的转换。

12.进一步地,所述步骤2具体包括:步骤2.1:按照量子芯片的物理拓扑结构选择量子比特的电路符号;步骤2.2:通过基本电路符号生成量子比特的等效电路符号;所述基本电路符号包括电容、电感以及约瑟夫森结的电路符号;步骤2.3:所述量子比特连接有读取谐振器,对应的量子比特的电路符号通过电容耦合连接有谐振腔的电路符号;步骤2.4:将两个及两个以上存在相互作用的量子比特通过电容耦合,对应的两个

及两个以上的等效电路符号之间通过电容符号连接,生成与量子芯片的物理拓扑结构对应的量子芯片等效电路。

13.按照量子芯片的物理拓扑结构选择量子比特的电路符号,通过映射以及组合生成量子芯片等效电路。

14.进一步地,步骤1.2所述基础门组的门操作包括哈德玛门运算和相位门运算。

15.通过上述技术方案,本发明的有益效果为:本发明针对实际算法问题,设计了一种针对该算法的专用量子芯片的eda工具架构,用于辅助专用超导量子芯片设计,专用体现在为实现某个特定算法所设计量子芯片,提出从算法门线路到量子芯片物理拓扑结构的映射方法,并通过量子芯片物理拓扑结构构建等效电路,通过量子芯片物理拓扑结构以及具有量子参数的等效电路,生成gds版图,完成量子芯片的设计,具有较高自由度,并具有简化设计难度的效果。

附图说明

16.图1是本发明基于量子门线路模型的超导量子芯片eda架构的步骤流程图;图2是本发明基于量子门线路模型的超导量子芯片eda架构的算法门线路模型示意图;图3是本发明基于量子门线路模型的超导量子芯片eda架构的量子芯片物理拓扑结构示意图;图4是本发明基于量子门线路模型的超导量子芯片eda架构的电路符号示意图。

17.图5是本发明基于量子门线路模型的超导量子芯片eda架构的量子比特的等效电路示意图。

具体实施方式

18.下面结合附图和具体实施方式对本发明作进一步说明:实施例1如图1~图5所示,基于量子门线路模型的超导量子芯片eda架构,包括:步骤1:将算法门线路模型转化为实现预设算法的量子芯片物理拓扑结构;步骤2:使用所述量子芯片物理拓扑结构映射出量子比特的等效电路;步骤3:对所述等效电路进行优化,添加量子参数,生成具有量子参数的等效电路,所述量子参数包括量子比特的工作频率,非谐性、约瑟夫森结常温电阻值;步骤4:通过量子芯片物理拓扑结构以及具有量子参数的等效电路,生成gds版图。

19.作为一种可实施方式,所述步骤1具体包括:步骤1.1:使用程序编译方法将算法门线路模型进行分解得到构成算法门线路功能的基础门组;步骤1.2:对所述基础门组进行程序编译处理,解析出量子比特的数量以及量子比特之间的相互作用关系;其中,基础门组中算法线路的数量代表了量子比特的数量,基础门组的门操作代表了量子比特之间存在相互作用关系;步骤1.3:通过量子比特的数量以及量子比特之间的相互作用关系得到量子芯片

的物理拓扑结构。

20.作为一种可实施方式,所述步骤2具体包括:步骤2.1:按照量子芯片的物理拓扑结构选择量子比特的电路符号;步骤2.2:通过基本电路符号生成量子比特的等效电路符号;所述基本电路符号包括电容、电感以及约瑟夫森结的电路符号;步骤2.3:所述量子比特连接有读取谐振器,对应的量子比特的电路符号通过电容耦合连接有谐振腔的电路符号;步骤2.4:将两个及两个以上存在相互作用的量子比特通过电容耦合,对应的两个及两个以上的等效电路符号之间通过电容符号连接,生成与量子芯片的物理拓扑结构对应的量子芯片等效电路。

21.作为一种可实施方式,步骤1.2所述基础门组的门操作包括哈德玛门运算和相位门运算。

22.结合上述方法对专用量子芯片设计进行说明将算法门线路模型转化为实现预设算法的量子芯片物理拓扑结构,如图2所示,首先图中的直线代表算法线路,其数目表示实现该算法的基础门组所需的量子比特的数量,图中的h表示哈德玛门运算(hadamard gate),p表示相位门运算(phase gate),h和p映射为量子比特之间的相互作用关系,通过量子比特的数量以及量子比特之间的相互作用关系得到量子芯片的物理拓扑结构;通过量子芯片物理拓扑结构映射出量子比特的等效电路,如图3所示,已知量子芯片的物理拓扑结构得到图5所示的量子芯片等效电路;图3到图5的过程如图4所示,按照现有的量子芯片的构成组件通过量子芯片的物理拓扑结构进行等效电路设计,如步骤2.2~2.4,包括电容电路符号(a),电感电路符号(b),约瑟夫森结电路符号(c),自动形成量子比特的等效电路符号(d),将量子比特的等效电路符号与读取谐振器的电路符号(e)相结合,两个及两个以上的等效电路符号之间通过控制线电路符号连接有电容的电路符号,最终结合生产量子芯片等效电路(f),(a~e表示图4中与之对应的电气元件的电路符号,f表示图5中与之对应的电气元件的电路符号);完成量子芯片等效电路后,对所述等效电路进行优化,添加量子参数,生成具有量子参数的等效电路,根据算法设计的要求,得到量子芯片的基本参数,包括量子比特的工作频率,非谐性、约瑟夫森结常温电阻值;最终,通过量子芯片物理拓扑结构以及具有量子参数的等效电路,生成gds版图。

23.以上所述之实施例,只是本发明的较佳实施例而已,并非限制本发明的实施范围,故凡依本发明专利范围所述的构造、特征及原理所做的等效变化或修饰,均应包括于本发明申请专利范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1