集成电路、数据储存的方法及获得错误校正数据的方法与流程

本公开技术是关于存储器集成电路(integrated circuit;ic),且特定言之,是关于减小读取数据的位错误率(bit-error rate;ber)的集成电路、将数据储存于集成电路中的方法以及自存储器中储存于多个位置中的数据获得错误校正数据的方法。

背景技术:

1、存储器芯片的位错误率(ber)随着更先进的技术节点变得更高。现有产品使用先进的错误侦测及校正技术,且尝试在不同读取条件下进行读取以恢复损坏的数据。

2、然而,若存在过多错误位,则无法恢复一些数据。此对于重要数据(诸如对于操作系统)是不可接受的,且可使用数据的额外副本来增强数据完整性。

3、在存储器内计算(computing-in-memory;cim)应用中,在存储器芯片内部执行某些计算操作。在无内部错误校正码(ecc)电路校正数据的情况下,cim应用受高数据错误率妨碍。

技术实现思路

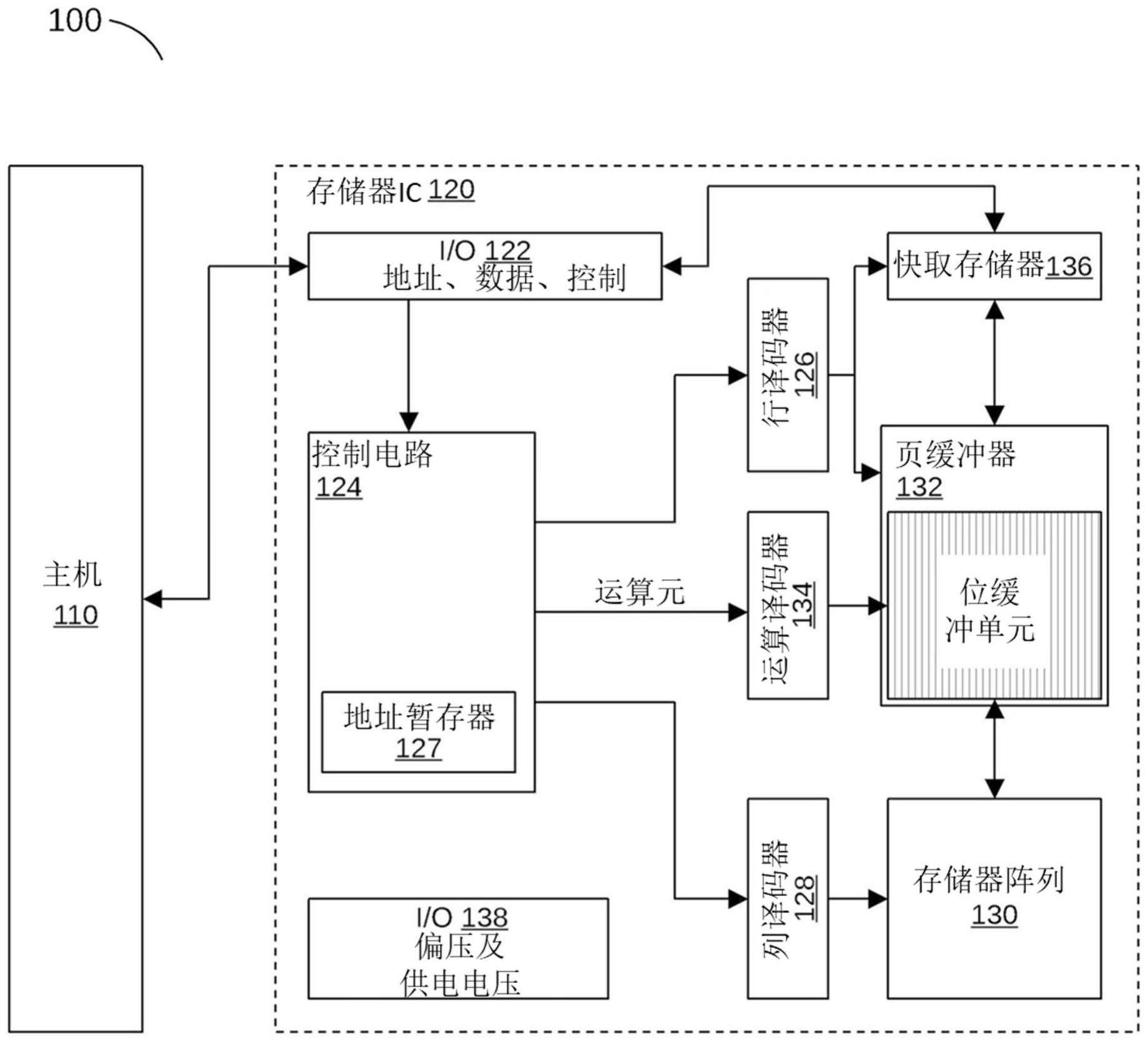

1、在第一实施例中,所公开技术提供集成电路(ic),所述集成电路包括与存储器内计算(cim)逻辑耦接的存储器阵列。存储器具有一或多个存储器单元阵列。cim逻辑对冗余地储存于存储器阵列中的三个或大于三个位执行多数决功能以获得错误校正数据。cim逻辑可包含组合逻辑以执行多数决功能。

2、ic可还包含i/o接口、页缓冲器,所述页缓冲器包含第一位数据缓冲器、第二位数据缓冲器以及第三位数据缓冲器。cim逻辑可包含逻辑电路以对储存于第一位数据缓冲器、第二位数据缓冲器及/或第三位数据缓冲器中的位执行至少部分的多数决功能,其中多个位缓冲单元的第一位数据缓冲器d1联合地形成第一数据缓冲器,多个位缓冲单元的第二位数据缓冲器联合地形成第二数据缓冲器,且多个位缓冲单元的第三位数据缓冲器联合地形成第三数据缓冲器。此外,ic可包含控制电路,所述控制电路与输入/输出接口、存储器阵列以及页缓冲器耦接,且经组态以自输入/输出接口接收控制信号,且响应于冗余读取数据控制信号,自存储器阵列中的三个或大于三个不同位置读取数据,且对自三个或大于三个不同位置读取的数据执行多数决功能以获得错误校正数据,且将错误校正数据复制至输入/输出接口或将错误校正数据用于新的cim逻辑操作。

3、在实施例中,控制电路可经组态以响应于“冗余写入数据”控制信号而将数据自输入/输出接口复制至存储器阵列中的三个或大于三个不同位置中的每一个。

4、在另一实施例中,控制电路可经组态以响应于冗余读取数据控制信号而执行多数决功能以提供错误校正数据。

5、在另一实施例中,ic可包含耦接于页缓冲器与输入/输出接口之间的快取存储器。

6、在实施例中,控制电路可经组态以输出信号以使cim逻辑执行包含以下的操作:自存储器阵列中的第一位置读取数据,且将自第一位置读取的数据储存于第一数据缓冲器中;自存储器阵列中的第二位置读取数据,且将自第二位置读取的数据储存于第二数据缓冲器中;对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位xnor运算,且将由位xnor运算产生的数据储存于第三数据缓冲器中;对储存于第三数据缓冲器中的数据以及储存于第一数据缓冲器中的数据执行第一位and运算,且将由第一位and运算产生的数据储存于第一数据缓冲器中;自存储器阵列中的第三位置读取数据,且将自第三位置读取的数据储存于第二数据缓冲器中;对储存于第二数据缓冲器中的数据以及来自储存于第三数据缓冲器中的数据的反相位执行第二位and运算,且将由第二位and运算产生的数据储存于第二数据缓冲器中;以及对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位or运算,且使用由位or运算产生的数据作为错误校正数据。

7、在另一实施例中,控制电路经组态以输出信号以使cim逻辑执行包含以下的操作:自存储器阵列中的第一位置读取数据,且将自第一位置读取的数据储存于第一数据缓冲器中;自存储器阵列中的第二位置读取数据,且将自第二位置读取的数据储存于第二数据缓冲器中;对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位xnor运算,且将由位xnor运算产生的数据储存于第三数据缓冲器中;自存储器阵列中的第三位置读取数据,且将自第三位置读取的数据储存于第二数据缓冲器中;对储存于第三数据缓冲器中的数据以及储存于第一数据缓冲器中的数据执行第一位and运算,且将由第一位and运算产生的数据储存于第一数据缓冲器中;对储存于第二数据缓冲器中的数据以及来自储存于第三数据缓冲器中的数据的反相位执行第二位and运算,且将由第二位and运算产生的数据储存于第二数据缓冲器中;以及对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位or运算,且使用由位or运算产生的数据作为错误校正数据。

8、在实施例中,提供一种将数据地储存于集成电路(ic)的存储器阵列中的方法。存储器阵列可包含一或多个存储器单元阵列,ic可包含地址暂存器及与存储器阵列耦接的存储器内计算(cim)逻辑。方法可包含:将安全储存的档案的至少一个地址保存在地址暂存器中;由地址暂存器输出安全储存的档案的三个或大于三个地址;以及实施cim逻辑以对安全储存的档案的三个或大于三个位执行多数决功能,以在存储器阵列中将三个或大于三个位冗余地储存于与存储器阵列中的三个或大于三个地址相关联的三个或大于三个不同位置中。

9、在其他实施例中,方法可包含:自存储器阵列中的第一位置读取数据,且将自第一位置读取的数据储存于第一数据缓冲器中;自存储器中的第二位置读取数据,且将自第二位置读取的数据储存于第二数据缓冲器中;对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位xnor运算,且将由位xnor运算产生的数据储存于第三数据缓冲器中;对储存于第三数据缓冲器中的数据以及储存于第一数据缓冲器中的数据执行第一位and运算,且将由第一位and运算产生的数据储存于第一数据缓冲器中;自存储器中的第三位置读取数据,且将自第三位置读取的数据储存于第二数据缓冲器中;对储存于第二数据缓冲器中的数据以及来自储存于第三数据缓冲器中的数据的反相位执行第二位and运算,且将由第二位and运算产生的数据储存于第二数据缓冲器中;以及对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位or运算,且使用由位or运算产生的数据作为错误校正数据。

10、在另一实施例中,方法可包含:自存储器阵列中的第一位置读取数据,且将自第一位置读取的数据储存于第一数据缓冲器中;自存储器中的第二位置读取数据,且将自第二位置读取的数据储存于第二数据缓冲器中;对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位xnor运算,且将由位xnor运算产生的数据储存于第三数据缓冲器中;自存储器阵列中的第三位置读取数据,且将自第三位置读取的数据储存于第二数据缓冲器中;对储存于第三数据缓冲器中的数据以及储存于第一数据缓冲器中的数据执行第一位and运算,且将由第一位and运算产生的数据储存于第一数据缓冲器中;对储存于第二数据缓冲器中的数据以及来自储存于第三数据缓冲器中的数据的反相位执行第二位and运算,且将由第二位and运算产生的数据储存于第二数据缓冲器中;以及对储存于第一数据缓冲器中的数据以及储存于第二数据缓冲器中的数据执行位or运算,且使用由位or运算产生的数据作为错误校正数据。

11、在审阅以下附图、详细描述以及权利要求范围时可见所公开技术的其他实施例及优势。

- 还没有人留言评论。精彩留言会获得点赞!