一种基于范围可寻址查找表计算tanh函数的数字电路模块的制作方法

1.本发明涉及神经网络和数字电路设计领域,尤其是涉及非线性激活函数的电路实现,具体涉及一种基于范围可寻址查找表计算tanh函数的数字电路模块。

背景技术:

2.如今,人工神经网络已经被应用在许多领域,如图像和语音识别、自然语言处理等。在人工神经网络种,激活函数被用于每个神经元,用来给神经网络引入非线性,从而提高神经网络对模型的表达能力。神经网络在计算时,首先会将输入的数据进行卷积等线性运算,再将结果作为激活函数的输入量。如今新兴的网络演变趋向于使用较少的线性计算操作,并且对于线性计算进行了很多的优化,结果神经网络的性能瓶颈逐渐转移到复杂的激活函数上来。

3.目前主流的人工神经网络中,tanh函数是常见的非线性激活函数,由于其需要复杂的指数运算和除法运算,用软件去计算将会消耗很多的时间,限制神经网络的性能,因此我们希望去设计专用的硬件模块来计算非线性激活函数。

4.关于非线性激活函数的近似方法主要有查找表、分段线性近似、分段非线性近似、混合方法等。其中查找表方法思路简单,计算速度快,是比较常采用的方法。但是查找表方法需要很多的存储单元去存储函数值,随着精度的提高,存储单元的数量会急剧上升。

技术实现要素:

5.为了缓解查找表方法对于存储单元需求量大的不足,充分利用tanh函数自身的特点(包括tanh接近零点处函数值接近自变量x,无穷远处函数值趋向于1和-1,以及tanh本身是奇函数),对一定的精度要求选择最合适的数据位宽和查找表的存储内容,本发明采用如下的技术方案:

6.本发明提供了一种基于范围可寻址查找表计算tanh函数的数字电路模块,包括:输入模块、地址映射模块、暂存寄存器模块、存储器模块、选择输出模块、控制逻辑单元;

7.所述输入模块,接受外部的输入数据data作为tanh函数的自变量,并将输入数据data分解为符号位sign和无符号数unsigned,作为输入模块的输出;输入数据的格式规定如下:采用n位定点数的格式,其数据格式是{s,i,f},其中s为1位符号位,表示数据的正负,i为n0位整数位,f为n1小数位,n=1+n0+n1;数据的输入范围为(-2

n0

,2

n0

),n为数据位宽,n0为整数位宽,n1为小数位宽;

8.所述地址映射模块,接受输入模块给出的无符号数unsigned,以及外部输入的overflow位,处理产生对应函数值在存储器模块中的地址addr2,并生成读使能信号ren;其中外部输入的overflow位表示输入数据的范围,若overflow=1,表示输入不在(-2

n0

,2

n0

)之间;

9.所述暂存寄存器模块,接受输入模块输出的无符号数unsigned并存储起来;

10.所述存储器模块,有读出和写入两种模式;当外部给出的写使能信号wen为1时,存

储器模块将外部的输入数据data作为数据存储起来,存储地址为外部输入的地址addr1;当地址映射模块生成的读使能信号ren为1时,存储器模块将地址addr2处所存储的数据作为输出;存储器模块的存储单元的数据格式是无符号定点数,并且只有小数位,位宽为n2-1;其中1表示符号位,符号位不需要存储;

11.所述选择输出模块,根据控制逻辑单元给出的控制信号、选择暂存寄存器模块或存储器模块的输出数据的其中一个,经过去除整数位、末尾补零的操作以及添加符号位sign的操作后,作为输出output;所述选择输出模块的选择逻辑为,当输入数据data的无符号数unsigned小于预先给定的分界值x_start,且overflow位为0时,直接将unsigned经过去除整数位、末尾补零和添加符号位sign的操作后,作为输出output,其中小数部分末尾补零直到整个数据位宽与输出output规定的位宽n2相等;否则,输入数据的函数值会在存储器模块中查找,再经过添加符号位sign的操作后,作为输出output;输出数据output为有符号定点数,位宽为n2,数据格式为{s,f},其中s为1位符号位,f为定点数的小数位,没有整数位;预先给定的分界值x_start的格式为{i,f},位宽为n-1,不包含符号位;

12.所述控制逻辑单元,协调各模块的执行,在其控制下整个计算过程在3个时钟周期内被完成,并输出计算完成信号fin;当外部输入的复位信号rst为1时,整个数字电路模块被复位;第1个时钟周期内,输入数据经过输入模块和地址映射模块,得到ren信号和地址addr,以及需要被暂存的数据unsigned;第2个时钟周期内,暂存寄存器模块和存储器模块的输出值将会根据控制逻辑单元给出的信号被选择;第3个时钟周期内,被选择的数据经过输出寄存器被输出,同时计算完成信号fin变为1,表示计算已经完成。

13.根据本发明的优选方案,所述输入数据data的数据位宽n,整数位宽n0和小数位宽n1,输出数据output的数据位宽n2,选择输出模块的分界值x_start由以下方法确定:

14.首先确定计算tanh函数的最大绝对值误差e;

15.然后确定n2,选取的n2满足1/2

n2

≤e/10;

16.接着确定n1,要满足1/2

n1

≤e且1/2

n1

≤2(e-1/2

n2

);

17.接着确定n0,要满足1-tanh(2

n0

)≤2(e-1/2

n2

),n0选择满足条件的最小值;

18.接着确定n,要满足n=1+n0+n1;

19.最后确定x_start,其为方程x-tanh(x)=e的解。

20.根据本发明的优选方案,选择输出模块的分界值x_start取其定点数格式下能表示的最接近方程x-tanh(x)=e的解的值。

21.根据本发明的优选方案,地址映射模块的映射法则由以下方法确定:

22.把区间[x_start,2

n0

)分成n个分区,各个分区首尾连接、互不重叠地覆盖整个区间。已经确定x_start后,x_start为第1个分区的开始点,也记为x0,第1个分区的截止点为x1,也为第2个分区的开始点,以此类推,用变量k表示一个分区的标号,k取1、2、3、

……

、n;x0和后面第k个分区的截止点xk为n-1位的无符号定点数,小数位宽为n1,整数位宽为n0,选取xk为最大的该格式下能满足tanh(xk)-tanh(xk-1)≤2(e-1/2

n2

)的数,即从x0开始,将x0从最小一位加1得到该格式下能表示的x0的下一位数x,然后检验该数x是否满足tanh(xk)-tanh(xk-1)≤2(e-1/2

n2

),直到不满足为止,把最后一个满足上述不等式的数x作为x1,其余的xk也按照此规则确定;按照这种规则直到确定到第k个分区,使得xk≥2

n0

,这时已经把区间[x_start,2

n0

)范围内全部分区,最后一个分区的截止点xk取2

n0

,分区总数n=k。

[0023]

根据本发明的优选方案,地址映射模块的映射法则为:当overflow=0时,若输入的无符号数处于第k个分区,就输出二进制形式的k-1作为地址addr2;当overflow=1时,就输出二进制形式的n作为地址addr2。

[0024]

根据本发明的优选方案,所述存储器模块的存储数据值为:在地址k-1处,存储能用存储数据格式表示的最接近(tanh(xk)-tanh(xk-1))/2的数,其中存储数据格式就是小数位宽为n2-1、没有整数位的无符号定点数;在地址n处,存储能用该数据格式表示的最接近(1-tanh(2

n0

))/2的数。

[0025]

根据本发明的优选方案,该模块在执行计算操作之前,需要先按照上述的存储数据值在存储器模块中存放相应的数据。

[0026]

根据本发明的优选方案,地址addr是由控制逻辑单元从地址addr1和地址addr2两个信号中选择出来的,选择上述两个数据的逻辑为:当外部给出的写使能信号wen为1时,选择地址addr1作为地址addr;当写使能信号wen为0时,选择地址addr2作为地址addr。

[0027]

本发明的优势在于提出了利用范围可寻址查找表计算tanh函数的具体电路模块设计方法,在设计给定的最大绝对值误差e内,将多个输入数据映射到同一个存储单元,减少了存储单元的使用,同时提出了一种优化的分区方法,能够选择较优的数据映射方案,进一步的减少存储单元的使用;此外还提出了输入数据和输出数据的位宽选择方法,能尽可能的减少单个存储单元的长度,从而减少存储器的使用面积;并且还利用了tanh函数的性质,将小于x_start的输入直接作为输出,负数的输入转化为正数后再进行计算,也减少了存储器的面积。本发明相对于普通查找表方法,减少了存储器资源的使用,并且结构简单,没有类似乘法器的复杂单元,计算速度快,功耗低,占用面积小,可拓展,能够符合目前神经网络边缘计算的应用场景。

附图说明

[0028]

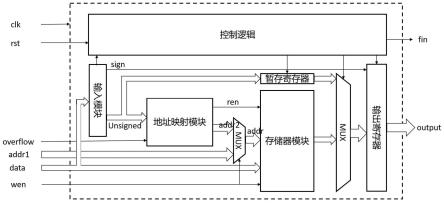

图1是本发明模块的结构框图。

[0029]

图2是本发明模块的输入数据格式图。

[0030]

图3是本发明模块的电路时序图。

[0031]

图4是本发明模块的功能仿真波形图。

具体实施方式

[0032]

下面结合附图和具体实施方式对本发明作进一步详细的说明。

[0033]

本实施例计算tanh的最大绝对值误差e=0.02,采用如下技术方案:

[0034]

一种基于范围可寻址查找表计算tanh函数的数字电路模块,包括:输入模块、地址映射模块、存储器模块、暂存寄存器模块、选择输出模块、控制逻辑单元;其结构框图如图1所示。

[0035]

所述输入模块,接受外部的输入data作为tanh函数的自变量,并将输入数据分解为符号位sign和无符号数unsigned,作为模块的输出。输入数据采用8位定点数的格式,包括1位符号位,1位整数和6位小数。数据的输入范围为(-2,2),数据格式如图2所示。

[0036]

所述地址映射模块,接受输入模块给出的无符号数unsigned,以及外部神经网络的输入overflow位,处理产生对应函数值在存储器模块中的地址addr2,并生成读使能信号

ren,addr2位宽为5。其中外部神经网络的输入overflow位表示输入数据的范围,若overflow=1,表示输入不在(-2,2)之间。

[0037]

所述暂存寄存器模块,接受输入模块输出的无符号数unsigned并存储起来。

[0038]

所述存储器模块,有读出和写入两种模式。当外部给出的写使能信号wen为1时,存储器模块将外部的输入data作为数据存储起来,存储地址为外部输入的数据addr1;当地址映射模块生成的读使能信号ren为1时,存储器模块将地址addr2处所存储的数据作为输出。存储器模块的存储单元的数据格式是无符号定点数,并且只有小数位,位宽为8。

[0039]

所述选择输出模块,包含mux和输出寄存器两个部分,其会根据控制逻辑给出的控制信号,选择暂存寄存器或存储器模块的输出数据的其中一个,经过添加符号位sign的操作后,作为输出output,其中暂存寄存器存储输入数据的无符号部分unsigned,output为9位有符号定点数,包括1位符号位和8位小数位,没有整数位。上述选择输出模块的选择逻辑为,当输入的数据data的无符号数unsigned小于预先给定的数据x_start=0.40625(转化为定点数格式即为7’h1a),且overflow=0时,说明数据足够小,直接将unsigned经过去除整数位,并在小数位末尾添加两位0以及在最高位添加符号位sign的操作后,作为输出output;否则,输入数据的函数值会在存储器模块中查找,再经过补充数据位和添加符号位sign的操作后,作为输出output。

[0040]

所述控制逻辑单元,协调各模块的执行,在其控制下整个计算过程在3个时钟周期内被完成,如图3所示,并输出计算完成信号fin。当外部输入的复位信号rst为1时,整个数字电路模块被复位;第1个时钟周期内,输入数据经过输入模块和地址映射模块,得到ren信号和地址addr,以及被需要被暂存的数据unsigned,地址addr是由控制逻辑单元从地址addr1和地址addr2两个信号中选择出来的,选择上述两个数据的逻辑为:当外部给出的写使能信号wen为1时,选择地址addr1作为地址addr;当写使能信号wen为0时,选择地址addr2作为地址addr;第2个时钟周期内,暂存寄存器模块和存储器模块的输出值将会根据控制逻辑给出的信号被选择;第3个时钟周期内,被选择的数据经过输出寄存器被输出,同时计算完成信号fin变为1,表示计算已经完成。

[0041]

当输入在以下区间范围内时,上述地址映射模块的具体映射法则和对应地址下存储器模块的存储数据如下所述,其中地址和存储器模块的存储值还写出了二进制格式的数据:

[0042]

区间[0.40625,0.4375),输出addr2=5’b00000,存储器模块存储0.3984375(8’h66);

[0043]

区间[0.4375,0.46875),输出addr2=5’b00001,存储器模块存储0.42578125(8’h6d);

[0044]

区间[0.46875,0.5),输出addr2=5’b00010,存储器模块存储0.44921875(8’h73);

[0045]

区间[0.5,0.546875),输出addr2=5’b00011,存储器模块存储0.48046875(8’h7b);

[0046]

区间[0.546875,0.59375),输出addr2=5’b00100,存储器模块存储0.515625(8’h84);

[0047]

区间[0.59375,0.640625),输出addr2=5’b00101,存储器模块存储0.55078125

(8’h8d);

[0048]

区间[0.640625,0.6875),输出addr2=5’b00110,存储器模块存储0.58203125(8’h95);

[0049]

区间[0.6875,0.734375),输出addr2=5’b00111,存储器模块存储0.609375(8’h9c);

[0050]

区间[0.734375,0.78125),输出addr2=5’b01000,存储器模块存储0.640625(8’ha4);

[0051]

区间[0.78125,0.84375),输出addr2=5’b01001,存储器模块存储0.671875(8’hac);

[0052]

区间[0.84375,0.90625),输出addr2=5’b01010,存储器模块存储0.703125(8’hb4);

[0053]

区间[0.90625,0.984375),输出addr2=5’b01011,存储器模块存储0.73828125(8’hbd);

[0054]

区间[0.984375,1.0625),输出addr2=5’b01100,存储器模块存储0.76953125(8’hc5);

[0055]

区间[1.0625,1.15625),输出addr2=5’b01101,存储器模块存储0.8046875(8’hce);

[0056]

区间[1.15625,1.265625),输出addr2=5’b01110,存储器模块存储0.8359375(8’hd6);

[0057]

区间[1.265625,1.40625),输出addr2=5’b01111,存储器模块存储0.87109375(8’hdf);

[0058]

区间[1.40625,1.59375),输出addr2=5’b10000,存储器模块存储0.90234375(8’he7);

[0059]

区间[1.59375,1.90625),输出addr2=5’b10001,存储器模块存储0.9375(8’hf0);

[0060]

区间[1.90625,2.0),输出addr2=5’b10010,存储器模块存储0.9609375(8’hf6);

[0061]

当overflow为1时,输出addr2=5’b10011,存储器模块存储0.98046875(8’hfb)。

[0062]

本发明在进行计算之前,需要通过相应接口将上述数值存储到相应存储单元内部。

[0063]

以上实施例在vivado上实现了设计,并通过了功能仿真和实际的fpga上板验证,测试发现,电路的实际功能与预期相符,输出与理论值吻合。在此实施例中e=0.02,一共使用了20个存储单元,每个单元的数据位宽为8位,而使用普通查找表方法,需要使用64个存储单元,每个单元数据位宽为8位,本实施例存储器使用量相比普通查找表方法减少了68.8%;而在e=0.002的另一个测试结果中,一共使用了296个存储单元,每个单元的数据位宽为11位,而普通查找表方法需要使用512个存储单元,每个单元数据位宽为11位,存储器使用量相比普通查找表方法减少了42.2%。图4为此实施例的功能仿真波形,从图中可以看到计算三个时钟周期内完成。

[0064]

以上实施例仅用以说明本发明的技术方案,而非对其限制,本发明的保护范围并不限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变

化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1