一种PHY数据传输系统的制作方法

一种phy数据传输系统

技术领域

1.本发明涉及一种数据传输技术领域,具体为一种phy数据传输系统。

背景技术:

2.phy中文可称之为端口物理层,是一个对osi模型物理层的共同简称,phy数据传输最关键的两个因素是传输速度和传输的安全性,例如,参考图1,申请号201610710456.6,发明名称为一种基于m-phy接口实现的数据传输加密装置的发明专利,通过主控制器、flash模块、加解密算法模块和usb-key模块组成加解密模块,且pc主机将要写入的数据经过加解密模块实现加密后写入ufs主控端ufshost连接的ufs设备;加解密模块实现将ufs设备上的加密数据进行解密后传输给pc主机,能够提高m-phy数据传输的安全性;

3.目前phy数据传输在传输速度上还存在着一定缺陷,现有的phy数据传输接口通过arm传输到上位机的传输速率只能达到400mbps,这样的传输速率已经不能满足现阶段人们的需求,基于现状,急需对现有技术进行改革。

技术实现要素:

4.本发明的目的在于提供一种phy数据传输系统,以解决上述背景技术中提出的问题。

5.一方面,本发明提供如下技术方案一种phy数据传输装置,包括:数据接收转发模块、协议处理模块、仲裁控制器、arm(处理器)和上位机;

6.所述数据接收转发模块具有一耦接外部设备硬件接口的phy数据接收器,且所述数据接收转发模块还具有一ddr数据发送器,所述phy数据接收器用于接收外部设备发送的数据,且phy数据接收器接收的数据通过ddr数据发送器发送到协议处理模块中的ddr接收器中;

7.所述数据接收转发模块与协议处理模块采用并口通信方式,所述数据接收转发模块输出端包括:用于接收信号的ready信号线、用于判断信号是否有效的valid信号线、用于发送数据的data信号线和用于控制上升沿和下降沿的clk时钟信号线;所述ready信号线为高电平有效,当所述ready信号线为高电平时,协议处理模块的ddr接收器准备好接收数据,且只有在ready信号线为高电平的前提下,所述valid信号线为高电平时,ddr数据发送器发送到ddr接收器的数据才有效。

8.所述协议处理模块包括:ddr接收器、ram(存储器)、fifo(先进先出阵列)和dma(内存访问模块);

9.所述ddr仲裁控制器与协议处理模块中的dma采用axi协议通信,ddr仲裁控制器与ram采用spi协议通信;

10.在协议处理模块中,所述ddr接收器与fifo通过信号线fifo_we连接,且所述ddr接收器与ram之间通过信号线ram_we连接;所述fifo采用8bits输入32bits输出,且所述fifo与dma之间采用axis协议通信;

11.所述fifo与ram通过信号线fifo_we和信号线ram_we同步接收ddr数据接收器传输的数据,但是,fifo与ram的传输数据不同之处在于:fifo接收数据后不断的累加并写入到dma中,而ram接收数据后以设定的字节数为周期进行更新;

12.所述dma和ram均通过spi协议与arm通信,且dma中具有dma长度寄存器:dma_length_reg、dma_length_reg_d1和dma_length_reg_d2;且ram中具有ram长度寄存器ram_length_reg;

13.arm定时通过spi协议一方面查询dma的长度寄存器,将设定的字节数的整数倍的数据通过dma传输到arm的内存中;arm定时通过spi协议另一方面查询ram的长度寄存器,将不足设定的字节数的数据通过ram传输到arm的内存中。

14.另一方面,本发明还提供如下技术方案一种phy数据传输方法,具体步骤包括:

15.步骤s1:数据接收转发模块将接收的外部数据通过采用并口通信方式传输到协议处理模块的ddr接收器;

16.步骤s2:ddr接收器分别通过信号线fifo_we和信号线ram_we将数据同步传输到fifo和ram中,且所述fifo接收数据后不断的累加,且ram接收数据后以设定的字节数为周期进行更新,且ram存储的字节数达到设定的字节数时,更新为0字节;

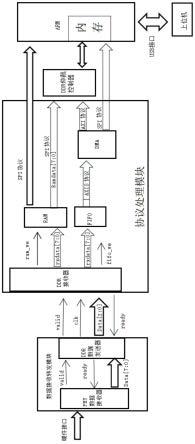

17.步骤s3:arm定时通过spi协议查询dma的长度寄存器,将步骤s2中所述设定的字节数的整数倍的数据,通过dma传输到arm的内存中;

18.步骤s4:arm定时通过spi协议查询ram的长度寄存器,将小于步骤s2中所述设定的字节数的数据,通过ram传输到arm的内存中。

附图说明

19.图1为现有技术一种基于m-phy接口实现的数据传输加密装置的结构示意图;

20.图2为本发明phy数据传输方法示意图;

21.图3为本发明phy数据传输装置结构示意图。

具体实施方式

22.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

23.参考图3,一方面,本发明提供如下技术方案一种phy数据传输装置,包括:数据接收转发模块、协议处理模块、仲裁控制器、arm(处理器)和上位机;

24.在实施例中,数据接收转发模块具有一耦接外部设备硬件接口的phy数据接收器,且数据接收转发模块还具有一ddr(双倍数据速率)数据发送器,phy数据接收器用于接收外部设备发送的数据,且phy数据接收器接收的数据通过ddr数据发送器发送到协议处理模块中的ddr接收器中;

25.在实施例中,数据接收转发模块与协议处理模块采用并口通信方式,数据接收转发模块输出端包括:用于接收信号的ready信号线、用于判断信号是否有效的valid信号线、用于发送数据的data信号线和用于控制上升沿和下降沿的clk时钟信号线;所述ready信号

线为高电平有效,当所述ready信号线为高电平时,协议处理模块的ddr接收器准备好接收数据,且只有在ready信号线为高电平的前提下,所述valid信号线为高电平时,ddr数据发送器发送到ddr接收器的数据才有效,相应的,在ready信号线为低电平时,无论valid信号线为高电平或者低电平,ddr数据发送器发送到ddr接收器的数据均无效;clk时钟信号线在上升沿和下降沿都有效,由于phy数据接收器发送8个字节给ddr数据发送器,data信号线在上升沿和下降沿时分别发送4个字节到ddr接收器,有效的节省了数据接收转发模块与协议处理模块之间的总线数量。

26.所述协议处理模块包括:ddr接收器、ram(存储器)、fifo(先进先出阵列)和dma(内存访问模块);

27.在实施例中,协议处理模块用于通过ddr接收器接收到数据接收转发模块发送的数据后,为了避免不断的传输到arm内存中,一直占用arm内存,导致arm无法进行其他正常工作的情况,所以协议处理模块在向arm内存传输数据之前,先通过ddr仲裁控制器对arm内存申请访问,当arm内存空闲时,再进行协议处理模块的数据传输,其中,所述ddr仲裁控制器与协议处理模块中的dma采用axi协议通信,ddr仲裁控制器与ram采用spi协议通信;

28.在实施例中,在协议处理模块的数据传输过程中,又为了避免一直不断的传输数据,会导致arm的内存不断的工作,占用arm内存时间过长的情况,协议处理模块一方面采用64字节的整数倍的数据通过dma传输到arm的内存中,另一方面将不足64字节的整数倍的数据通过ram传输到arm的内存中;

29.在实施例中,在协议处理模块中,所述ddr接收器与fifo通过信号线fifo_we连接,且所述ddr接收器与ram之间通过信号线ram_we连接;所述fifo采用8bits输入32bits输出,且所述fifo与dma之间采用axis协议通信;

30.在实施例中,所述fifo与ram通过信号线fifo_we和信号线ram_we同步接收ddr数据接收器传输的数据,但是,fifo与ram的传输数据不同之处在于:fifo接收数据后不断的累加并写入到dma中,而ram接收数据后以设定的字节数(本实施例以64字节为例)为周期进行更新;

31.在实施例中,所述dma和ram均通过spi协议与arm通信,且dma中具有dma长度寄存器:dma_length_reg、dma_length_reg_d1和dma_length_reg_d2;且ram中具有ram长度寄存器ram_length_reg;

32.在实施例中,arm定时通过spi协议一方面查询dma的长度寄存器,将设定的字节数(本实施例以64字节为例)的整数倍的数据通过dma传输到arm的内存中;arm定时通过spi协议另一方面查询ram的长度寄存器,将不足设定的字节数(本实施例以64字节为例,即0-63字节)的数据通过ram传输到arm的内存中;

33.在本实施例中,例如在一定时间内,ddr数据接收器同步向fifo和ram都传输了68字节的数据,fifo中存储了68个字节并写入到dma中,且arm定时通过spi协议查询dma的长度寄存器,将64个字节数据传输到arm内存中,而ram中只存储了4个字节,arm定时通过spi协议查询ram的长度寄存器,并在一定时间t3内将该4个字节的数据传输到arm内存中。

34.在实施例中,本发明clk时钟信号线的时钟频率为100m,由于clk时钟信号线包括上升沿触发和下降沿触发,且由图3可知数据接收转发模块与协议处理模块的数据位宽为4,所以本发明的传输速率可以达到100

×2×

4=800mbps,传输速率是目前通过arm传输到

上位机的传输速率的2倍,大大提高了传输效率。

35.参考图2,另一方面,本发明还提供如下技术方案一种phy数据传输方法,基于前述phy数据传输装置为硬件基础对phy数据进行传输;具体步骤包括:

36.步骤s1:数据接收转发模块将接收的外部数据通过采用并口通信方式传输到协议处理模块的ddr接收器;在ready信号线为高电平的前提下,协议处理模块的ddr接收器准备好接收数据,valid信号线为高电平时,ddr数据发送器有效的将数据发送到ddr接收器;

37.步骤s2:ddr接收器分别通过信号线fifo_we和信号线ram_we将数据同步传输到fifo和ram中;fifo接收数据后不断的累加,而ram接收数据后以设定的字节数为周期进行更新,在本实施例中,设定的字节数为64字节,当ram存储的字节数达到64字节时,会更新为0字节;

38.步骤s3:arm定时通过spi协议查询dma的长度寄存器,将步骤s2中所述设定的字节数的整数倍的数据,通过dma传输到arm的内存中;其中,在本实施例中,所述设定的字节为64字节。

39.步骤s301:当fifo不为空时,dma通过读取fifo中的数据往dma写入4字节数据,dma每写入4字节数据,dma的长度寄存器dma_length_reg累加4,且每一段时间t1(本实施例t1采用100ms)锁存一下该数值,并赋值给dma的长度寄存器dma_length_reg_d1,记录此100ms共写入的dma数据量;其中,且长度寄存器dma_length_reg_d1中的字节数小于等于长度寄存器dma_length_reg中的字节数。

40.在实施例中,由于存在长度寄存器dma_length_reg_d1中的字节数在100ms时刚好是64字节的情况,若此时arm通过spi协议查询dma的长度寄存器dma_length_reg_d1而获取dma的传输数据时,会导致长度寄存器dma_length_reg_d1与ram抢占传输到arm内存的情况发生,因此,通过步骤s302进行解决;

41.步骤s302:在100ms的基础上再延时一段时间t2(本实施例t2采用50ms),并将数据锁存到dma的长度寄存器dma_length_reg_d2中;其中,dma_length_reg_d2中的字节数小于等于dma_length_reg_d1中的字节数;这样,当长度寄存器dma_length_reg_d1中的数据就会延时50ms将64字节的整数倍的数据锁存到长度寄存器dma_length_reg_d2中,从而arm定时通过spi协议查询dma的长度寄存器dma_length_reg_d2,获取dma的传输数据,其中,arm通过spi查询的长度寄存器dma_length_reg_d2的值为64的倍数;

42.本发明提供另一可选实施例,用于阐述说明上述arm获取dma的数据的具体过程:例如,0-99ms之间,fifo向dma的长度寄存器dma_length_reg写入的数据为60个字节,此时,长度寄存器dma_length_reg_d1还没有到100ms锁存,所以,dma长度寄存器dma_length_reg_d1和dma长度寄存器dma_length_reg_d2中数据的字节数都为0;arm定时通过spi协议查询dma的长度寄存器dma_length_reg_d2获取dma的传输数据为0字节;

43.在实施例中,当100ms时,fifo向dma的长度寄存器dma_length_reg写入的数据为64个字节,此时,将该64字节数据锁存到dma长度寄存器dma_length_reg_d1中,长度寄存器dma_length_reg_d2中的数据字节数还是0;arm定时通过spi协议查询dma的长度寄存器dma_length_reg_d2获取dma的传输数据还是为0字节;

44.在实施例中,当150ms时,fifo向dma的长度寄存器dma_length_reg写入的字节数为68字节,此时,将64字节数据锁存到长度寄存器dma_length_reg_d1中,且将64字节数据

锁存到长度寄存器dma_length_reg_d2中,arm定时通过spi协议查询dma的长度寄存器dma_length_reg_d2获取dma的传输数据为64字节。

45.步骤s4:arm定时通过spi协议查询ram的长度寄存器,将小于步骤s2中所述设定的字节数的数据,通过ram传输到arm的内存中;

46.步骤s401:ram通过信号线ram_we接收数据后,ram读写地址累加,将数据保存至ram的长度寄存器ram_length_reg中;ram中的数据上传到arm内存有两种方式分别为步骤4021和步骤4022:

47.步骤4021:将dma传输数据的时间与ram传输数据的时间设置为同步,且ram使用2个ram(ram1和ram2),深度分别为64bytes,采取乒乓存储方式,以150ms为一个周期,arm定时150ms通过spi协议查询ram1的长度寄存器ram1_length_reg和ram2的长度寄存器ram2_length_reg;例如,当第一个150ms时,不足64字节的数据锁存到ram1的长度寄存器ram1_length_reg中,arm在150ms时通过spi协议查询ram1的长度寄存器ram1_length_reg,获取ram1的长度寄存器ram_length_reg的数据;当第二个150ms时,不足64字节的数据锁存到ram2的长度寄存器ram2_length_reg中,arm在300ms时,通过spi协议查询ram2的长度寄存器ram2_length_reg,获取ram2的长度寄存器ram_length_reg的数据。

48.本发明提供了一可选实施例,在实施例中,当0-150ms时,ddr接收器总计传输了132个字节的数据,其中,arm通过spi协议查询dma的长度寄存器dma_length_reg_d2获取dma的传输数据为128个字节,且arm通过spi协议查询ram1的ram_length_reg获取ram1中4个字节的数据,从而arm在150ms内获取了128+4=132个字节的数据;若当到300ms时,ddr接收器总计写入了136个字节的数据,arm通过spi协议查询ram2的ram_length_reg获取ram2中151-300ms之间发送的4个字节的数据,从而arm在300ms内获取了132+4=136个字节的数据。

49.步骤4022:dma传输数据的时间与ram传输数据的时间不同步,arm通过spi协议不断的查询ram_length_reg中的数据,当ram中超过一定的时间t3(本实施例t3采用200ms)没有新数据写入,则将ram写地址锁存至ram的长度寄存器ram_length_reg中,此长度寄存器ram_length_reg内的数据值范围必然是0~63字节之间,arm再通过spi协议查询ram_length_reg,若为非0值,则通过spi通信的方式将ram数据读出上传至上位机。

50.尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1