图像处理方法及装置、电子设备、存储介质与流程

1.本技术涉及通信技术领域,具体涉及一种图像处理方法及装置、电子设备、存储介质。

背景技术:

2.随着电子设备拍摄技术的不断发展,如今摄像头在拍摄到原始图像之后,电子设备中的图像处理器可以对原始图像进行优化处理,以提高图像的画面质量;进一步地,图像处理器还可以将优化后的图像数据发送给应用处理器进行进一步地优化,以进一步提高图像的画面质量。

3.在实践中发现,随着图像优化技术的发展,图像处理器发送给应用处理器的图像数据的数据量越来越多,从而导致用于图像数据传输的功耗越来越大。

技术实现要素:

4.本技术实施例公开了一种图像处理方法及装置、电子设备、存储介质,能够降低图像数据传输过程的功耗。

5.本技术实施例第一方面公开一种图像处理方法,应用于第一处理器,所述方法包括:

6.获取第一图像数据,并对所述第一图像数据进行处理,得到处理后的第二图像数据和深度数据,所述深度数据用于描述所述第一图像数据对应的第一图像的景深信息;

7.通过同一个传输接口将所述第二图像数据和所述深度数据发送给第二处理器。

8.本技术实施例第二方面公开一种图像处理方法,应用于第二处理器,所述方法包括:

9.接收第一处理器通过同一个传输接口发送的第二图像数据和深度数据,所述第二图像数据和深度数据是所述第一处理器对获取的第一图像数据进行处理后得到的,所述深度数据用于描述所述第一图像数据对应的第一图像的景深信息;

10.根据所述第二图像数据和所述深度数据生成第三图像。

11.本技术实施例的第三方面公开一种图像处理装置,应用于第一处理器,所述装置包括:

12.处理单元,用于获取第一图像数据,并对所述第一图像数据进行处理,得到处理后的第二图像数据和深度数据,所述深度数据用于描述所述第一图像数据对应的第一图像的景深信息;

13.发送单元,用于通过同一个传输接口将所述第二图像数据和所述深度数据发送给第二处理器。

14.本技术实施例的第四方面公开一种图像处理装置,应用于第二处理器,所述装置包括:

15.接收单元,用于接收第一处理器通过同一个传输接口发送的第二图像数据和深度

数据,所述第二图像数据和深度数据是所述第一处理器对获取的第一图像数据进行处理后得到的,所述深度数据用于描述所述第一图像数据对应的第一图像的景深信息;

16.生成单元,用于根据所述第二图像数据和所述深度数据生成第三图像。

17.本技术实施例第五方面公开一种电子设备,包括:

18.存储有可执行程序代码的存储器;

19.与所述存储器耦合的处理器;

20.所述处理器调用所述存储器中存储的所述可执行程序代码,执行本技术实施例第一方面或第二方面公开的图像处理方法。

21.本技术实施例第六方面公开一种计算机可读存储介质,其存储计算机程序,其中,所述计算机程序使得计算机执行本技术实施例第一方面或第二方面公开的图像处理方法。

22.本技术实施例第七方面公开一种计算机程序产品,当所述计算机程序产品在计算机上运行时,使得所述计算机执行本技术实施例第一方面或第二方面的任意一种方法的部分或全部步骤。

23.本技术实施例第八方面公开一种应用发布平台,所述应用发布平台用于发布计算机程序产品,其中,当所述计算机程序产品在计算机上运行时,使得所述计算机执行本技术实施例第一方面或第二方面的任意一种方法的部分或全部步骤。

24.与相关技术相比,本技术实施例具有以下有益效果:

25.本技术实施例中,第一处理器可以获取第一图像数据,并对第一图像数据进行处理,以分别得到处理后的第二图像数据及深度数据,该深度数据用于描述第一图像数据对应的第一图像的景深信息。其中,与相关技术中通常采用多个不同的传输接口分别传输第二图像数据和深度数据不同,本技术实施例中第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

附图说明

26.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

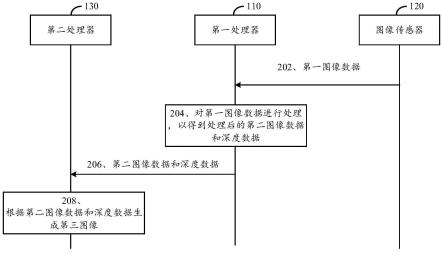

27.图1是本技术实施例公开的一种应用场景的示意图;

28.图2是本技术实施例公开的一种图像处理方法的流程示意图;

29.图3是本技术实施例公开的另一种图像处理方法的流程示意图;

30.图4是本技术实施例公开的一种传输接口的示意图;

31.图5是本技术实施例公开的一种用于说明元数据和深度数据传输过程的示意图;

32.图6是本技术实施例公开的又一种图像处理方法的流程示意图;

33.图7是本技术实施例公开的一种数据包的示意图;

34.图8是本技术实施例公开的再一种图像处理方法的流程示意图;

35.图9是本技术实施例公开的一种图像处理装置的结构示意图;

36.图10是本技术实施例公开的另一种图像处理装置的结构示意图;

37.图11是本技术实施例公开的一种电子设备的结构示意图。

具体实施方式

38.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

39.需要说明的是,本技术的说明书和权利要求书中的术语“第一”、“第二”、“第三”和“第四”等是用于区别不同的对象,而不是用于描述特定顺序。本技术实施例的术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

40.本技术实施例公开了一种图像处理方法及装置、电子设备、存储介质,能够降低图像数据传输过程的功耗。

41.下面将结合具体实施例对本技术技术方案进行详细说明。

42.为了更加清楚地说明本技术实施例公开的一种图像处理方法及装置、电子设备、存储介质,首先介绍一种适用于该方法的应用场景。请参阅图1,图1是本技术实施例公开的一种应用场景的示意图。可选的,该方法可以应用于各种具备图像采集功能和图像处理功能的设备中,包括但不限于手机、平板电脑等电子设备,以及相机等。可选的,该设备可以包括第一处理器110、图像传感器120及第二处理器130。其中,第一处理器110的输入端可以通过第一传输接口与图像传感器120连接,第一处理器110的输出端可以通过第二传输端口与第二处理器130连接。

43.其中,第一处理器110可以包括但不限于预图像信号处理器(pre-isp,pre-image signal processing)、图像信号处理器(isp,image signal processing)或者协处理器(cc,coprocessor chip)等。第一处理器110用于对图像传感器120采集的第一图像数据进行前置图像优化处理,以生成优化后的第二图像数据;其中,前置图像优化处理可以包括但不限于高动态范围成像(high dynamic range imaging,hdr)提亮、数字降噪(digital noise reduction,dnr)处理等,以提高第一图像数据对应的第一图像的画面质量;可选的,第一处理器110还可以包括景深信息提取单元,例如网络处理单元(network processing unit,npu);进而可以通过景深信息提取单元提取第一图像对应的深度数据,该深度数据用于描述第一图像的景深信息。

44.图像传感器120可以是一种能够将光学信号转换成电子信号的模块,其被广泛应用于摄像头等电子光学设备中,用于采集图像数据。可选的,图像传感器120可以被设置于各种摄像装置中,包括但不限于手机、平板电脑等电子设备的摄像头、相机的摄像头等,在此不作限定。

45.第二处理器130可以包括应用处理器(application processor,ap),其可以是通过通信协议为应用程序提供一种可管理的对系统资源的访问机制的处理器。例如,基于j2ee(java 2platform,enterprise edition)技术、ejb(enterprise javabeans)、jms(java message service)的应用处理器等,在此不作限定。

46.第一传输接口和第二传输接口可以包括但不限于移动行业处理器接口(mobile industry processor interface,mipi)、串行通用串行总线(universal serial bus,usb)或者相机串行接口(cmos sensor interface,csi)等;本技术实施例以移动行业处理器接口为例进行说明,不应对本技术实施例构成限定。

47.在一种实施例中,在摄像装置开启时,图像传感器120可以采集第一图像数据,并通过第一传输接口将第一图像数据发送给第一处理器110;第一处理器110可以对第一图像数据进行处理,以分别得到第二图像数据和深度数据,进而第一处理器110可以将第二图像数据和深度数据通过同一个第二传输接口发送给第二处理器130;第二处理器130在接收到第二图像数据和深度数据之后,根据第二图像数据和深度数据对第二图像数据对应的第二图像进行图像处理操作,以得到优化后的第三图像。

48.实施上述方法,与相关技术中通常采用多个不同的传输接口分别传输第二图像数据和深度数据不同,本技术实施例中第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

49.基于此,以下对本技术实施例公开的图像处理方法进行介绍。

50.请参阅图2,图2是本技术实施例公开的一种图像处理方法的流程示意图。可选的,该方法可以应用于图1所示的应用场景中,该方法可以包括以下步骤:

51.202、图像传感器120采集第一图像数据,并将第一图像数据发送给第一处理器110。

52.本技术实施例中,图像传感器120采集的第一图像数据可以是未经过图像优化处理的原始图像数据(或者可以称为ori data),进而图像传感器120可以将第一图像数据发送给第一处理器110,以对第一图像数据进行前置优化处理。

53.204、第一处理器110接收第一图像数据,并对第一图像数据进行处理,以得到处理后的第二图像数据和深度数据。

54.本技术实施例中,第一处理器110可以包括各种前置处理单元,用于执行各种前置优化处理;进而第一处理器110在接收到第一图像数据之后,可以通过各种前置处理单元对第一图像数据进行前置优化处理,以得到处理后的第二图像数据。

55.可选的,前置处理单元可以包括hdr处理单元和/或dnr处理单元,进而第一处理器110可以通过hdr处理单元对第一图像数据进行hdr提亮处理,和/或通过dnr处理单元对第一图像数据进行数字降噪处理,以得到优化后的第二图像数据。

56.可选的,第一处理器110还可以包括景深信息提取单元,例如网络处理单元(network processing unit,npu),进而第一处理器110可以通过景深信息提取单元提取第一图像数据对应的第一图像对应的深度数据,该深度数据用于描述第一图像的景深信息。

57.在一种实施例中,第一处理器110在上电之后,可以对包括的各种前置处理单元及景深信息提取单元进行初始化及相关数据的加载,以及可以对图像处理110内部的各种线路进行初始化,以提高第一处理器110对第一图像数据的处理效果。

58.206、第一处理器110通过同一个传输接口将第二图像数据和深度数据发送给第二处理器130。

59.本技术实施例中,第一处理器110在对第一图像数据处理,得到第二图像数据和深

度数据之后,第一处理器110可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器130。

60.可选的,传输接口可以包括移动行业处理器接口(mobile industry processor interface,mipi)。其中,移动行业处理器接口包括n条虚拟通道,n为正整数;n条虚拟通道可以用于传输不同类型的数据,进而第一处理器110可以通过不同的虚拟通道分别将第二图像数据和深度数据发送给第二处理器130,从而实现了通过同一个传输接口传输第二图像数据和深度数据。

61.而正由于第一处理器110可以通过同一个传输接口传输第二图像数据和深度数据,所以第一处理器110和第二处理器130之间可以只设置一个传输接口,从而可以在降低硬件成本的同时降低功耗。

62.208、第二处理器130接收第一处理器110发送的第二图像数据和深度数据,并根据第二图像数据和深度数据生成第三图像。

63.本技术实施例中,第二处理器130在接收到第二图像数据和深度数据之后,可以根据第二图像数据和深度数据对第二图像数据对应的第二图像进行图像优化处理,以生成第三图像。

64.可选的,图像优化处理可以包括焦外成像处理、图像渲染处理、美颜处理、图像虚化处理、图像融合处理中的一种或多种,在此不作限定。其中,优化后的第三图像可以包括肖像视频(portrait video display)。

65.实施上述各实施例公开的方法,第一处理器可以获取第一图像数据,并对第一图像数据进行处理,以分别得到处理后的第二图像数据及深度数据,该深度数据用于描述第一图像数据对应的第一图像的景深信息。其中,与相关技术中通常采用多个不同的传输接口分别传输第二图像数据和深度数据不同,本技术实施例中第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

66.请参阅图3,图3是本技术实施例公开的另一种图像处理方法的流程示意图。可选的,该方法可以应用于图1所示的应用场景中,该方法可以包括以下步骤:

67.302、图像传感器120采集第一图像数据,并将第一图像数据发送给第一处理器110。

68.304、第一处理器110将第二图像数据和深度数据存储在传输接口对应的存储空间中。

69.本技术实施例中,传输接口可以包括一个或多个存储空间,用于存储即将通过传输接口传输的数据。可选的,第一处理器110可以将第二图像数据和深度数据存储在同一个存储空间;第一处理器110也可以将第二图像数据和深度数据存储在不同的存储空间中,在此不作限定。

70.可选的,传输接口可以包括n条虚拟通道(virtual channel,vc),n为正整数。其中,各条虚拟通道可以对应一个存储空间,用于存储即将通过对应虚拟通道进行传输的数据。可选的,第一处理器110可以将第二图像数据存储至第一存储空间,以及将深度数据存储至第二存储空间,其中,第一存储空间和第二存储空间为不同的虚拟通道对应的虚拟空间。

71.需要说明的是,由于第二图像数据的数据量通常较大,所以将第二图像数据和深度数据分别存储在不同虚拟通道对应的存储空间,可以避免第二图像数据或深度数据无法全部存储到存储空间中的情况;此外,将第二图像数据和深度数据分开存储,还可以避免后续第二处理器需要解析大量的数据才能够将第二图像数据和深度数据区分开,从而可以减少第二处理器的数据处理量,进而可以降低第二处理器的功耗。

72.进一步结合图4举例来说,图4是本技术实施例公开的一种传输接口的示意图。可选的,传输接口可以包括4条虚拟通道,即vc0、vc1、vc2和vc3;其中,vc0~vc3各自对应一个存储空间,sot表示开始传输信号,eot表示结束传输信号,lps表示低功耗状态,ph表示数据包的包头,pf表示数据包的包尾。

73.可选的,第一处理器110可以将第二图像数据存储至vc0~vc3中的任一条虚拟通道对应的存储空间中,其中图4中以第二图像数据存储在vc0对应的存储空间中为例进行说明,不应对本技术实施例构成限定。即可选的,存储第二图像数据的第一存储空间可以是n条虚拟通道中第一条虚拟通道(vc0)对应的存储空间。

74.可选的,在vc0对应的存储空间用于存储第二图像数据的情况下,vc1对应的存储空间通常用于存储第二图像数据对应的元数据(metadata+3a),元数据是用于记录第二图像数据的存储位置、历史数据等信息的数据。vc2对应的存储空间用于存储包数据,即pd(pack data),而vc3对应的存储空间空闲。对此可选的,由于vc0对应的存储空间已经存储了第二图像数据,则为了避免vc0对应的存储空间不够存储深度数据的情况,第一处理器110可以将深度数据存储在vc1~vc3任一条虚拟通道中。

75.在一种实施例中,由于vc1和vc2已经用于存储数据,所以为了避免深度数据与其他数据混淆以及保证深度数据能够全部存储至存储空间中,第一处理器110可以将深度数据存储至vc3对应的存储空间中。即可选的,存储深度数据的第二存储空间可以是n条虚拟通道中,对应的存储空间未存储数据的目标虚拟通道(例如图4所示的vc3)对应的存储空间。

76.在实践中发现,第一处理器110在使用虚拟通道对应的存储空间时,需要向传输接口申请,所以第一处理器110采用vc3对应的存储空间需要申请,且申请的过程是需要消耗功耗的。对此第一处理器110可以将深度数据存储至已经申请过使用对应存储空间的vc1或者vc2中,以降低功耗。进一步可选的,由于vc1对应的存储空间中存储的元数据的数据量较小,还剩余较大的存储空间,对此第一处理器110可以将深度数据存储至存储有vc1对应的存储空间中。即可选的,第二存储空间可以是n条虚拟通道分别对应的存储空间中,存储有元数据的存储空间。

77.需要进一步说明的是,图4仅是为了方便举例说明,不应对本技术实施例构成限定。可选的,传输接口可以支持m路(lane)线路同时发送数据,其中m为正整数,m可以根据传输的图像数据的像素大小确定,典型值可以包括4、5、6等,在此不作限定。图4所示为m路线路中的一路线路。

78.在一种实施例中,第二存储空间可以是存储有第二图像数据对应的元数据的存储空间。可选的,第一处理器110可以在第二存储空间中确定第一存储地址,进而以第一存储地址作为深度数据的起始存储地址,将深度数据存储至第二存储空间中;其中,第一存储地址和第二存储地址之间间隔目标存储容量,第二存储地址可以是元数据中排列在最后一位

的数据在第二存储空间中对应的存储地址。

79.结合图5举例来说,图5是本技术实施例公开的一种用于说明元数据和深度数据传输过程的示意图。其中,第二存储地址d1和第一存储地址d2之间可以间隔目标存储容量,具体数值可以由开发人员根据大量的开发经验设定,在此不作限定。进而深度数据可以从d2开始存储。

80.实施上述方法,可以将元数据和深度数据分隔,从而避免元数据和深度数据相互干扰混淆。此外后续若元数据更新导致元数据的数据量增大,则增加的数据也可以直接存储在间隔的目标存储容量中,从而提高了该方法的灵活性。

81.作为另一种可选的实施方式,第一处理器110还可以根据深度数据生成校验码,并将该校验码添加至元数据中;进而第二处理器130在接收到深度数据和元数据之后,可以从元数据中获取校验码,并根据校验码确定接收到的深度数据是否准确。

82.可选的,校验码可以包括checksum校验码;可选的,第一处理器110可以将深度数据中的每一位数据相加,以得到校验码。进而可选的,第二处理器130可以将接收到深度数据中的每一位数据相加,得到总和,若总和与校验码相匹配,例如总和校验码相等,则确定接收到的深度数据准确;若总和与校验码不匹配,则确定接收到深度数据不准确。

83.实施上述方法,可以通过在元数据中添加校验码,并与深度数据一起发送到第二处理器端,从而使得第二处理器可以根据校验码确定接收到深度数据是否准确,避免影响后续根据深度数据对第二图像数据对应的第二图像的优化效果。

84.可选的,第二处理器130在确定接收到深度数据不准确时,可以将第一处理器110反馈重发指令,第一处理器110在接收到重发指令时,可以再次向第二处理器发送深度数据。

85.作为一种可选的实施方式,第一处理器110还可以通过传输接口根据目标数据长度对存储于第二存储空间的元数据和深度数据进行分段,以得到多个数据段;进而可以通过传输接口为每个数据段增加消息头,以得到多个数据分片,进而传输接口可以通过第二存储空间对应的虚拟通道将多个数据分片发送给第二处理器130。

86.进而第二处理器130在接收到第一处理器110发送的数据之后,可以根据消息头确定接收到数据分片属于元数据和/或深度数据。进一步可选的,第二处理器130可以在数据分片中分别解析得到元数据和深度数据。

87.可选的,第二处理器130可以按照接收顺序对从第二存储空间对应的虚拟通道接收到的数据分片进行解析,直至得到目标数据量的数据作为元数据,其中,目标数据量为元数据对应的总数据量;进而第二处理器130可以对剩余的数据分片进行解析,并将解析得到的数据作为深度数据。

88.结合图5举例来说,传输接口根据目标数据长度对元数据和深度数据进行分段,以得到多个数据段,并为每个数据段增加消息头,即图5中“ec”,以得到多个数据分片,即图5中的一行为一个“slice”。进而第二处理器130可以按照接收的顺序,图5中为从上往下的顺序解析数据分片,并在解析的数据量达到元数据的总数据量时,可以将已解析的数据作为元数据。举例来说,元数据的总数据量有2mb,则第二处理器130可以在解析到2mb时,将已解析的数据作为元数据。进一步地,第二处理器130可以对剩余的数据分片进行解析,并将解析得到的数据作为深度数据。

89.需要进一步说明的是,由于数据分片中添加的消息头也占用一定的数据量,对此在计算已经解析了多少数据量的数据时,可以减去已解析到的消息头占用的数据量。

90.实施上述方法,第一处理器可以通过传输接口为元数据和深度数据分段并添加消息头,从而方便后续第二处理器根据消息头在接收到所有数据在确定出元数据和深度,并且分段传输还方便第二处理器进行解析和将元数据和深度数据区分开。

91.306、第一处理器110通过同一个传输接口将第二图像数据和深度数据发送给第二处理器130。

92.实施上述各实施例公开的方法,第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗;以及,可以避免第二图像数据或深度数据无法全部存储到存储空间中的情况;此外,将第二图像数据和深度数据分开存储,还可以避免后续第二处理器需要解析大量的数据才能够将第二图像数据和深度数据区分开,从而可以减少第二处理器的数据处理量,进而可以降低第二处理器的功耗;以及,可以通过在元数据中添加校验码,并与深度数据一起发送到第二处理器端,从而使得第二处理器可以根据校验码确定接收到深度数据是否准确,避免影响后续根据深度数据对第二图像数据对应的第二图像的优化效果;以及,可以通过传输接口为元数据和深度数据分段并添加消息头,从而方便后续第二处理器根据消息头在接收到所有数据在确定出元数据和深度,并且分段传输还方便第二处理器进行解析和将元数据和深度数据区分开。

93.请参阅图6,图6是本技术实施例公开的又一种图像处理方法的流程示意图。可选的,该方法可以应用于图1所示的应用场景中,该方法可以包括以下步骤:

94.602、通过一个图像传感器120采集获取第一图像数据,并将第一图像数据发送给第一处理器110。

95.在相关技术中,通常采用两个图像传感器,一个用于采集第一图像数据,另一个用户采集第一图像数据的深度数据;而采集这样的架构对两个图像传感器之间的兼容性要求高,实施难度大且成本高。

96.而本技术实施例中,第一图像数据可以是仅通过一个图像传感器120采集的,进而第一处理器110可以对第一图像数据进行处理,以分别得到第二图像数据和深度数据。其中,采用“图像传感器和第一处理器”配合生成第二图像数据和深度数据的方式对兼容性的要求更低,实施难度也更低,此外仅采用一个图像传感器还可以节省成本。

97.604、第一处理器110接收第一图像数据,并对第一图像数据进行处理,以得到处理后的第二图像数据和深度数据。

98.本技术实施例中,第一处理器110在对第一图像数据处理,得到处理后的第二图像数据和深度数据之后,可以分别对第二图像数据和深度数据进行打包,以得到第二图像数据对应的第一数据包,和深度数据对应的第二数据包。

99.请参阅图7,图7是本技术实施例公开的一种数据包的示意图。可选的,第一数据包710可以包括包头、包数据,即第二图像数据和包尾组成,其中,包头包括第一虚拟通道的标识,第二图像数据的数据类型信息,其中,第一虚拟通道是后续将要传输第一数据包的虚拟通道,进而传输接口在接收到图处理器110发送的第一数据包时,可以根据包头中第一虚拟通道的标识,将第一数据包存储至第一虚拟通道对应的存储空间中,并在后续通过第一虚

拟通道传输第一数据包。

100.可选的,第二数据包可以包括深度数据和元数据,同理的,第二数据包可以包括包头、包数据和包尾;其中,第二数据包的包头可以包括第二存储空间对应的虚拟通道标识,进而后续传输接口可以将第二数据包存储至第二存储空间,进而后续传输接口可以通过第二存储空间对应的虚拟通道传输第二数据包。

101.实施上述方法,第一处理器可以在将第二图像数据和深度数据通过传输接口传输之前,可以对第二图像数据和深度数据打包,并通过数据包的包头信息中指明通过哪一条虚拟通道传输对应的数据包,从而方便传输接口根据包头将数据包存储至对应的虚拟通道的存储空间中,以使得整个数据传输过程更加有序。

102.606、第一处理器110通过同一个传输接口将第二图像数据和深度数据发送给第二处理器130。

103.作为一种可选的实施方式,第一处理器110在通过同一个传输接口将第二图像数据和深度数据发送给第二处理器的过程中,还可以通过目标校验方法对深度数据进行校验,以在检测到深度数据在传输过程中出现误码时,触发第一处理器110重新发送正确的数据。

104.可选的,目标校验方式可以包括但不限于循环冗余校验方法、奇偶校验方法、海明威验证方法或者md5信息摘要算法等,在此不作限定。

105.实施上述方法,第一处理器可以在传输深度数据的过程中对深度数据进行校验,以保证第二处理器能够接收到准确的深度数据,进而保证后续根据深度数据对第二图像数据对应的第二图像的优化效果。

106.实施上述各实施例公开的方法,第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗;以及,可以是仅通过一个图像传感器采集第一图像数据,进而第一处理器可以对第一图像数据进行处理,以分别得到第二图像数据和深度数据。其中,采用“图像传感器和第一处理器”配合生成第二图像数据和深度数据的方式对兼容性的要求更低,实施难度也更低,此外仅采用一个图像传感器还可以节省成本;以及,可以在将第二图像数据和深度数据通过传输接口传输之前,可以对第二图像数据和深度数据打包,并通过数据包的包头信息中指明通过哪一条虚拟通道传输对应的数据包,从而方便传输接口根据包头将数据包存储至对应的虚拟通道的存储空间中,以使得整个数据传输过程更加有序;以及,可以在传输深度数据的过程中对深度数据进行校验,以保证第二处理器能够接收到准确的深度数据,进而保证后续根据深度数据对第二图像数据对应的第二图像的优化效果。

107.请参阅图8,图8是本技术实施例公开的再一种图像处理方法的流程示意图。可选的,该方法可以应用于图1所示的应用场景中,该方法可以包括以下步骤:

108.802、第一处理器110通过同一个传输接口向第二处理器130发送第二图像数据和深度数据。

109.804、第二处理器130接收第一处理器110发送的第二图像数据和深度数据,并根据第二图像数据和深度数据生成第三图像。

110.实施上述方法,第二处理器可以接收第一处理器通过同一个传输接口发送的第二

图像数据和深度数据,并根据第二图像数据和深度数据生成优化后的第三图像,从而可以提高后续设备输出的图像的画面质量。此外,第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

111.请参阅图9,图9是本技术实施例公开的一种图像处理装置的结构示意图。可选的,该装置可以应用于上述的第一处理器110,该装置可以包括处理单元902和发送单元904,其中:

112.处理单元902,用于获取第一图像数据,并对第一图像数据进行处理,得到处理后的第二图像数据和深度数据,深度数据用于描述第一图像数据对应的第一图像的景深信息;

113.发送单元904,用于通过同一个传输接口将第二图像数据和深度数据发送给第二处理器。

114.实施上述装置,第一处理器可以获取第一图像数据,并对第一图像数据进行处理,以分别得到处理后的第二图像数据及深度数据,该深度数据用于描述第一图像数据对应的第一图像的景深信息。其中,与相关技术中通常采用多个不同的传输接口分别传输第二图像数据和深度数据不同,本技术实施例中第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

115.作为一种可选的实施方式,图9所示的装置还可以包括未图示的存储单元,其中:

116.存储单元,用于在通过同一个传输接口将第二图像数据和深度数据发送给第二处理器之前,将第二图像数据和深度数据存储在传输接口对应的存储空间中。

117.实施上述装置,第一处理器可以将第二图像数据和深度数据存储在传输接口对应的存储空间中,其中第二图像数据和深度数据可以存储在同一个存储空间,也可以存储在不同的存储空间中,提高了该方法的灵活性。

118.作为一种可选的实施方式,传输接口包括n条虚拟通道,n为正整数;存储单元,还用于将第二图像数据存储在第一存储空间,以及将深度数据存储在第二存储空间,第一存储空间和第二存储空间为不同的虚拟通道对应的存储空间。

119.实施上述装置,将第二图像数据和深度数据分别存储在不同虚拟通道对应的存储空间,从而可以避免第二图像数据或深度数据无法存储到存储空间中的情况;此外,将第二图像数据和深度数据分开存储,还可以避免后续第二处理器需要解析大量的数据才能够将第二图像数据和深度数据区分开,从而可以减少第二处理器的数据处理量,进而可以降低第二处理器的功耗。

120.作为一种可选的实施方式,第二存储空间还用于存储第二图像数据对应的元数据;存储单元,还用于以第一存储地址作为深度数据的起始存储地址,将深度数据存储至第二存储空间,第一存储地址和第二存储地址之间间隔目标存储容量,第二存储地址是元数据中排列在最后一位的数据在第二存储空间中对应的存储地址。

121.实施上述装置,可以将元数据和深度数据分隔,从而避免元数据和深度数据相互干扰混淆。此外后续若元数据更新导致元数据的数据量增大,则增加的数据也可以直接存储在间隔的目标存储容量中,从而提高了该方法的灵活性。

122.作为一种可选的实施方式,图9所示的装置还可以包括未图示的添加单元,其中:

123.添加单元,用于在以第一存储地址作为深度数据的起始存储地址,将深度数据存储至第二存储空间之后,根据深度数据生成校验码,并将校验码添加至元数据中,校验码用于使得第二处理器根据校验码校验接收到的深度数据是否准确。

124.实施上述装置,可以通过在元数据中添加校验码,并与深度数据一起发送到第二处理器端,从而使得第二处理器可以根据校验码确定接收到深度数据是否准确,避免影响后续根据深度数据对第二图像数据对应的第二图像的优化效果。

125.作为一种可选的实施方式,发送单元904,还用于根据目标数据长度对元数据和深度数据进行分段,得到多个数据段;以及,为每个数据段增加消息头,得到多个数据分片,消息头用于使得应用服务器根据消息头确定数据分片属于元数据和/或深度数据;以及,通过第二存储空间对应的虚拟通道将多个数据分片发送给第二处理器。

126.实施上述装置,第一处理器可以通过传输接口为元数据和深度数据分段并添加消息头,从而方便后续第二处理器根据消息头在接收到所有数据在确定出元数据和深度,并且分段传输还方便第二处理器进行解析和将元数据和深度数据区分开。

127.作为一种可选的实施方式,发送单元904,还用于将多个数据分片以数据包的形式发送给第二处理器,数据包的包头包括数据类型标识,数据类型为元数据和/或深度数据对应的数据类型。

128.作为一种可选的实施方式,元数据和深度数据以数据包的形式存储,数据包的包头包括第二存储空间对应的虚拟通道的标识。

129.实施上述装置,可以在深度数据和元数据通过传输接口传输之前,对深度数据和元数据打包,并通过数据包的包头信息中指明通过哪一条虚拟通道传输对应的数据包,从而方便传输接口根据包头将数据包存储至对应的虚拟通道的存储空间中,以使得整个数据传输过程更加有序。

130.作为一种可选的实施方式,图9所示的装置还可以包括未图示的第一校验单元,其中:

131.第一校验单元,用于在通过同一个传输接口将第二图像数据和深度数据发送给第二处理器的过程中,通过目标校验方法对深度数据进行校验。

132.实施上述装置,第一处理器可以在传输深度数据的过程中对深度数据进行校验,以保证第二处理器能够接收到准确的深度数据,进而保证后续根据深度数据对第二图像数据对应的第二图像的优化效果。

133.作为一种可选的实施方式,处理单元902,还用于通过一个图像传感器采集获取第一图像数据。

134.实施上述装置,第一图像数据可以是仅通过一个图像传感器采集的,进而第一处理器可以对第一图像数据进行处理,以分别得到第二图像数据和深度数据。其中,采用“图像传感器和第一处理器”配合生成第二图像数据和深度数据的方式对兼容性的要求更低,实施难度也更低,此外仅采用一个图像传感器还可以节省成本。

135.请参阅图10,图10是本技术实施例公开的另一种图像处理装置的结构示意图。可选的,该装置可以应用于上述的第二处理器130,该装置可以包括接收单元1002和生成单元1004,其中:

136.接收单元1002,用于接收第一处理器通过同一个传输接口发送的第二图像数据和深度数据,第二图像数据和深度数据是第一处理器对第一图像数据进行处理后得到的,深度数据用于描述第一图像数据对应的第一图像的景深信息;

137.生成单元1004,用于根据第二图像数据和深度数据生成第三图像。

138.实施上述装置,第二处理器可以接收第一处理器通过同一个传输接口发送的第二图像数据和深度数据,并根据第二图像数据和深度数据生成优化后的第三图像,从而可以提高后续设备输出的图像的画面质量。此外,第一处理器可以通过同一个传输接口将第二图像数据和深度数据发送给第二处理器,减少了传输接口的使用数量,从而可以在降低硬件成本的同时降低图像数据传输过程的功耗。

139.作为一种可选的实施方式,传输接口包括n条虚拟通道,n为正整数;图10所示的装置还包括未图示的解析单元,其中:

140.解析单元,用于在根据第二图像数据和是深度数据生成第三图像之前,根据第二图像数据和深度数据在传输接口中分别对应虚拟通道,在传输接口中解析得到第二图像数据和所述深度数据。

141.实施上述装置,第二处理器可以根据第二图像数据和深度数据在传输接口中分别对应虚拟通道,解析得到第二图像数据和深度数据,避免第二图像数据和深度数据相互干扰、混淆。

142.作为一种可选的实施方式,深度数据和第二图像数据对应的元数据以数据分片的形式通过第二存储空间对应的虚拟通道传输,数据分片包括消息头和目标数据长度的元数据和/或深度数据;解析单元,还用于按照接收顺序对从第二存储空间对应的虚拟通道接收到的数据分片进行解析,直至得到目标数据量的数据作为元数据,目标数据量为元数据对应的总数据量;以及,对剩余的数据分片进行解析,并将解析得到的数据作为深度数据。

143.实施上述装置,可以通过传输接口为元数据和深度数据分段并添加消息头,从而方便后续第二处理器根据消息头在接收到所有数据在确定出元数据和深度,并且分段传输还方便第二处理器进行解析和将元数据和深度数据区分开。

144.作为一种可选的实施方式,图10所示的装置还包括未图示的第二校验单元,其中:

145.第二校验单元,用于在对剩余的数据分片进行解析,并将解析得到的数据作为深度数据之后,从元数据中获取校验码,并根据校验码确定深度数据是否准确。

146.实施上述装置,可以通过在元数据中添加校验码,并与深度数据一起发送到第二处理器端,从而使得第二处理器可以根据校验码确定接收到深度数据是否准确,避免影响后续根据深度数据对第二图像数据对应的第二图像的优化效果。

147.作为一种可选的实施方式,生成单元1004,还用于根据第二图像数据和深度数据对第二图像数据对应的第二图像进行图像优化处理,以生成第三图像,图像优化处理包括焦外成像处理、图像渲染处理、美颜处理、图像虚化处理、图像融合处理中的一种或多种。

148.实施上述装置,根据第二图像数据和深度数据生成优化后的第三图像,从而可以提高后续设备输出的图像的画面质量。

149.请参阅图11,图11是本技术实施例公开的一种电子设备的结构示意图。

150.如图11所示,该电子设备可以包括:

151.存储有可执行程序代码的存储器1101;

152.与存储器1101耦合的处理器1102;

153.其中,处理器1102调用存储器1101中存储的可执行程序代码,执行上述各实施例公开的图像处理方法。

154.本技术实施例公开一种计算机可读存储介质,其存储计算机程序,其中,该计算机程序使得计算机执行上述各实施例公开的图像处理方法。

155.本技术实施例还公开一种应用发布平台,其中,应用发布平台用于发布计算机程序产品,其中,当计算机程序产品在计算机上运行时,使得计算机执行如以上各方法实施例中的方法的部分或全部步骤。

156.应理解,说明书通篇中提到的“一个实施例”或“一实施例”意味着与实施例有关的特定特征、结构或特性包括在本技术的至少一个实施例中。因此,在整个说明书各处出现的“在一个实施例中”或“在一实施例中”未必一定指相同的实施例。此外,这些特定特征、结构或特性可以以任意适合的方式结合在一个或多个实施例中。本领域技术人员也应该知悉,说明书中所描述的实施例均属于可选实施例,所涉及的动作和模块并不一定是本技术所必须的。

157.在本技术的各种实施例中,应理解,上述各过程的序号的大小并不意味着执行顺序的必然先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

158.上述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物单元,即可位于一个地方,或者也可以分布到多个网络单元上。可根据实际的需要选择其中的部分或全部单元来实现本实施例方案的目的。

159.另外,在本技术各实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

160.上述集成的单元若以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可获取的存储器中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或者部分,可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储器中,包括若干请求用以使得一台计算机设备(可以为个人计算机、服务器或者网络设备等,具体可以是计算机设备中的处理器)执行本技术的各个实施例上述方法的部分或全部步骤。

161.本领域普通技术人员可以理解上述实施例的各种方法中的全部或部分步骤是可以通过程序来指令相关的硬件来完成,该程序可以存储于一计算机可读存储介质中,存储介质包括只读存储器(read-only memory,rom)、随机存储器(random access memory,ram)、可编程只读存储器(programmable read-only memory,prom)、可擦除可编程只读存储器(erasable programmable read only memory,eprom)、一次可编程只读存储器(one-time programmable read-only memory,otprom)、电子抹除式可复写只读存储器(electrically-erasable programmable read-only memory,eeprom)、只读光盘(compact disc read-only memory,cd-rom)或其他光盘存储器、磁盘存储器、磁带存储器、或者能够用于携带或存储数据的计算机可读的任何其他介质。

162.以上对本技术实施例公开的一种图像处理方法及装置、电子设备、存储介质进行

了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的一般技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1