存储器控制电路单元、存储装置及时钟信号控制方法与流程

1.本发明涉及一种存储器控制技术,尤其涉及一种存储器控制电路单元、存储器存储装置及时钟信号控制方法。

背景技术:

2.动态随机存取存储器(dynamic random access memory,dram)等易失性存储器具有存取速度快及体积小等优势,故相当适于设置于可携式电子装置中,以作为数据的暂存媒体。此外,存储器控制器可用以控制并存取易失性存储器。

3.一般来说,存储器控制器用来与易失性存储器沟通的时钟信号的工作周期(duty cycle)是在存储器控制器出厂前就设定好的(例如为40%或50%等),而不会针对不同的操作状态而进行动态调整。但是,实务上,使用固定的工作周期的时钟信号无法在对于易失性存储器的多种类型的存取操作(例如数据写入操作与数据读取操作)中皆取得最佳信号质量。

技术实现要素:

4.本发明提供一种存储器控制电路单元、存储器存储装置及时钟信号控制方法,可提高对易失性存储器模块的存取信号质量。

5.本发明的范例实施例提供一种存储器控制电路单元,其用以控制易失性存储器模块,所述存储器控制电路单元包括存储器接口电路与存储器控制器。所述存储器接口电路用以连接至所述易失性存储器模块。所述存储器控制器连接至所述存储器接口电路。所述存储器控制器用以通过所述存储器接口电路对所述易失性存储器模块执行存取操作。所述存储器接口电路用以根据所述存取操作的类型设定第一时钟信号的工作周期。所述存储器接口电路更用以将所述第一时钟信号传送至所述易失性存储器模块,以执行所述存取操作。

6.在本发明的一范例实施例中,所述存储器接口电路根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的操作包括:响应于所述存取操作为第一类存取操作,将所述第一时钟信号的所述工作周期设定为第一工作周期;以及响应于所述存取操作为第二类存取操作,将所述第一时钟信号的所述工作周期设定为第二工作周期,其中所述第一类存取操作不同于所述第二类存取操作,且所述第一工作周期不同于所述第二工作周期。

7.在本发明的一范例实施例中,所述第一类存取操作为数据读取操作,且所述第二类存取操作为数据写入操作。

8.在本发明的一范例实施例中,所述存储器接口电路更用以存储工作周期设定数据,并且响应于所述存取操作为所述第二类存取操作,将所述第一时钟信号的所述工作周期设定为所述第二工作周期的操作包括:响应于所述存取操作为所述第二类存取操作,根据所述工作周期设定数据将所述第一时钟信号的所述工作周期从所述第一工作周期切换

为所述第二工作周期。

9.在本发明的一范例实施例中,在所述第二类存取操作完成后,所述存储器接口电路更用以将所述第一时钟信号的所述工作周期从所述第二工作周期回复为所述第一工作周期。

10.在本发明的一范例实施例中,所述存储器接口电路根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的操作包括:响应于所述存取操作的所述类型改变,调整所述第一时钟信号的所述工作周期。

11.在本发明的一范例实施例中,所述存储器接口电路更用以将第二时钟信号传送至所述易失性存储器模块,且所述第二时钟信号的工作周期为预设值。

12.在本发明的一范例实施例中,所述存储器接口电路包括内部时钟产生器与第一时钟路径电路。所述第一时钟路径电路连接至所述存储器控制器、所述内部时钟产生器及所述易失性存储器模块。所述内部时钟产生器用以产生内部时钟信号。所述第一时钟路径电路用以根据所述内部时钟信号产生所述第一时钟信号。所述存储器控制器用以根据所述存取操作的所述类型产生致能信号。所述第一时钟路径电路更用以根据所述致能信号调整所述第一时钟信号的所述工作周期。

13.在本发明的一范例实施例中,所述存储器接口电路更包括写入路径电路,其连接至所述存储器控制器与所述内部时钟产生器。所述写入路径电路用以根据所述致能信号、所述内部时钟信号及内部数据信号产生数据信号。所述存储器接口电路更用以将所述数据信号传送至所述易失性存储器模块。

14.在本发明的一范例实施例中,所述存储器接口电路更包括第二时钟路径电路,其连接至所述内部时钟产生器与所述易失性存储器模块。所述第二时钟路径电路用以根据所述内部时钟信号产生第二时钟信号。所述第二时钟信号的工作周期为预设值。所述存储器接口电路更用以将所述第二时钟信号传送至所述易失性存储器模块。

15.本发明的范例实施例另提供一种存储器存储装置,其包括连接接口单元、可复写式非易失性存储器模块、易失性存储器模块及存储器控制电路单元。所述连接接口单元用以连接至主机系统。所述存储器控制电路单元连接至所述连接接口单元、所述可复写式非易失性存储器模块及所述易失性存储器模块。所述存储器控制电路单元用以:通过存储器接口电路对所述易失性存储器模块执行存取操作;根据所述存取操作的类型设定第一时钟信号的工作周期;以及将所述第一时钟信号传送至所述易失性存储器模块,以执行所述存取操作。

16.在本发明的一范例实施例中,所述存储器控制电路单元根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的操作包括:响应于所述存取操作为第一类存取操作,将所述第一时钟信号的所述工作周期设定为第一工作周期;以及响应于所述存取操作为第二类存取操作,将所述第一时钟信号的所述工作周期设定为第二工作周期,其中所述第一类存取操作不同于所述第二类存取操作,且所述第一工作周期不同于所述第二工作周期。

17.在本发明的一范例实施例中,所述存储器控制电路单元更用以存储工作周期设定数据,并且响应于所述存取操作为所述第二类存取操作,将所述第一时钟信号的所述工作周期设定为所述第二工作周期的操作包括:响应于所述存取操作为所述第二类存取操作,

根据所述工作周期设定数据将所述第一时钟信号的所述工作周期从所述第一工作周期切换为所述第二工作周期。

18.在本发明的一范例实施例中,在所述第二类存取操作完成后,所述存储器控制电路单元更用以将所述第一时钟信号的所述工作周期从所述第二工作周期回复为所述第一工作周期。

19.在本发明的一范例实施例中,所述存储器控制电路单元根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的操作包括:响应于所述存取操作的所述类型改变,调整所述第一时钟信号的所述工作周期。

20.在本发明的一范例实施例中,所述存储器接口电路更用以将第二时钟信号传送至所述易失性存储器模块,且所述第二时钟信号的工作周期为预设值。

21.本发明的范例实施例另提供一种时钟信号控制方法,其用于存储器控制电路单元,所述时钟信号控制方法包括:通过存储器接口电路对易失性存储器模块执行存取操作;根据所述存取操作的类型设定第一时钟信号的工作周期;以及将所述第一时钟信号传送至所述易失性存储器模块,以执行所述存取操作。

22.在本发明的一范例实施例中,根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的步骤包括:响应于所述存取操作为第一类存取操作,将所述第一时钟信号的所述工作周期设定为第一工作周期;以及响应于所述存取操作为第二类存取操作,将所述第一时钟信号的所述工作周期设定为第二工作周期,其中所述第一类存取操作不同于所述第二类存取操作,且所述第一工作周期不同于所述第二工作周期。

23.在本发明的一范例实施例中,所述存储器接口电路用以存储工作周期设定数据,并且响应于所述存取操作为所述第二类存取操作,将所述第一时钟信号的所述工作周期设定为所述第二工作周期的步骤包括:响应于所述存取操作为所述第二类存取操作,根据所述工作周期设定数据将所述第一时钟信号的所述工作周期从所述第一工作周期切换为所述第二工作周期。

24.在本发明的一范例实施例中,根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的步骤更包括:在所述第二类存取操作完成后,将所述第一时钟信号的所述工作周期从所述第二工作周期回复为所述第一工作周期。

25.在本发明的一范例实施例中,根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的步骤包括:响应于所述存取操作的所述类型改变,调整所述第一时钟信号的所述工作周期。

26.在本发明的一范例实施例中,所述的时钟信号控制方法更包括:将第二时钟信号传送至所述易失性存储器模块,其中所述第二时钟信号的工作周期为预设值。

27.在本发明的一范例实施例中,根据所述存取操作的所述类型设定所述第一时钟信号的所述工作周期的步骤包括:产生内部时钟信号;根据所述内部时钟信号产生所述第一时钟信号;根据所述存取操作的所述类型产生致能信号;以及根据所述致能信号调整所述第一时钟信号的所述工作周期。

28.在本发明的一范例实施例中,所述的时钟信号控制方法更包括:根据所述致能信号、所述内部时钟信号及内部数据信号产生数据信号;以及将所述数据信号传送至所述易失性存储器模块。

29.在本发明的一范例实施例中,所述的时钟信号控制方法更包括:根据所述内部时钟信号产生第二时钟信号,其中所述第二时钟信号的工作周期为预设值;以及将所述第二时钟信号传送至所述易失性存储器模块。

30.基于上述,存储器控制器可通过存储器接口电路对易失性存储器模块执行存取操作。特别是,存储器接口电路可根据所述存取操作的类型设定第一时钟信号的工作周期并将所述第一时钟信号传送至所述易失性存储器模块,以执行所述存取操作。因此,通过根据不同的存取操作来动态调整第一时钟信号的工作周期,可有效提高对易失性存储器模块的存取信号质量。

附图说明

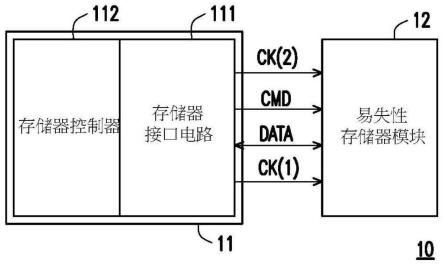

31.图1是根据本发明的范例实施例所示出的存储器存储装置的示意图;

32.图2是根据本发明的范例实施例所示出的根据存取操作的类型设定第一时钟信号的工作周期的示意图;

33.图3是根据本发明的范例实施例所示出的存储器存储装置的示意图;

34.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图;

35.图5是根据本发明的范例实施例所示出的时钟信号控制方法的流程图。

具体实施方式

36.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

37.以下提出多个范例实施例来说明本发明,然而本发明不仅限于所例示的多个范例实施例。又范例实施例之间也允许有适当的结合。在本案说明书全文(包括权利要求)中所使用的“连接”一词可指任何直接或间接的连接手段。举例而言,若文中描述第一装置连接于第二装置,则应该被解释成该第一装置可以直接连接于该第二装置,或者该第一装置可以通过其他装置或某种连接手段而间接地连接至该第二装置。此外,“信号”一词可指至少一电流、电压、电荷、温度、数据、或任何其他一或多个信号。

38.图1是根据本发明的范例实施例所示出的存储器存储装置的示意图。请参照图1,存储器存储装置10包括存储器控制电路单元11与易失性存储器模块12。

39.存储器控制电路单元11可用以控制并存取易失性存储器模块12。例如,存储器控制电路单元11可包括中央处理单元(central processing unit,cpu)、图形处理单元(graphics processing unit,gpu)或是其他可编程的一般用途或特殊用途的微处理器、数字信号处理器(digital signal processor,dsp)、可编程控制器、专用集成电路(application specific integrated circuits,asic)、可编程逻辑器件(programmable logic device,pld)或其他类似装置或这些装置的组合。

40.易失性存储器模块12可用以暂存数据。例如,易失性存储器模块12可包括第5代双通道同步动态随机存取存储器(double data rate 5sdram)或其他类型的易失性存储器。存储器控制电路单元11可将数据存入易失性存储器模块12中或者从易失性存储器模块12中读取数据。此外,易失性存储器模块12的数目可以是一或多个,本发明不加以限制。

41.存储器控制电路单元11可包括存储器接口电路111与存储器控制器112。存储器接

口电路111并用以连接至易失性存储器模块12。例如,存储器接口电路111可通过外设部件互连局部总线(peripheral component interconnect express,pci express)标准或其他类型的连接接口标准与易失性存储器模块12通信。

42.存储器控制器112连接至存储器接口电路111。存储器控制器112可通过存储器接口电路111对易失性存储器模块12执行存取操作。例如,所述存取操作可包括数据读取操作与数据写入操作。数据读取操作用以从易失性存储器模块12读取数据。数据写入操作用以将数据写入(即存储)至易失性存储器模块12中。在一范例实施例中,存储器控制器112亦称为动态随机存取存储器控制器(sram controller)。

43.存储器控制器112可根据所欲执行的存取操作,通过存储器接口电路111发送相应的指令信号cmd给易失性存储器模块12。易失性存储器模块12可根据指令信号cmd执行相应的存取行为。

44.在一范例实施例中,在数据读取操作中,存储器控制器112可通过存储器接口电路111将带有读取指令序列的指令信号cmd传送给易失性存储器模块12。此读取指令序列可指示易失性存储器模块12从特定的逻辑地址(或虚拟地址)读取数据。此逻辑地址(或虚拟地址)所对应的存储器地址位于易失性存储器模块12内部。易失性存储器模块12可根据带有读取指令序列的指令信号cmd从特定存储器地址读取数据并通过数据信号data将所读取的数据传送给存储器接口电路111。存储器控制器112可通过存储器接口电路111解析数据信号data以获得所欲读取的数据。

45.在一范例实施例中,在数据写入操作中,存储器控制器112可通过存储器接口电路111将带有写入指令序列的指令信号cmd与带有所欲存储的数据的数据信号data传送给易失性存储器模块12。此写入指令序列可指示易失性存储器模块12将数据信号data所携带的数据写入(即存储)至特定的逻辑地址(或虚拟地址)。此逻辑地址(或虚拟地址)所对应的存储器地址同样位于易失性存储器模块12内部。易失性存储器模块12可根据指令信号cmd与数据信号data将所欲存储的数据写入至内部的特定存储器地址。

46.在一范例实施例中,存储器接口电路111可产生时钟信号(亦称为第一时钟信号)ck(1)并将时钟信号ck(1)传送至易失性存储器模块12。易失性存储器模块12可根据时钟信号ck(1)来执行相应的数据读取和/或数据写入行为。例如,在数据读取操作中,易失性存储器模块12可根据时钟信号ck(1)来传送数据信号data至存储器接口电路111。此外,在数据写入操作中,易失性存储器模块12可根据时钟信号ck(1)来取样来自存储器接口电路111的数据信号data以获得所欲存储的数据。

47.存储器接口电路111可根据所欲执行的存取操作的类型来设定时钟信号ck(1)的工作周期。须注意的是,时钟信号ck(1)的工作周期表示在一个时钟周期(clock cycle)内,时钟信号ck(1)中的工作时间(例如正半周的持续时间或脉冲持续时间)与总时间长度的比率。例如,假设时钟信号ck(1)的工作周期为47%,表示在时钟信号ck(1)的一个时钟周期内,时钟信号ck(1)中的工作时间(例如正半周的持续时间或脉冲持续时间)占总时间长度的47%。然后,存储器接口电路11可将具有所设定的工作周期的时钟信号ck(1)传送至易失性存储器模块12,以执行相应的存取操作。

48.传统上,存储器控制器用来与易失性存储器沟通的时钟信号的工作周期是在存储器控制器出厂前就设定好的(例如为40%或50%等),而不会针对不同的操作状态而进行动

态调整。但是,实务上,使用固定的工作周期的时钟信号无法在对于易失性存储器的多种类型的存取操作(例如数据写入操作与数据读取操作)中皆取得最佳信号质量。反观本案,根据所欲执行的存取操作的类型来设定时钟信号ck(1)的工作周期,则可有效针对不同类型的存取行为来提高易失性存储器模块12的存取信号质量。

49.在一范例实施例中,响应于所欲执行的存取操作为第一类存取操作,存储器接口电路111可将时钟信号ck(1)的工作周期设定为某一工作周期(亦称为第一工作周期)。尔后,易失性存储器模块12可根据具有第一工作周期的时钟信号ck(1)来执行第一类存取操作。例如,具有第一工作周期的时钟信号ck(1)可用以提高易失性存储器模块12执行第一类存取操作的信号质量。但是,具有第一工作周期的时钟信号ck(1)可能无法提高甚至可能降低易失性存储器模块12执行第二类存取操作的信号质量。

50.在一范例实施例中,响应于所欲执行的存取操作为第二类存取操作,存储器接口电路111可将时钟信号ck(1)的工作周期设定为另一工作周期(亦称为第二工作周期)。第一类存取操作不同于第二类存取操作,且第一工作周期不同于第二工作周期。尔后,易失性存储器模块12可根据具有第二工作周期的时钟信号ck(1)来执行第二类存取操作。例如,具有第二工作周期的时钟信号ck(1)可用以提高易失性存储器模块12执行第二类存取操作的信号质量。但是,具有第二工作周期的时钟信号ck(1)可能无法提高甚至可能降低易失性存储器模块12执行第一类存取操作的信号质量。

51.在一范例实施例中,假设第一类存取操作为数据读取操作,且第二类存取操作为数据写入操作。因此,第一工作周期可为47%,且第二工作周期可为40%,但本发明不限于此。在其他范例实施例中,根据存取操作的类型,第一工作周期和/或第二工作周期皆可根据实务需求调整。

52.在一范例实施例中,第一工作周期为时钟信号ck(1)的预设工作周期,且存储器接口电路111中可存储有工作周期设定数据。例如,所述工作周期设定数据可包含可用以设定和/或调整时钟信号ck(1)的工作周期的信息。例如,所述工作周期设定数据可包含对应于上述第二工作周期的设定信息。例如,所述工作周期设定数据可反映上述第二工作周期在一个时钟周期中的占比(例如为40%)。此外,所述工作周期设定数据亦可包含对应于上述第一工作周期的设定信息。例如,所述工作周期设定数据亦可反映上述第一工作周期在一个时钟周期中的占比(例如为47%)。存储器接口电路111可根据所述工作周期设定数据来设定(包含调整和/或切换)时钟信号ck(1)的工作周期。或者,在一范例实施例中,所述工作周期设定数据亦可反映时钟信号ck(1)在一或多种使用情境下的工作周期的设定值。

53.在一范例实施例中,响应于所欲执行的存取操作为第二类存取操作,存储器接口电路111可根据所述工作周期设定数据将时钟信号ck(1)的工作周期从第一工作周期(即预设工作周期)切换为第二工作周期。在第二类存取操作完成后,存储器接口电路111可将时钟信号ck(1)的工作周期从第二工作周期回复为第一工作周期(即预设工作周期)。例如,第二类存取操作完成,是指对应于单次的数据写入操作的一或多个写入指令序列已全数向易失性存储器模块12发送或者抵达易失性存储器模块12。所述写入指令序列用以指示易失性存储器模块12存储数据。此外,响应于所欲执行的存取操作为第一类存取操作,存储器接口电路111可将时钟信号ck(1)的工作周期维持于第一工作周期(即预设工作周期)。

54.在一范例实施例中,若所欲执行的存取操作的类型没有改变,例如先前执行的存

取操作与下一个执行的存取操作的类型相同(例如皆为第一类存取操作或第二类存取操作),存储器接口电路111可不调整时钟信号ck(1)的工作周期。然而,响应于所欲执行的存取操作的类型改变,例如从先前执行的第一类存取操作改变为执行第二类存取操作或者从先前执行的第二类存取操作改变为执行第一类存取操作,则存储器接口电路111可调整时钟信号ck(1)的工作周期,以提高易失性存储器模块12执行下一个或当前的存取操作的信号质量。

55.在一范例实施例中,存储器接口电路111还可产生时钟信号(亦称为第二时钟信号)ck(2)并将时钟信号ck(2)传送至易失性存储器模块12。易失性存储器模块12可根据时钟信号ck(2)来取得控制器端的基本时钟。例如,易失性存储器模块12可根据时钟信号ck(2)来设定其内部的参考时钟。但是,须注意的是,相较于时钟信号ck(1),时钟信号ck(2)的工作周期为预设值,而不会根据所欲执行的存取操作的类型而改变。此外,时钟信号ck(1)与ck(2)可通过不同的接口或信号路径传送至易失性存储器模块12。

56.图2是根据本发明的范例实施例所示出的根据存取操作的类型设定第一时钟信号的工作周期的示意图。请参照图1与图2,假设在时间点t(1)之后,存储器控制器112通过存储器接口电路111传送读取指令序列给易失性存储器模块12,以指示易失性存储器模块12执行数据读取操作。响应于所欲执行的存取操作为数据读取操作(例如为第一类存取操作),存储器接口电路111可将时钟信号ck(1)的工作周期设定(或维持)为d(1)(例如为第一工作周期或预设工作周期)。例如,d(1)所对应的时间长度可占时钟信号ck(1)的一个时钟周期内的总时间长度的47%,且d(1)所对应的时间长度可根据实务需求调整。因此,在时间点t(1)之后,读取指令序列可与工作周期为d(1)的时钟信号ck(1)同步传送至易失性存储器模块12。易失性存储器模块12可根据工作周期为d(1)的时钟信号ck(1)与所述读取指令序列执行数据读取操作,以提升易失性存储器模块12执行数据读取操作的信号质量。

57.在执行数据读取操作后,在时间点t(2)之后,存储器控制器112通过存储器接口电路111传送写入指令序列给易失性存储器模块12,以指示易失性存储器模块12执行数据写入操作。响应于所欲执行的存取操作改变为数据写入操作(例如为第二类存取操作),存储器接口电路111可将时钟信号ck(1)的工作周期从d(1)调整为d(2)(例如为第二工作周期)。例如,d(2)所对应的时间长度可占时钟信号ck(1)的一个时钟周期内的总时间长度的40%,且d(2)所对应的时间长度可根据实务需求调整。因此,在时间点t(2)之后,写入指令序列可与工作周期为d(2)的时钟信号ck(1)同步传送至易失性存储器模块12。易失性存储器模块12可根据工作周期为d(2)的时钟信号ck(1)与所述写入指令序列执行数据写入操作,以提升易失性存储器模块12执行数据写入操作的信号质量。

58.在执行数据写入操作后,在时间点t(3)之后,存储器控制器112再次通过存储器接口电路111传送读取指令序列给易失性存储器模块12,以指示易失性存储器模块12执行数据读取操作。响应于所欲执行的存取操作改变(或回复)为数据读取操作(例如为第一类存取操作),存储器接口电路111可将时钟信号ck(1)的工作周期从d(2)调整(例如回复)为d(1)(例如为第一工作周期或预设工作周期)。因此,在时间点t(3)之后,读取指令序列可与工作周期为d(1)的时钟信号ck(1)同步传送至易失性存储器模块12。易失性存储器模块12可回复为根据工作周期为d(1)的时钟信号ck(1)与所述读取指令序列执行数据读取操作,以提升易失性存储器模块12执行数据读取操作的信号质量。此外,在一范例实施例中,在写

入指令序列发送完毕后,存储器接口电路111亦可自动将时钟信号ck(1)的工作周期从d(2)调整(例如回复)为d(1),无论是否发送新的读取指令序列或执行下一个数据读取操作。

59.须注意的是,在图2的范例实施例中,不同类型的存取操作的执行顺序及各种类型的存取操作所对应的时钟信号ck(1)的工作周期皆为范例,非用以限制本发明。

60.图3是根据本发明的范例实施例所示出的存储器存储装置的示意图。请参照图3,存储器存储装置30包括存储器控制电路单元31与易失性存储器模块32。存储器控制电路单元31与易失性存储器模块32可分别相同或相似于图1的存储器控制电路单元11与易失性存储器模块12。

61.存储器控制电路单元31包括存储器接口电路311与存储器控制器312。存储器接口电路311与存储器控制器312可分别相同或相似于图1的存储器接口电路111与存储器控制器112。

62.存储器接口电路311包括内部时钟产生器33与时钟路径(clock path)电路(亦称为第一时钟路径电路)34。内部时钟产生器33用以产生时钟信号(亦称为内部时钟信号)ick。时钟路径电路34连接至存储器控制器312、内部时钟产生器33及易失性存储器模块32。时钟路径电路34可接收时钟信号ick与致能信号(亦称为第一致能信号)wck_en。时钟路径电路34可根据时钟信号ick与致能信号wck_en产生时钟信号ck(1)。

63.另一方面,存储器控制器312可根据欲执行的存取操作的类型产生致能信号(亦称为第二致能信号或写入致能信号)wd_en。时钟路径电路34还可接收致能信号wd_en。时钟路径电路34可根据致能信号wd_en来调整时钟信号ck(1)的工作周期。或者,从另一角度而言,时钟路径电路34可根据致能信号wd_en、时钟信号ick及致能信号wck_en产生时钟信号ck(1)。然后,时钟路径电路34可将时钟信号ck(1)传送给易失性存储器模块32。

64.在一范例实施例中,在某一时间点,响应于当前所欲执行的存取操作为第一类存取操作(例如为数据读取操作),存储器控制器312可不产生致能信号wd_en。在此情况下,时钟路径电路34可根据时钟信号ick与致能信号wck_en产生具有第一工作周期的时钟信号ck(1)。然而,在另一时间点,响应于当前所欲执行的存取操作为第二类存取操作(例如为数据写入操作),存储器控制器312可产生致能信号wd_en。在此情况下,时钟路径电路34可根据致能信号wd_en、时钟信号ick及致能信号wck_en产生具有第二工作周期的时钟信号ck(1)。

65.在一范例实施例中,存储器接口电路311还包括时钟路径电路(亦称为第二时钟路径电路)35。时钟路径电路35连接至内部时钟产生器33与易失性存储器模块32。时钟路径电路35可接收时钟信号ick并根据时钟信号ick将时钟信号ck(2)传送给易失性存储器模块32。须注意的是,时钟信号ck(2)的工作周期可为预设值,而不根据所欲执行的存取操作的类型而改变。

66.在一范例实施例中,存储器接口电路311还包括指令路径(command path)电路36。指令路径电路36连接至存储器控制器312、内部时钟产生器33及易失性存储器模块32。指令路径电路36用以从存储器控制器312接收与欲执行的存取操作有关的指令信息ca并从内部时钟产生器33接收时钟信号ick。指令路径电路36可根据指令信息ca与时钟信号ick将指令信号cmd传送至易失性存储器模块32。指令信号cmd可带有指令序列(例如读取指令序列或写入指令序列)。易失性存储器模块32可根据指令信号cmd执行相应的存取操作。

67.在一范例实施例中,存储器接口电路311还包括写入路径(write path)电路37、读

取路径(read path)电路38及多工器(multiplexer)电路39。写入路径电路37与读取路径电路38皆连接至存储器控制器312与内部时钟产生器33。多工器电路39连接至写入路径电路37、读取路径电路38及易失性存储器模块32。写入路径电路37与读取路径电路38皆可从内部时钟产生器33接收时钟信号ick。

68.当存储器控制器312执行数据写入操作时,写入路径电路37可从存储器控制器312接收致能信号wd_en与内部数据信号wr_dq。写入路径电路37可根据致能信号wd_en、内部时钟信号ick及内部数据信号wr_dq产生数据信号data。数据信号data带有与所欲存储的数据有关信息。例如,数据信号data可包括rdqst信号与dq信号。rdqst信号可用以传送与欲存储的数据有关的错误更正码的信息。dq信号则可用以传送欲存储的数据。写入路径电路37可通过多工器电路39将数据信号data传送至易失性存储器模块32。同时,响应于致能信号wd_en,时钟路径电路34可将具有第二工作周期的时钟信号ck(1)传送给易失性存储器模块32。易失性存储器模块32可根据来自存储器接口电路311的指令信号cmd、数据信号data及具有第二工作周期的时钟信号ck(1)执行数据写入操作。

69.另一方面,当存储器控制器312执行数据读取操作时,时钟路径电路34未接收到致能信号wd_en,故时钟路径电路34可将具有第一工作周期的时钟信号ck(1)传送给易失性存储器模块32。易失性存储器模块32可根据来自存储器接口电路311的指令信号cmd与具有第一工作周期的时钟信号ck(1)执行数据读取操作。读取路径电路38可通过多工器电路39从易失性存储器模块32接收数据信号data。来自易失性存储器模块32的数据信号data可带有与所欲读取的数据有关的信息。读取路径电路38可根据数据信号data将rdqs信号与rd_dq信号传送给存储器控制器312。例如,rdqs信号可用以传送对应于rd_dq信号的时钟信号。rd_dq信号则可用以传送所读取的数据。

70.图4是根据本发明的范例实施例所示出的存储器存储装置的示意图。请参照图4,存储器存储装置40包括连接接口单元41、存储器控制电路单元42、可复写式非易失性存储器模块43及易失性存储器模块44。

71.连接接口单元41用以将存储器存储装置40连接主机系统11。存储器存储装置40可通过连接接口单元41与主机系统通信。在一范例实施例中,连接接口单元41是相容于外设部件互连局部总线(pci express)标准。在一范例实施例中,连接接口单元41亦可以是符合串行高级技术附件(serial advanced technology attachment,sata)标准、并行高级技术附件(parallel advanced technology attachment,pata)标准、电气和电子工程师协会(institute of electrical and electronic engineers,ieee)1394标准、通用串行总线(universal serial bus,usb)标准、sd接口标准、超高速一代(ultra high speed-i,uhs-i)接口标准、超高速二代(ultra high speed-ii,uhs-ii)接口标准、存储棒(memory stick,ms)接口标准、mcp接口标准、mmc接口标准、emmc接口标准、通用快闪存储器(universal flash storage,ufs)接口标准、emcp接口标准、cf接口标准、整合式驱动电子接口(integrated device electronics,ide)标准或其他适合的标准。连接接口单元41可与存储器控制电路单元42封装在一个芯片中,或者连接接口单元41是布设于一包含存储器控制电路单元42的芯片外。

72.存储器控制电路单元42连接至连接接口单元41与可复写式非易失性存储器模块43。存储器控制电路单元42用以执行以硬件型式或固件型式实作的多个逻辑门或控制指令

并且根据主机系统的指令在可复写式非易失性存储器模块43中进行数据的写入、读取与抹除等运作。此外,存储器控制电路单元42可包括图1的存储器控制电路单元11或图3的存储器控制电路单元31。

73.可复写式非易失性存储器模块43用以存储主机系统所写入的数据。可复写式非易失性存储器模块43可包括单阶存储单元(single level cell,slc)nand型快闪存储器模块(即,一个存储单元中可存储1个比特的快闪存储器模块)、二阶存储单元(multi level cell,mlc)nand型快闪存储器模块(即,一个存储单元中可存储2个比特的快闪存储器模块)、三阶存储单元(triple level cell,tlc)nand型快闪存储器模块(即,一个存储单元中可存储3个比特的快闪存储器模块)、四阶存储单元(quad level cell,qlc)nand型快闪存储器模块(即,一个存储单元中可存储4个比特的快闪存储器模块)、其他快闪存储器模块或其他具有相同特性的存储器模块。

74.可复写式非易失性存储器模块43中的每一个存储单元是以电压(以下亦称为临界电压)的改变来存储一或多个比特。具体来说,每一个存储单元的控制门(control gate)与通道之间有一个电荷捕捉层。通过施予一写入电压至控制门,可以改变电荷补捉层的电子量,进而改变存储单元的临界电压。此改变存储单元的临界电压的操作亦称为“把数据写入至存储单元”或“程序化(programming)存储单元”。随着临界电压的改变,可复写式非易失性存储器模块43中的每一个存储单元具有多个存储状态。通过施予读取电压可以判断一个存储单元是属于哪一个存储状态,因此取得此存储单元所存储的一或多个比特。

75.在一范例实施例中,可复写式非易失性存储器模块43的存储单元可构成多个实体程序化单元,并且此些实体程序化单元可构成多个实体抹除单元。具体来说,同一条字线上的存储单元可组成一或多个实体程序化单元。若一个存储单元可存储2个以上的比特,则同一条字线上的实体程序化单元可至少可被分类为下实体程序化单元与上实体程序化单元。例如,一存储单元的最低有效比特(least significant bit,lsb)是属于下实体程序化单元,并且一存储单元的最高有效比特(most significant bit,msb)是属于上实体程序化单元。一般来说,在mlc nand型快闪存储器中,下实体程序化单元的写入速度会大于上实体程序化单元的写入速度,和/或下实体程序化单元的可靠度是高于上实体程序化单元的可靠度。

76.在一范例实施例中,实体程序化单元为程序化的最小单元。即,实体程序化单元为写入数据的最小单元。例如,实体程序化单元可为实体页(page)或是实体扇(sector)。若实体程序化单元为实体页,则此些实体程序化单元可包括数据比特区与冗余(redundancy)比特区。数据比特区包含多个实体扇,用以存储用户数据,而冗余比特区用以存储系统数据(例如,错误更正码等管理数据)。在一范例实施例中,数据比特区包含32个实体扇,且一个实体扇的大小为512字节(byte,b)。然而,在其他范例实施例中,数据比特区中也可包含8个、16个或数目更多或更少的实体扇,并且每一个实体扇的大小也可以是更大或更小。另一方面,实体抹除单元为抹除的最小单位。亦即,每一实体抹除单元含有最小数目的一并被抹除的存储单元。例如,实体抹除单元为实体区块(block)。

77.易失性存储器模块44用以易失性地存储数据。例如,易失性存储器模块44可包括图1的易失性存储器模块12或图3的易失性存储器模块32。存储器控制电路单元42亦可用以存取易失性存储器模块44。

78.图5是根据本发明的范例实施例所示出的时钟信号控制方法的流程图。请参照图5,在步骤s501中,通过存储器接口电路对易失性存储器模块执行存取操作。在步骤s502中,根据所述存取操作的类型设定第一时钟信号的工作周期。在步骤s503中,将所述第一时钟信号传送至所述易失性存储器模块,以执行所述存取操作。

79.然而,图5中各步骤已详细说明如上,在此便不再赘述。值得注意的是,图5中各步骤可以实作为多个程序码或是电路,本案不加以限制。此外,图5的方法可以搭配以上范例实施例使用,也可以单独使用,本案不加以限制。

80.综上所述,本发明实施例提供的存储器控制电路单元、存储器存储装置及时钟信号控制方法,可根据不同的存取操作来动态调整第一时钟信号的工作周期,可有效提高对易失性存储器模块的存取信号质量。

81.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1