分析集成电路时序变化的制作方法

本发明涉及电路设计和实现,并且更具体地分析电路设计的时序。

背景技术:

1、分析集成电路设计的时序对于基于该设计构建的集成电路的正常运行是必不可少的。然而,用于确定时序的当前方法存在精度或性能不足的问题。当前的静态时序分析方法在分析整个芯片时具有高性能,但会牺牲精度,因为简化的静态模型会失去噪声和自适应时钟的动态影响。当前的动态分析方法(例如spice)具有精确的动态噪声和时钟模型,但性能非常有限。这些方法仅在分析一小部分仅代表设计一小部分的选定路径时才实用,这在用于签署整个芯片设计时会产生过度概括的风险。所需要的是一种高性能方法,该方法能够实际执行整个芯片时序变化分析,而不会牺牲噪声和自适应时钟模型的精确动态影响。

2、附图的简要说明

3、图1示出了根据实施例的用于在考虑电压噪声的同时执行电路测试的方法的流程图;

4、图2示出了根据实施例的用于使用混合方法执行电路测试的方法的流程图;

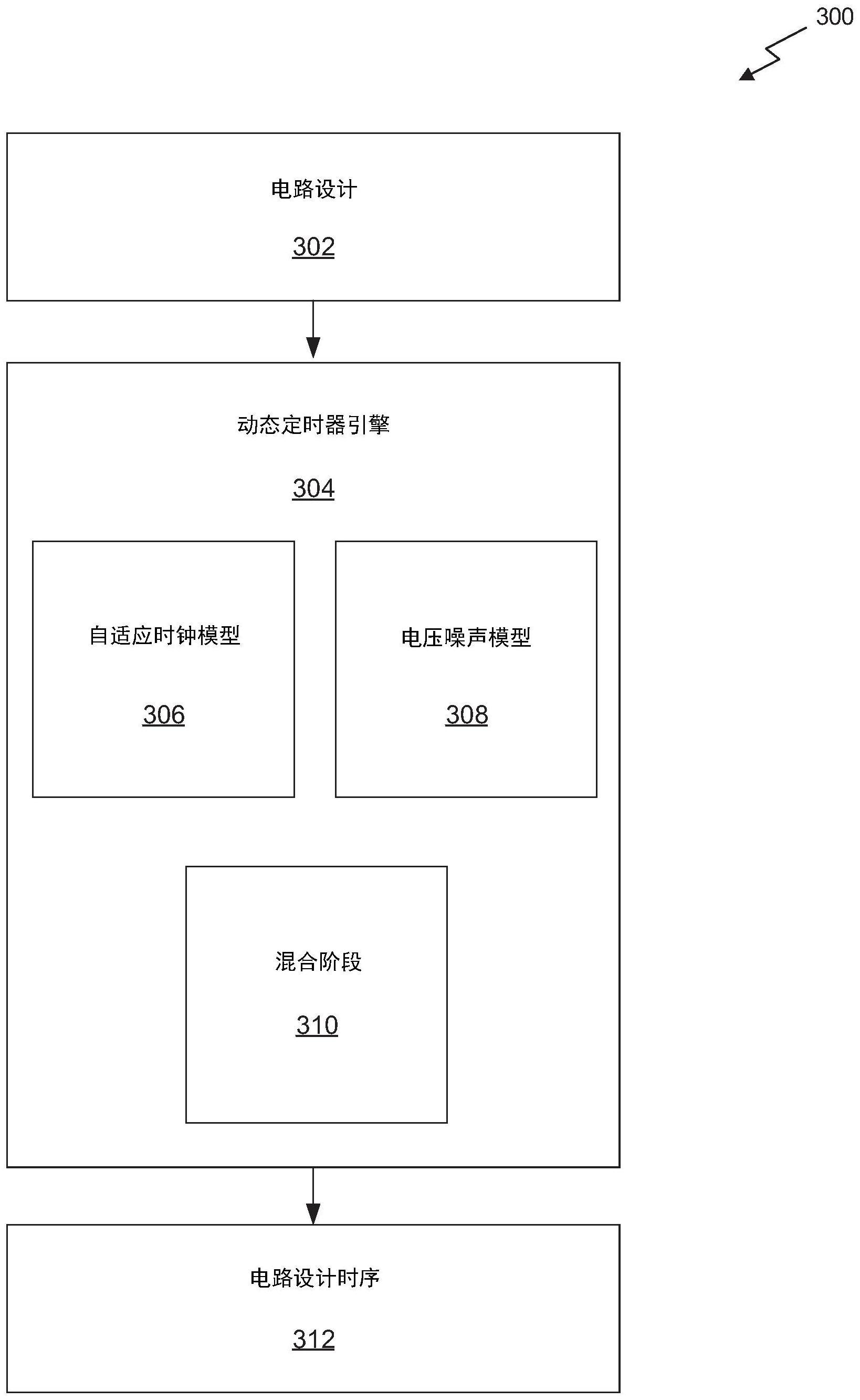

5、图3示出了根据实施例的示例性动态测试环境;

6、图4示出了示例性系统,其中可以实现各种先前实施例的各种架构和/或功能;

7、图5为示出被配置为实现各个实施例的一个或更多个方面的计算机系统的框图。

技术实现思路

技术特征:

1.一种方法,包括,在设备处:

2.如权利要求1所述的方法,其中在确定所述时序时还使用自适应时钟模型。

3.如权利要求1所述的方法,其中在每个时钟周期期间,在确定所述电路设计的时序的同时:

4.如权利要求1所述的方法,其中所述电压噪声模型包括一个或更多个电源的原始电源噪声波形。

5.如权利要求4所述的方法,其中所述原始电源噪声波形是由物理电压源产生的。

6.如权利要求4所述的方法,其中在确定所述电路设计的所述时序时使用所述原始电源噪声波形而不是固定电压。

7.如权利要求4所述的方法,包括:在确定所述时序的同时计算门延迟,其中检查所述原始电源噪声波形以确定在信号到达所述电路设计的门输入引脚时门的实际工作电压。

8.如权利要求7所述的方法,包括:

9.如权利要求1所述的方法,包括:基于所确定的时序调整所述电路设计。

10.如权利要求1所述的方法,包括:基于所述电路设计构建硬件电路。

11.一种系统,包括:

12.如权利要求11所述的系统,其中所述电压噪声模型包括一个或更多个电源的原始电源噪声波形。

13.一种非暂时性计算机可读存储介质,其存储指令,所述指令在由设备的处理器执行时,使所述处理器使所述设备:

14.如权利要求13所述的计算机可读存储介质,其中所述电压噪声模型包括一个或更多个电源的原始电源噪声波形。

15.一种方法,包括,在设备处:

16.如权利要求15所述的方法,其中包括所述基于图的方法和所述基于路径的方法两者的混合阶段用于确定所述电路设计的所述时序。

17.如权利要求16所述的方法,其中所述混合阶段包括对所述电路设计内的延迟的计算。

18.如权利要求16所述的方法,其中所述混合阶段包括驱动单元、在所述驱动单元的输出处的网的rc网络、所述电路设计内的网络负载引脚的电容性负载,以及路径、周期和逻辑唯一化输入信号。

19.如权利要求15所述的方法,其中利用所述基于图的方法,为所述电路设计构建有向无环图dag,其中所述dag表示所述电路设计内的所有路径。

20.如权利要求19所述的方法,其中在所述电路设计的分析期间,所述dag中的每个门仅被访问一次。

21.如权利要求19所述的方法,其中利用所述基于路径的方法,来自所述电路设计内的与门相关的所有路径和周期的所有延迟计算在对所述门的单次访问期间执行并且在所述电路设计的整个其余部分中传播。

22.如权利要求16所述的方法,其中所述混合阶段对所述电路设计进行模拟,并且所述模拟分为输入相关部分和输入无关部分,

23.如权利要求19所述的方法,其中在所述电路设计的测试期间在不同路径之间共享逻辑相同的输入延迟。

24.如权利要求19所述的方法,其中在所述电路设计内的不同路径、波形和场景之间共享在预定阈值内相同或具有差异的延迟和噪声值。

25.一种系统,包括:

26.如权利要求25所述的系统,其中利用所述基于图的方法,为所述电路设计构建有向无环图dag,其中所述dag表示所述电路设计内的所有路径。

27.一种非暂时性计算机可读存储介质,其存储指令,所述指令在由设备的处理器执行时,使所述处理器使所述设备:

28.如权利要求27所述的计算机可读存储介质,其中利用所述基于图的方法,为所述电路设计构建有向无环图dag,其中所述dag表示所述电路设计内的所有路径。

技术总结

本公开涉及分析集成电路时序变化。在电路设计测试期间,在测试环境的计算机实现的方法中使用自适应时钟模型和电压噪声模型,以确定电压变化和自适应时钟对电路设计时序的动态影响。计算机实现的方法使用结合了基于图的方法和基于路径的方法的混合阶段,也可以将其结合到测试环境中,以便最大化电路设计的测试性能。

技术研发人员:李春辉,S·普拉缇,泰扎斯威·拉贾,W·岳,V·B·斯里纳特

受保护的技术使用者:辉达公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!