一种无减法器的快速除三电路的设计方法与流程

本发明涉及无减法器的快速除三电路设计领域,特别涉及一种无减法器的快速除三电路的设计方法。

背景技术:

1、乘积码(product codes)也被称作an码,使用乘积码进行运算可以保护算术运算免受电路故障的影响。使用乘积码进行容错的原理为将一个数n表示为乘积an,其中a为校验模数常量,通过对运算结果进行关于a的整除性检查,可以确定本次运算过程中是否出现错误。乘积码是一种不可分编码(nonseparate codes),原始数据与用于检查的冗余信息是混杂在一起的,需要除以校验模数常量a得到最终的运算结果。

2、校验模数常量a为奇数的an码可以检测出运算过程中出现的全部单比特错误,并且为了确保an码编码过程易于实现,校验模数常量a常选用低成本乘积码(low costproduct codes),其形式为a=2a-1,因此an码的编码过程可以通过对数n的移位和减法运算得到,常用的校验模数常量a的值为3,即a=22-1。

3、目前对an码的运算结果进行关于a的整除性检查,都是使用除法器进行的,通过运算得到商和余数,商为最终的运算结果,余数用于对本次算术运算过程中是否出现错误进行判断。

4、目前除法器主要基于减法器进行实现,通过迭代减法运算得到商,每次迭代运算可以确定有限位数的商,因此对于多比特数的除法运算,需要多次迭代才能完成,导致使用乘积码进行容错的算术运算单元在执行结果检查时的时间开销大。

技术实现思路

1、本发明的目的是提供一种无减法器的快速除三电路的设计方法,通过构建基本除三运算单元,对基本除三运算单元进行级联实现多比特数的除三运算,可以快速得到商和余数,运算过程中无需任何减法器,解决了使用乘积码进行容错的算术运算单元在执行结果检查时的时间开销大的问题。

2、本发明解决其技术问题,采用的技术方案是:

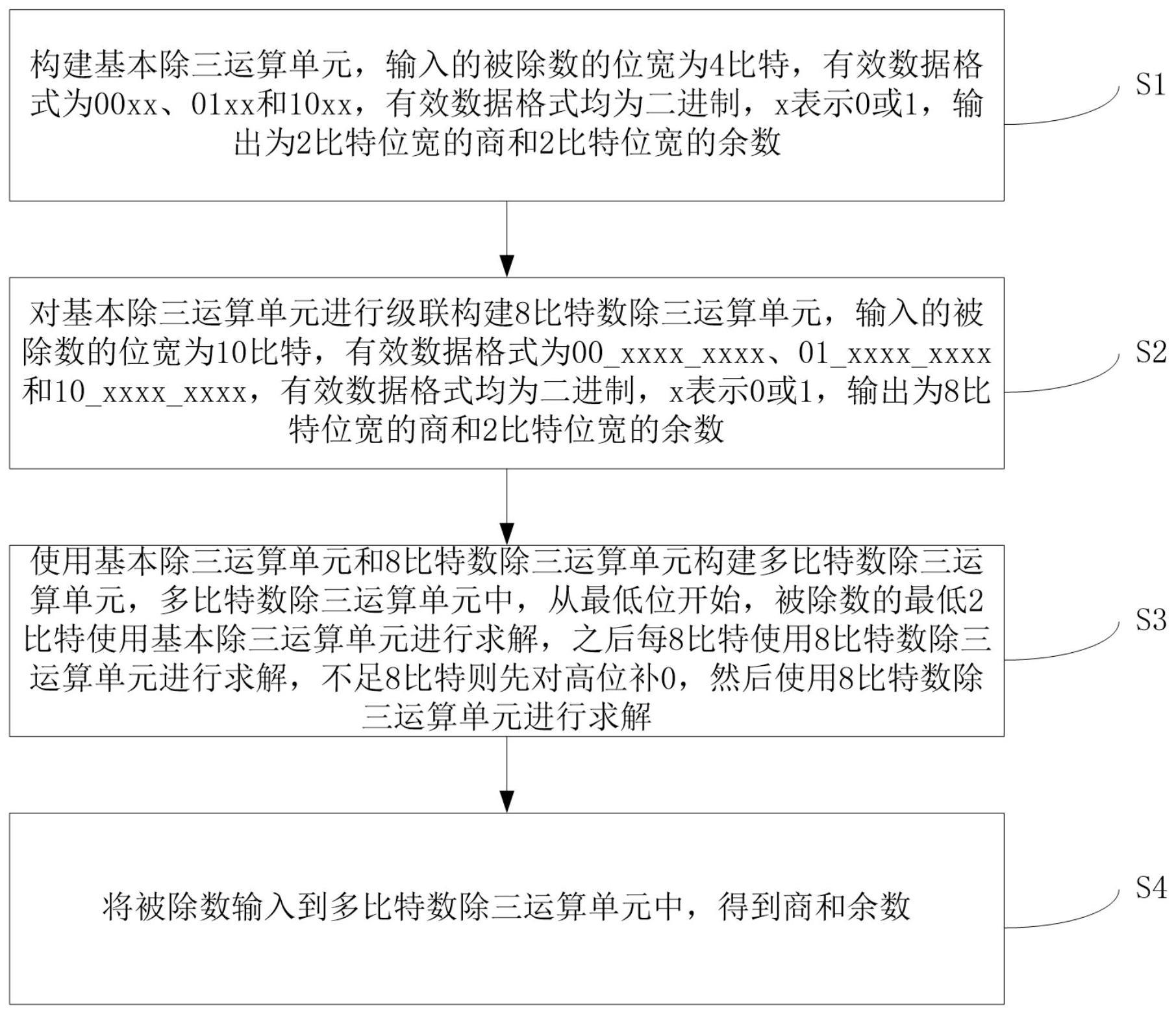

3、本发明提出的是一种无减法器的快速除三电路的设计方法,包括如下步骤:

4、构建基本除三运算单元,输入的被除数的位宽为4比特,有效数据格式为00xx、01xx和10xx,有效数据格式均为二进制,x表示0或1,输出为2比特位宽的商和2比特位宽的余数;

5、对基本除三运算单元进行级联构建8比特数除三运算单元,输入的被除数的位宽为10比特,有效数据格式为00_xxxx_xxxx、01_xxxx_xxxx和10_xxxx_xxxx,有效数据格式均为二进制,x表示0或1,输出为8比特位宽的商和2比特位宽的余数;

6、使用基本除三运算单元和8比特数除三运算单元构建多比特数除三运算单元,多比特数除三运算单元中,从最低位开始,被除数的最低2比特使用基本除三运算单元进行求解,之后每8比特使用8比特数除三运算单元进行求解,不足8比特则先对高位补0,然后使用8比特数除三运算单元进行求解;

7、将被除数输入到多比特数除三运算单元中,得到商和余数。

8、作为进一步优化,使用查表法构建所述基本除三运算单元。

9、作为进一步优化,所述基本除三运算单元包括商值查找表和余数查找表,输入的被除数被用作商值查找表和余数查找表的地址选择。

10、作为进一步优化,通过4个基本除三运算单元以串联方式级联构建所述8比特数除三运算单元。

11、作为进一步优化,所述基本除三运算单元输入的被除数和8比特数除三运算单元输入的被除数的最高2位的有效输入均为00、01或10,且均为二进制。

12、作为进一步优化,所述基本除三运算单元输出的余数和8比特数除三运算单元输出的余数的取值均为00、01或10,且均为二进制。

13、作为进一步优化,采用串联方式或并联方式级联构建所述多比特数除三运算单元。

14、本发明的有益效果是:通过上述一种无减法器的快速除三电路的设计方法,可以实现多比特数的除三运算,相比于常规除三运算电路,此方法在运算过程中不借助减法器,算术运算延时小,并且,避免了使用乘积码进行容错的算术运算单元在执行运算结果检查时的时间开销大的问题。

技术特征:

1.一种无减法器的快速除三电路的设计方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的一种无减法器的快速除三电路的设计方法,其特征在于,使用查表法构建所述基本除三运算单元。

3.根据权利要求1所述的一种无减法器的快速除三电路的设计方法,其特征在于,所述基本除三运算单元包括商值查找表和余数查找表,输入的被除数被用作商值查找表和余数查找表的地址选择。

4.根据权利要求1-3任意一项所述的一种无减法器的快速除三电路的设计方法,其特征在于,通过4个基本除三运算单元以串联方式级联构建所述8比特数除三运算单元。

5.根据权利要求4所述的一种无减法器的快速除三电路的设计方法,其特征在于,所述基本除三运算单元输入的被除数和8比特数除三运算单元输入的被除数的最高2位的有效输入均为00、01或10,且均为二进制。

6.根据权利要求5所述的一种无减法器的快速除三电路的设计方法,其特征在于,所述基本除三运算单元输出的余数和8比特数除三运算单元输出的余数的取值均为00、01或10,且均为二进制。

7.根据权利要求1所述的一种无减法器的快速除三电路的设计方法,其特征在于,采用串联方式或并联方式级联构建所述多比特数除三运算单元。

技术总结

本发明涉及无减法器的快速除三电路设计领域,提出一种无减法器的快速除三电路的设计方法,该方法包括:构建基本除三运算单元,输入的被除数的位宽为4比特,输出为2比特位宽的商和2比特位宽的余数;对基本除三运算单元进行级联构建8比特数除三运算单元,输入的被除数的位宽为10比特,输出为8比特位宽的商和2比特位宽的余数;使用基本除三运算单元和8比特数除三运算单元构建多比特数除三运算单元,从最低位开始,被除数的最低2比特使用基本除三运算单元进行求解,之后每8比特使用8比特数除三运算单元进行求解,不足8比特则先对高位补0,然后使用8比特数除三运算单元进行求解;将被除数输入到多比特数除三运算单元中,得到商和余数。

技术研发人员:梁宗南,刘鸿瑾,年嘉伟,高鑫,高嘉轩,张绍林,杨孟飞

受保护的技术使用者:北京轩宇空间科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!