一种基于Winograd的相关算法加速器存储方法与流程

一种基于winograd的相关算法加速器存储方法

技术领域

1.本公开属于神经网络存储技术领域,具体而言涉及一种基于winograd的相关算法加速器存储方法。

背景技术:

2.随着深度学习技术的快速发展,卷积神经网络(convolutional neural network,cnn)开始用于图像匹配定位算法。该算法由cnn和相关(correlation)算法组成,其中cnn用于基准图与实时图的特征提取,相关算法用于对cnn提取的特征数据进行相关运算,提取相关极大值。由于cnn的海量计算与存储,一般由深度学习处理器(deep-learning processing unit,dpu)完成计算。但是由于相关算法的计算特征与深度学习算法差异较大,导致dpu通常对其计算效率极低,从而催生了基于fpga的相关算法加速器。

技术实现要素:

3.本公开正是基于现有技术的上述需求而提出的,本公开要解决的技术问题是提供一种基于winograd的相关算法加速器存储方法以降低加速器对片外存储带宽的需求。

4.为了解决上述问题,本公开提供的技术方案包括:

5.提供了一种基于winograd的相关算法加速器存储方法,包括:s1分别获取相关结果矩阵块和实时图矩阵块的大小,分别获取相关结果矩阵和实时图张量的大小,获取加速单元的通道并行度;s2由片外存储向基准张量第一区域存储cb×

(m+r-1)

×

pn的基准图张量块,其中,cb为基准图张量宽度,m为相关结果矩阵块的宽度,r为实时图矩阵块的宽度,pn为加速单元的通道并行度;s3由片外存储向实时张量缓存cr×r×

n的实时图张量块,其中,cr为实时图张量的宽度,n为实时图张量的通道数;s4由基准图张量缓存中的第一区域读取数据,将读取的最后两行数据写入基准图张量缓存中的第二区域的前两行,同时从外部存储中读取接下来的四行写入第二区域,重复cb×

r个时钟周期;s5由基准张量缓存中读取大小为(r-1)

×

(m+r-1)

×

pn的张量块,并预写入基准张量寄存器组;s6由实时图张量缓存向实时图张量图寄存器写入r

×r×

pn大小的张量块;s7将基准寄存器组的前列数据搬移到后列,同时将基准张量缓存中读取数据到寄存器组的前列;s8在不同的寄存器组之间进行处理和计算后写入张量寄存器组。

6.优选地,所述s1中,所述基准张量缓存包括m

×

(m+r-1)个独立的存储体,每个存储体对应基准张量的一行,分为m组。

7.优选地,所述s2中,当实时张量缓存中的数据重用完后,由片外存储中加载新的数据覆盖。

8.优选地,所述s5中,由基准张量缓存从m-1组和m-2组中读取大小为(r-1)

×

(m+r-1)

×

pn的张量块,并预写入基准张量寄存器组的前r-1列。

9.优选地,所述s5在所述s2之后进行。

10.优选地,所述s6和s5同时进行。

11.优选地,所述s8包括:将基准张量寄存器组和实时张量寄存器组中的数据经变换后分别写入v张量寄存器组和u张量寄存器组;将v张量寄存器组和u张量寄存器组中的数据对应逐点相乘后,写入e张量寄存器组。

12.优选地,所述s8还包括:将e张量寄存器组中的数据经变换后写入s张量寄存器组;同时从过程张量缓存中读取中间结果数据至偏置张量寄存器组。

13.优选地,所述s8还包括:将s张量寄存器组中的数据沿通道方向累加后,与偏置寄存器组中的数据逐点相加,并写入过程张量寄存器组中。

14.优选地,s8直至完成当前实时张量块对基准图张量一整行数据的扫描后结束。

15.与现有技术相比,本公开满足计算单元高吞吐量的数据需求的同时,能够利用尽可能少的片上bram资源,实现尽可能高的数据复用率,从而降低加速器对片外存储带宽的需求。

附图说明

16.为了更清楚地说明本说明书实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本说明书实施例中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

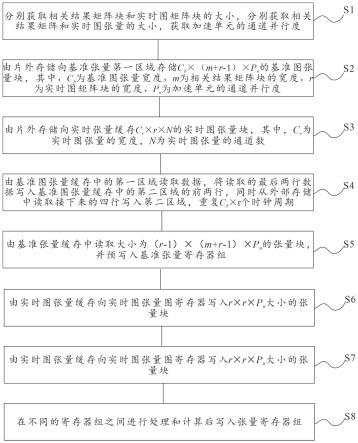

17.图1为本公开一种基于winograd的相关算法加速器存储方法的步骤流程图;

18.图2为本公开基于winograd的相关算法加速器存储系统的架构图;

19.图3为本公开实施例中片外存储基准图数据排布方式的示意图;

20.图4为本公开基准图缓存和基准寄存器组的连接和数据传输示意图。

具体实施方式

21.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

22.在本公开实施例的描述中,需要说明的是,除非另有明确的规定和限定,术语“相连”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接可以是机械连接,也可以是电连接可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

23.全文中描述使用的术语“顶部”、“底部”、“在

……

上方”、“下”和“在

……

上”是相对于装置的部件的相对位置,例如装置内部的顶部和底部衬底的相对位置。可以理解的是装置是多功能的,与它们在空间中的方位无关。

24.为便于对本技术实施例的理解,下面将结合附图以具体实施例做进一步的解释说明,实施例并不构成对本技术实施例的限定。

25.本实施例提供了一种基于winograd的相关算法加速器存储方法,如图1-图4所示。

26.为超越fpga上dsp资源的限制,本发明提出利用winograd算法对相关算法进行加速。

27.相关算法的基于其基本原理可将实时张量视为相关窗口,该相关窗口顺序地扫过基准图张量,得到相关结果矩阵。每个相关窗口内实时张量与基准图张量进行乘累加运算,得到一个相关结果值。表示如下:

[0028][0029]

0《cc《cc[0030]

0《rc《rc[0031]

0《n《n

[0032]

其中,c为相关结果矩阵,cc为相关结果矩阵内元素的列索引,rc为相关结果矩阵内元素的行索引,n为实时图张量的通道数,rr为实时图张量的高度,cr为实时图张量的宽度,b表示基准图张量,cb为基准图张量内元素的列索引,rb为基准图张量内元素的行索引,n为输入通道的索引,r表示实时图张量,cr为实时图张量内元素的列索引,rr为实时图张量内元素的行索引。

[0033]

此外,相关结果矩阵的宽度表示为:

[0034]cc

=c

b-cr+1

[0035]

其中,cc为相关结果矩阵宽度,cb为基准图张量宽度,cr为实时图张量宽度。

[0036]

相关结果矩阵的高度表示为:

[0037]

rc=r

b-rr+1

[0038]

其中,rc为相关结果矩阵高度,rb为基准图张量高度,rr为实时图张量高度。

[0039]

winograd算法的基本原理可用以下表达式表达:

[0040]

y=a

t

[[ggg

t

]e[b

t

db]]a

[0041]

其中y表示m

×

m大小的相关结果矩阵块,g表示r

×

r大小的实时图矩阵块,d表示(m+r-1)

×

(m+r-1)大小的基准图矩阵块。即,将实时图矩阵块g和基准图矩阵块d分别经过g矩阵和b矩阵变换后,进行逐点相乘,再经过a矩阵反变换得到相关结果矩阵块y。为方便起见,上述表达式记为f(m

×

m,r

×

r)。

[0042]

则基于winograd算法加速计算相关算法的基本原理得到:

[0043][0044]

其中,cc为相关结果矩阵内分块的列索引,rc为相关结果矩阵内分块的行索引,cb为基准图张量内分块的列索引,rb为基准图张量内分块的行索引,cr为实时图张量内分块的列索引,rr为实时图张量内分块的行索引。

[0045]

实时图张量r的分块方式包括rr与cr,表示为:

[0046][0047][0048]

相关结果矩阵c的分块方式包括rc与cc,表示为:

[0049][0050][0051]

基准图张量b的分块个数rb与cb与相关结果矩阵c相同,但分块大小不同,且相邻分块间的重叠区宽度为(r-1)。

[0052]

本方法基于相关算法加速器存储系统实现,如图2所示,所述相关算法加速器存储系统包括片外存储、片上张量缓存以及多个寄存器。所述片上张量缓存包括基准张量缓存、实时张量缓存以及过程张量缓存,所述多个寄存器包括基准张量寄存器组、实时张量寄存器组、过程张量寄存器组以及偏置张量寄存器组、v张量寄存器组、u张量寄存器组、e张量寄存器组以及s张量寄存器组。所述片外存储与片上张量缓存通过数据加载单元相连,具体而言,所述片外存储通过axi数据总线与数据加载单元相连,数据加载单元通过fifo数据线分别与基准张量缓存和实时张量缓存相连,所述基准张量缓存依次连接基准张量寄存器组、基准图变换单元和v张量寄存器组;所述实时张量缓存依次连接实时张量寄存器组、实时图变换单元和u张量寄存器组;v张量寄存器组和u张量寄存器组均连接到逐点相乘单元,由逐点相乘单元输出数据至e张量寄存器中,e张量寄存器与结果变换单元相连,并连接s张量寄存器组,所述s张量寄存器组连接通道累加单元,经过通道累加单元的处理后,输入至过程张量寄存器组,所述过程张量寄存器组与过程张量缓存相连,并通过fifo数据线输入至数据卸载单元中,最后通过axi数据总线输出至片外存储上。

[0053]

如图1所示,所述存储方法包括:

[0054]

s1分别获取相关结果矩阵块和实时图矩阵块的大小,分别获取相关结果矩阵和实时图张量的大小,获取加速单元的通道并行度。

[0055]

s2由片外存储向基准张量第一区域存储cb×

(m+r-1)

×

pn的基准图张量块,其中,cb为基准图张量宽度,m为相关结果矩阵块的宽度,r为实时图矩阵块的宽度,pn为加速单元的通道并行度

[0056]

基准图张量缓存用于缓存当前计算所需的基准图张量块,基于本加速器的数据重用策略设计,每次需缓存大小为cb×

(m+r-1)

×

pn的张量块。它的结构与加速单元采用的winograd的算法相关,表示为:

[0057]

bufb[m][m+r-1][db][pn]

[0058]

对于f(m

×

m,r

×

r),共需要m

×

(m+r-1)个独立的存储体。其中,bufb为基准图的缓存,m表示winograd中相关结果矩阵的宽度,(m+r-1)为基准图矩阵块的高度。每个存储体的宽度为(pn×

bitb)比特,db为存储体的深度,pn是加速单元在输入通道方向上的并行度,bitb为基准图特征数据的位宽。

[0059]

每个存储体的深度需满足大于基准图宽度最大值的2倍,即:

[0060]

db≥max(cb)

×2[0061]

也就是说该缓存每个时钟周期最大可读写大小为m

×

(m+r-1)

×

pn的基准图张量块。

[0062]

为充分利用fpga中的bram资源,基准图张量缓存采用双口ram实现,沿深度方向设置乒乓的读写区域。基于上述存储体的深度需求可知,如基准图的最大宽度小于等于256,

则该缓存的深度为512。将深度方向0~255的区域设置为“乒区域”,256~511的区域设置为“乓区域”。在加速单元读取“乒区域”的数据进行计算时,数据加载器可向“乓区域”缓存新的数据,反之亦然,从而达到数据计算与传输的并行。“乒区域”对应于第一区域,“乓区域”对应于第二区域。

[0063]

s3由片外存储向实时张量缓存cr×r×

n的实时图张量块,其中,cr为实时图张量的宽度,n为实时图张量的通道数。

[0064]

实时图张量缓存用于缓存当前计算所需的实时图张量块,基于本加速器的数据重用策略设计,每次需缓存大小为cr×r×

n的张量块。它的结构与加速单元采用的winograd的算法相关,表示为:

[0065]

bufr[r][dr][pn]

[0066]

对于f(m

×

m,r

×

r),共需要r个独立的存储体,其中bufr为实时图的缓存,r表示实时图矩阵块的高度,dr表示每个存储体的深度。每个存储体的宽度为(pn×

bitr)比特,bitr为实时图特征数据的位宽,即该缓存每个时钟周期最大可读写大小为1

×r×

pn的基准图张量块。每个存储体的深度大于实时图宽度与通道分块乘积的最大值,即:

[0067][0068]

s4由基准图张量缓存中的第一区域读取数据,将读取的最后两行数据写入基准图张量缓存中的第二区域的前两行,同时从外部存储中读取接下来的四行写入第二区域,重复cb×

r个时钟周期。

[0069]

由winograd算法和相关算法的基本原理可知,相邻基准图矩阵分块之间的重叠区宽度为(r-1),则基准图张量缓存的“乒乓”读写区域之间,有(r-1)行数据是相同的。为了降低片外访存带宽需求,可在读取“乒区域”数据的同时,将最后两行,即第(m+r-2)行和第(m+r-3)行的数据写入“乓区域”,反之亦然。由于首次向“乒区域”缓存数据时,它的全部数据需从ddr获取,通过上述方式,除首次向“乒区域”缓存数据外,每次只需从ddr向单个读写区域缓存m行数据,可降低(r-1)/(m+r-1)的基准图数据的ddr传输量。

[0070]

s5由基准张量缓存中读取大小为(r-1)

×

(m+r-1)

×

pn的张量块,并预写入基准张量寄存器组。

[0071]

基准张量寄存器组从基准图张量缓存中加载数据,并向基准图变换单元提供数据。基准图变换单元每个时钟周期吞吐大小为(m+r-1)

×

(m+r-1)

×

pn的张量块,但是由于相邻基准图矩阵分块之间的重叠区宽度为(r-1),故每个时钟周期只需从基准图张量缓存中读取大小为m

×

(m+r-1)

×

pn的张量块,剩余的大小为(r-1)

×

(m+r-1)

×

pn的张量块通过寄存器组内部搬移实现。

[0072]

s6由实时图张量缓存向实时图张量图寄存器写入r

×r×

pn大小的张量块。

[0073]

实时图张量缓存用于缓存当前计算所需的实时图张量块,基于本加速器的数据重用策略设计,每次需缓存大小为cr×r×

n的张量块。它的结构与加速单元采用的winograd的算法相关,表示为:

[0074]

bufr[r][dr][pn]

[0075]

对于f(m

×

m,r

×

r),共需要r个独立的存储体,其中bufr为实时图的缓存,r表示实时图矩阵块的高度,dr表示每个存储体的深度。每个存储体的宽度为(pn×

bitr)比特,bitr为实时图特征数据的位宽,即该缓存每个时钟周期最大可读写大小为1

×r×

pn的基准图张量块。每个存储体的深度大于实时图宽度与通道分块乘积的最大值,即:

[0076][0077]

实时张量寄存器组从实时图张量缓存加载数据,并向实时图变换单元提供数据,寄存器组的大小为r

×r×

pn。基于本加速器的数据重用策略设计,实时张量寄存器每隔(cc/m)个时钟周期更新一次。由实时图张量缓存的最大带宽可知,该寄存器组完成一次更新需要r个时钟周期。

[0078]

s7将基准寄存器组的前列数据搬移到后列,同时将基准张量缓存中读取数据到寄存器组的前列。

[0079]

s8在不同的寄存器组之间进行处理和计算后写入张量寄存器组。

[0080]

所述s8包括:将基准张量寄存器组和实时张量寄存器组中的数据经变换后分别写入v张量寄存器组和u张量寄存器组;将v张量寄存器组和u张量寄存器组中的数据对应逐点相乘后,写入e张量寄存器组。

[0081]

v张量寄存器组接收基准图变换单元的输出数据,并向逐点相乘单元提供数据,寄存器组的大小为(m+r-1)

×

(m+r-1)

×

pn。

[0082]

u张量寄存器组接收实时图变换单元的输出数据,并向逐点相乘单元提供数据,寄存器组的大小为(m+r-1)

×

(m+r-1)

×

pn。

[0083]

所述s8还包括:将e张量寄存器组中的数据经变换后写入s张量寄存器组;同时从过程张量缓存中读取中间结果数据至偏置张量寄存器组。

[0084]

e张量寄存器组接收逐点相乘单元的输出数据,并向结果变换单元提供数据,寄存器组的大小为(m+r-1)

×

(m+r-1)

×

pn。

[0085]

s张量寄存器组接收结果变换单元的输出数据,并向通道累加单元提供数据,寄存器组的大小为m

×m×

pn。

[0086]

所述s8还包括:将s张量寄存器组中的数据沿通道方向累加后,与偏置寄存器组中的数据逐点相加,并写入过程张量寄存器组中。

[0087]

偏置张量寄存器组从过程张量缓存中加载数据,并向通道累加单元提供数据,寄存器组的大小为m

×m×

1。

[0088]

过程张量寄存器组接收通道累加单元的数据,并写入过程张量缓存,寄存器的大小为m

×m×

1。

[0089]

过程张量缓存用于缓存当前计算产生的中间结果数据,基于本加速器的数据重用策略设计,需缓存大小为cc×

rc的相关结果矩阵的全部中间结果数据。它的结构与加速单元采用的winograd的算法相关,表示为:

[0090]

bufc[m][m][dc]

[0091]

对于f(m

×

m,r

×

r),共需要m

×

m个独立的存储体,其中bufc为过程的缓存,m表示相关结果矩阵块的尺寸。每个存储体的宽度为(1

×

bitc)比特,bitc为中间结果数据的位宽,即该缓存每个时钟周期最大可读写大小为m

×

m的相关结果矩阵块。每个存储体的深度大于相关结果矩阵面积的1/m2。

[0092][0093]

s8直至完成当前实时张量块对基准图张量一整行数据的扫描后结束。

[0094]

为了便于理解,此处举例以说明:

[0095]

若winograd算法是f(4

×

4,3

×

3),则每次输出的相关结果矩阵块的尺寸为4

×

4。

[0096]

s1基准图张量的尺寸为256

×

256

×

256,实时图张量的尺寸为128

×

128

×

256,则相关结果矩阵的尺寸为129

×

129。加速单元采用的通道并行度pn=32。

[0097]

s2从片外ddr向基准张量缓存的“乒区域”缓存大小为256

×6×

32的基准图张量块。如图4所示,基准张量缓存共有4

×

6个独立的存储体,每个存储体对应基准张量的一行,分为4组,每组对应图3中不同颜色标记的列的张量数据。

[0098]

s3从片外ddr向实时张量缓存写入大小为128

×3×

256的实时图张量块。并在经过一定之间的计算,该缓存中的部分数据重用完毕后,从ddr中加载新的数据覆盖之。

[0099]

s4如图4所示,在计算中读取基准图张量缓存“乒区域”数据的同时,将读出来的最后两行数据写入“乓区域”的前两行。于此同时,从ddr读取接下来的4行数据写入“乓区域”。该步骤需要cb×

3个时钟周期,与接下来的计算步骤同时进行。当“乒区域”的数据重用完毕后,利用同样的方式,向“乒区域”写入新的数据。如此这般,“乒乓区域”一直交错式的读写数据。

[0100]

s5当s2完成后,从第三组和第四组存储体读取大小为2

×6×

32的张量块,预写入基准张量寄存器组的前2列,对应图中绿色箭头标记的step0。

[0101]

s6在s5的同时,利用3个时钟周期,从实时图张量缓存向实时张量寄存器写入3

×3×

32大小的张量块。

[0102]

s7,如图4所示,当s6完成后,将基准张量寄存器组的前两列数据搬移到后两列,同时从基准张量缓存中读取4列数据到寄存器组的前4列。

[0103]

s8,将基准张量寄存器组和实时张量寄存器组中的数据经变换后分别写入v张量寄存器组和u张量寄存器组。将v张量寄存器组和u张量寄存器组中的数据对应逐点相乘后,写入e张量寄存器组。将e张量寄存器组中的数据经变换后写入s张量寄存器组。从过程张量缓存中读取中间结果数据至偏置张量寄存器组。如果是首次计算,缓存中无中间结果数据,则直接给寄存器组赋零。将s张量寄存器组中的数据沿通道方向累加后,与偏置寄存器组中的数据逐点相加,并写入过程张量寄存器组中。直至完成当前实时张量块对基准图张量一整行数据的扫描后结束。

[0104]

重复上述s5-s8,直至完成所有的相关计算。

[0105]

以上所述的具体实施方式,对本技术的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本技术的具体实施方式而已,并不用于限定本技术的保护范围,凡在本技术的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1