一种基于RFSOC模组的多通道AD同步采集电路的制作方法

一种基于rfsoc模组的多通道ad同步采集电路

技术领域

1.本实用新型涉及多通道数据采集技术领域,尤其涉及一种基于rfsoc模组的多通道ad同步采集电路。

背景技术:

2.传统的多通道ad采样实现基本都是通过fpga+外接adc芯片的形式实现的,这种方式设计复杂,需要同时对pcb和电源进行复杂设计,而且对时钟的设计要求也比较高,导致整体的设计开发成本高周期长,不利于雷达、通信以及dbf(数字波束合成)等领域的应用。

技术实现要素:

3.本实用新型的目的在于克服现有技术的缺点,提供一种基于rfsoc模组的多通道ad同步采集电路,解决了现有多通道ad采样方式存在的不足。

4.本实用新型的目的通过以下技术方案来实现:一种基于rfsoc模组的多通道ad同步采集电路,它包括rfsoc芯片和数据同步采集通道;所述数据同步采集通道包括单模块采集通道或者多模块采集通道;所述rfsoc芯片与所述单模块采集通道或者多模块采集通道连接;单模块采集通道自身产生采样时钟信号、同步信号和core时钟信号实现8路adc通道的同步采集,多模块采集通道接入外部输入的采样时钟信号、同步信号和core时钟信号实现8

×

n路adc通道的同步采集,n为大于1的正整数。

5.所述单模块采集通道包括时钟模块、缓冲器和巴伦转换器通过smp射频连接器将模拟信号输入到所述巴伦转换器转换为差分信号,提供给rfsoc进行ad采样,转换后的数据传输到axi总线提供给pl端处理;所述时钟模块输出adc需要的采样时钟信号、同步信号和core时钟信号,其中采样时钟信号输入到缓冲器分发后提供给rfsoc芯片内部的adc端口作采样时钟。

6.所述时钟模块包括温补晶体振荡器和时钟锁相环;所述温补晶体振荡器输出10mhz的温补晶振到所述时钟锁相环,所述时钟锁相环采用内部vco模式,输出adc需要的采样时钟以及同步信号,经过缓冲器分发后给8路adc采集通道提供采样时钟,以保证多路adc之间的同步采样。

7.所述多模块采集通道包括多个相同的采集通道单元,每个采集通道单元包括缓冲器和巴伦转换器;通过smp射频连接器输入外部提供同步的采样时钟信号、同步信号和core时钟信号,通过smp射频连接器将模拟信号输入到所述巴伦转换器转换为差分信号后提供给rfsoc芯片采样,其中采样时钟信号输入到缓冲,经过分发后提供给rfsoc芯片内部的adc端口作采样时钟;通过集成多个相同的采集通道单元,实现多模块多通道的同步采集。

8.还包括存储模块、网络接口模块和电源模块;所述存储模块和网络接口模块与所述rfsoc芯片相互连接,所述电源模块的供电输出端与所述rfsoc芯片连接。

9.所述存储模块包括ddr和flash,所述ddr和flash与所述rfsoc芯片相互连接。

10.本实用新型具有以下优点:一种基于rfsoc模组的多通道ad同步采集电路,降低了

开发周期、开发成本和开发复杂度,无需扩展adc芯片即可完成8通道高速adc采集和数据处理,同时支持多个模块多通道同步。设计简单、成本较低、极大的降低开发成本。在雷达、通信、dbf等应用中,有极强的竞争力。

附图说明

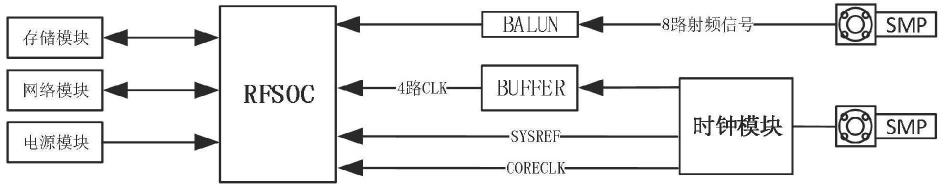

11.图1为本实用新型单模块采集通道时的整体原理结构示意图;

12.图2单模块采集通道的原理结构示意图;

13.图3为多模块采集通道的原理结构示意图。

具体实施方式

14.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。因此,以下结合附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的保护范围,而是仅仅表示本技术的选定实施例。基于本技术的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。下面结合附图对本实用新型做进一步的描述。

15.如图1所示,本实用新型具体涉及一种基于zynq ultrascal rfsoc的多模块多通道ad同步采集电路,以zynq ultrascal rfsoc为核心,实现8通道ad同步采集以及多模块多通道同步采集。最大采样率4gsps,时钟部分提供采样时钟和同步信号,数据采集转换后通过传输到rfsoc的axi总线供pl端进行处理。

16.它包括rfsoc芯片和数据同步采集通道;所述数据同步采集通道包括单模块采集通道或者多模块采集通道;所述rfsoc芯片与所述单模块采集通道或者多模块采集通道连接;单模块采集通道自身产生采样时钟信号、同步信号和core时钟信号实现8路adc通道的同步采集,多模块采集通道接入外部输入的采样时钟信号、同步信号和core时钟信号实现8

×

n路adc通道的同步采集,n为大于1的正整数。

17.进一步地,如图2所示,其中一种实施方式为单模块的同步采集模式,其中单模块采集通道包括时钟模块、缓冲器和巴伦转换器;通过smp射频连接器将模拟信号输入到所述巴伦转换器转换为差分信号后提供给rfsoc芯片采样;所述时钟模块输出adc需要的采样时钟信号、同步信号和core时钟信号,其中采样时钟信号输入到缓冲器,经过分发后提供给rfsoc作采样时钟。

18.其中,时钟模块包括温补晶体振荡器和时钟锁相环;所述温补晶体振荡器输出10mhz的温补晶振到所述时钟锁相环,所述时钟锁相环采用内部vco(压控振荡器)模式,输出adc需要的采样时钟以及同步信号,经过缓冲器分发后给8路adc采集通道提供采样时钟,以保证多路adc之间的同步采样。

19.进一步地,时钟pll(时钟锁相环)选用ti的lmk04828,板上参考10mhz温补晶振。采用内部vco模式,输出adc需要的采样时钟,以及同步信号sysref。8路adc需要4路采样时钟,lmk04828输出的时钟经过低延迟buffer(缓冲器)分发后提供给zynq ultrascal rfsoc芯

片作为采样时钟,保证多路adc之间的同步性。buffer典型延迟为1.5ps,保证多路adc的同步采样。

20.进一步地,如图3所示,另一种实施方式为采用多模块多通道的同步采集模式,其中多模块采集通道包括多个相同的采集通道单元,每个采集通道单元包括缓冲器和巴伦转换器;通过smp射频连接器输入外部提供同步的采样时钟信号、同步信号和core时钟信号,通过smp射频连接器将模拟信号输入到所述巴伦转换器转换为差分信号后提供给rfsoc采样,其中采样时钟信号输入到缓冲缓冲器,经过分发后提供给rfsoc作采样时钟;通过集成多个相同的采集通道单元,实现多模块多通道的同步采集。

21.其中,多模块多通道同步,需要外部提供同步的采样时钟、同步信号、core时钟。通过smp射频连接器输入,板上经过buffer分发后提供给adc,buffer典型延迟为1.5ps,可以完全保证多模块之间通道的同步性。

22.进一步地,还包括存储模块、网络接口模块和电源模块;所述存储模块和网络接口模块与所述rfsoc芯片相互连接,所述电源模块的供电输出端与所述rfsoc芯片连接。存储模块包括ddr和flash,所述ddr和flash与所述rfsoc芯片相互连接。进一步地,每路adc采集通道采用ac耦合(交流耦合)的设计,输入模拟信号经过balun(巴伦)转换为差分信号,输入到zynq ultrascal rfsoc进行ad采集。balun选用marki的bal-0006smg,该balun具有极好的幅频特性。

23.本实用新型可使用一片zynq ultrascal rfsoc芯片即可完成8通道高速adc采集和数据处理,同时支持多个模块多通道同步。设计简单、成本较低、极大的降低开发成本。在雷达、通信、dbf等应用中,有极强的竞争力。

24.以上所述仅是本实用新型的优选实施方式,应当理解本实用新型并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本实用新型的精神和范围,则都应在本实用新型所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1