一种串并转换器的制作方法

1.本实用新型属于集成电路技术领域,具体的说是涉及一种串并转换器。

背景技术:

2.通信模组是连通物联网不可或缺的桥梁。通信模组是将基带芯片、射频芯片、电源管理芯片、定位芯片、pn型器件及阻容感元器件等材料集成于pcb上的功能模块,以实现无线电波收发、信道噪声过滤及模拟信号与数字信号之间相互转换等功能。

3.通信模组是连通物联网不可或缺的桥梁。通信模组对不同芯片、器件进行再设计和集成,涉及多种通信协议/制式、体积、功耗与特殊工艺。无线通信模组是实现万物智联的关键设备,物联网终端通过无线通信模组接入网络以满足数据无线传输需求,是物联网感知层与网络层的重要连接枢纽。因此,数据传输是通信模组的核心技术。串并转换器是通信模组的核心部件,主要有串行输入并行输出和并行输入串行输出。串行数据传输是将组成数据和字符的码元按时序逐位予以传输,并行数据传输是将固定位数的数据和字符码元同时传输至接收端,串并转换器是完成这两种传输方式之间转换的装置。

4.通信模组内接口数量少,如图1所示,在模组内将串并转换器芯片配合化合物数控时延器芯片等,可以实现高精度、高速度传输功能。

技术实现要素:

5.为了解决了通信模组内输入接口数量不足的问题,本实用新型提出一种串并转换器。

6.本实用新型的技术方案为:

7.一种串并转换器,包括第一寄存器、第二寄存器、第三寄存器、第四寄存器、二选一开关、第一单端转差分电路、第二单端转差分电路;所述第一寄存器和第二寄存器的时钟信号端接第一外部时钟信号,第一寄存器和第二寄存器的片选信号端接外部片选信号,第一寄存器的数据输入端接外部串行数据,第二寄存器的数据输入端接第一寄存器的数据输出端,在外部片选信号为低时,外部串行数据输入第一寄存器,同时第一外部时钟信号输入第一寄存器和第二寄存器;第二寄存器接收第一寄存器的串行数据,第二寄存器的输出端输出串行数据;所述第三寄存器为第一寄存器的二级存储器,第三寄存器的数据输入端接第一寄存器的数据输出端,第四寄存器为第二寄存器的二级存储器,第四寄存器的数据输入端接第二寄存器的数据输出端;第三寄存器和第四寄存器的时钟信号输入端接第二外部时钟信号;第二外部时钟信号在第一外时钟信号的最后一个时钟到来后,产生脉冲将输入的串行数据通过第一寄存器和第二寄存器分别存入到第三寄存器和第四寄存器;第三寄存器和第四寄存器的数据输出端连接到二选一开关,所述二选一开关用于在外部控制信号作用下选择性输出第三寄存器和第四寄存器的数据到第二单端转差分电路,所述第二单端转差分电路用于将串行数据转为并行数据输出,具体为当外部控制信号为高电平时,二选一开关将第四寄存器的数据输出到第二单端转差分电路,第二单端转差分电路将第四寄存器的

串行数据转为并行数据输出,当外部控制信号为低电平时,二选一开关将第三寄存器的数据输出到第二单端转差分电路,第二单端转差分电路将第三寄存器的串行数据转为并行数据输出;同时外部控制信号经过第一单端转差分电路转化为差分信号输出。

8.本实用新型的有益效果是:本实用新型提出一种高集成、高精度的串并转换驱动器芯片,既能实现足够的接口数量,又能满足数据传输速度的要求,具有更高的集成度、更小的体积、更高的精度。

附图说明

9.图1为通信模组内部逻辑结构示意图。

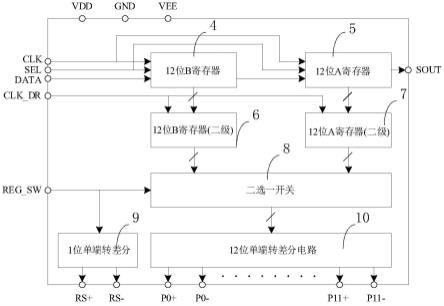

10.图2为本实用新型的逻辑结构示意图。

具体实施方式

11.下面结合附图对本实用新型进行详细描述。

12.如图2所示,本实用新型的串并转换驱动器,包括二选一开关模块8、a数据寄存器模块5、b数据寄存器模块4、a数据寄存器(二级)模块7、b数据寄存器(二级)模块6、1位的单端转差分电路9和12位的单端转差分电路10;

13.所述b数据寄存器模块4用于接收存放串行输入数据data信号,该信号为正压信号,并将串行输入信号按照先进先出原则进行传输。

14.所述a数据寄存器模块5用于接收存放b数据寄存器模块4传输的信号,并从sout串行输出到后级芯片。

15.所述b数据寄存器(二级)模块6用于接收存放b数据寄存器模块4传输的数据,并在clk_dr信号的作用下,将b二级寄存器的数据刷新到并行输出端口。

16.所述a数据寄存器(二级)模块7用于接收存放a数据寄存器模块5传输的数据,并在clk_dr信号的作用下,将a二级寄存器7的数据刷新到并行输出端口。

17.所述二选一开关模块8用于接收a数据寄存器(二级)模块7与b数据寄存器(二级)模块6传输的数据,并在reg_sw信号的作用下将a/b二级数据寄存器的数据二选一,并刷新到并行输出端口。

18.单端转差分输出级模块9、10用于将reg_sw信号与二选一开关模块8信号单端转差分输出。

19.具体的,串行数据data为正压信号,按照先进先出原则,依次经过b数据寄存器模块4和a数据寄存器模块5,然后从sout串行输出到后级数控时延器芯片。

20.具体的,clk_dr信号可将a/b二级数据寄存器的数据刷新到并行输出端口p《11:0》+和p《11:0》-,12对并行差分输出信号为负压。

21.具体的,reg_sw信号可将a/b二级寄存器数据二选一,并刷新到并行输出端口p《11:0》+和p《11:0》-,同时通过单端转双端电路输出rs+和rs-差分信号,信号为负压信号。

22.具体的,时钟信号clk和串行输入数据data均为ttl电平,sel为片选信号。当sel为低时,时钟信号clk和串行输入数据data可以进入芯片内部;sel为高时,时钟clk和串行数据输入data被封锁在芯片之外。24位输入数据data全部输入完成后,再经过24个周期使sout输出24个串行数据后,sel为高电平。

23.具体的,时钟信号clk_dr为ttl脉冲,在最后一个时钟clk到来后,产生一个脉冲,将24位串行数据存入分别存入a数据寄存器(二级)模块和b数据寄存器(二级)模块中,a数据寄存器(二级)模块和b数据寄存器(二级)模块中的数据通过二选一开关模块的控制互补输出。

24.具体的,控制信号reg_sw为ttl电平,当reg_sw为高电平时,a数据寄存器(二级)中的数据经过12位单独转差分电路输出;当reg_sw为低电平时,b数据寄存器(二级)中的数据经过12位单独转差分电路输出。reg_sw经过1位单端转差分电路互补输出rs+和rs-。

技术特征:

1.一种串并转换器,其特征在于,包括第一寄存器、第二寄存器、第三寄存器、第四寄存器、二选一开关、第一单端转差分电路、第二单端转差分电路;所述第一寄存器和第二寄存器的时钟信号端接第一外部时钟信号,第一寄存器和第二寄存器的片选信号端接外部片选信号,第一寄存器的数据输入端接外部串行数据,第二寄存器的数据输入端接第一寄存器的数据输出端,在外部片选信号为低时,外部串行数据输入第一寄存器,同时第一外部时钟信号输入第一寄存器和第二寄存器;第二寄存器接收第一寄存器的串行数据,第二寄存器的输出端输出串行数据;所述第三寄存器为第一寄存器的二级存储器,第三寄存器的数据输入端接第一寄存器的数据输出端,第四寄存器为第二寄存器的二级存储器,第四寄存器的数据输入端接第二寄存器的数据输出端;第三寄存器和第四寄存器的时钟信号输入端接第二外部时钟信号;第二外部时钟信号在第一外时钟信号的最后一个时钟到来后,产生脉冲将输入的串行数据通过第一寄存器和第二寄存器分别存入到第三寄存器和第四寄存器;第三寄存器和第四寄存器的数据输出端连接到二选一开关,所述二选一开关用于在外部控制信号作用下选择性输出第三寄存器和第四寄存器的数据到第二单端转差分电路,所述第二单端转差分电路用于将串行数据转为并行数据输出,具体为当外部控制信号为高电平时,二选一开关将第四寄存器的数据输出到第二单端转差分电路,第二单端转差分电路将第四寄存器的串行数据转为并行数据输出,当外部控制信号为低电平时,二选一开关将第三寄存器的数据输出到第二单端转差分电路,第二单端转差分电路将第三寄存器的串行数据转为并行数据输出;同时外部控制信号经过第一单端转差分电路转化为差分信号输出。

技术总结

本实用新型属于集成电路技术领域,具体的说是涉及一种串并转换器。本实用新型包括包括第一寄存器、第二寄存器、第三寄存器、第四寄存器、二选一开关、并行输出端口、单端转双端电路,主要通过多个寄存器存储外部的串行信号,并且在控制下将存储的串行信号转为并行输出,同时输出控制信号的差分信号。本实用新型提出一种高集成、高精度的串并转换驱动器芯片,既能实现足够的接口数量,又能满足数据传输速度的要求,具有更高的集成度、更小的体积、更高的精度。精度。精度。

技术研发人员:李俊美 龙飞 王洪全 张殿亮

受保护的技术使用者:成都华兴大地科技有限公司

技术研发日:2022.05.11

技术公布日:2022/8/26

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1