神经形态存储器电路和人工神经网络的神经发生的方法与流程

本公开总体上涉及神经形态存储器电路和训练人工神经网络的方法。

背景技术:

1、人工神经网络在各种领域和应用中被用于执行各种任务,如字符识别、图像分类、自然语言处理以及各种模式匹配和分类任务。人工神经网络包含输入层、至少一个隐藏层和输出层,每个层都具有一群神经元或节点。一层中的神经元的输出连接到下一层中的神经元的输入,并且“权重”与神经元之间的每个连接相关联。为了计算每个神经元的激活状态,对神经元的输入执行加权和(即,将一组输入信号乘以一组权重,然后求和),然后利用传递函数将加权输入的线性组合转换为阈值激活函数(f(s))。

技术实现思路

1、本公开涉及存储器电路的各种实施例,所述存储器电路被配置为执行乘法累加(mac)操作以执行人工神经网络。在一个实施例中,所述存储器电路包含:布置成交叉条阵列的一系列单元,所述一系列单元中的每个单元包含与忆阻器串联连接的存储器晶体管;连接到每个单元中的所述存储器晶体管的源极端子的一系列输入线(位线);连接到每个单元中的所述忆阻器的输出端子的一系列输出线(板线);以及耦接到每个单元中的所述存储器晶体管的栅极端子的一系列编程线(字线)。每个单元的所述忆阻器被配置为存储电导值,所述电导值表示连接到所述人工神经网络中的神经元的突触的突触权重。每个单元的所述存储器晶体管被配置为存储阈值电压,所述阈值电压表示连接到所述人工神经网络中的所述神经元的所述突触的突触重要性值。对于所述一系列单元中的每个单元,所述忆阻器的所述电导值和所述存储器晶体管的所述阈值电压是可独立编程的。

2、所述一系列单元中的每个单元中的所述忆阻器可以是电阻式随机存取存储器(reram)元件、相变存储器(pcm)元件、铁电隧道结(ftj)元件或自旋转移力矩存储器(stt-ram)元件。

3、所述一系列单元中的每个单元中的所述存储器晶体管可以是铁电场效应晶体管(fefet)或电荷俘获晶体管(ctt)。

4、所述存储器电路还可以包含耦接到所述一系列字线的字线驱动器、耦接到所述一系列输入线的位线驱动器以及耦接到所述一系列输出线的输出驱动器。

5、所述存储器电路还可以包含耦接到所述交叉条阵列的电流感测元件。所述电流感测元件可以包含采样保持放大器或跨阻抗放大器。

6、所述存储器电路可以包含耦接到所述电流感测元件的多路复用器和耦接到所述多路复用器的多路复用器控制器。

7、所述存储器电路还可以包含耦接到所述多路复用器的一系列模数转换器。

8、所述存储器电路可以包含耦接到所述一系列模数转换器的一系列加法器和一系列移位寄存器。这些外围电路由cmos制成。

9、本公开还涉及对存储器电路进行编程的方法的各种实施例。在一个实施例中,所述方法包含:在第一任务上训练人工神经网络期间改变一系列单元中的至少一个单元中的忆阻器的表示突触权重的电导值;用与所述存储器电路分离的电路确定用于执行所述第一任务的所述人工神经网络的至少一个重要突触;改变所述一系列单元中的至少一个单元中的存储器晶体管的表示突触重要性值的阈值电压,所述至少一个单元对应于用于执行所述第一任务的所述人工神经网络的所述至少一个重要突触。

10、改变所述阈值电压可以包含跨所述至少一个单元中的所述存储器晶体管的栅极端子和源极端子施加编程脉冲,同时保持输入线和输出线处于相同电压(不施加电压或施加相同电压),以避免存储在忆阻器元件中的所述突触权重的任何变化。在fefet的实施例中,其阈值电压可以通过使用所述编程脉冲方法改变铁电栅极介电层的剩余极化来调节。铁电材料的剩余极化的这种变化是非易失性的,并且在去除所述编程脉冲之后被存储。

11、所述方法可以包含在不同于所述第一任务的第二任务上训练所述人工神经网络期间改变所述一系列单元中的至少一个单元的所述忆阻器的表示所述突触权重的所述电导值。改变所选择的忆阻器元件的所述突触权重可以包含跨所述所选择的忆阻器元件的所述输入线(与所述忆阻器串联的所述存储器晶体管的所述源极端子)和所述输出线施加编程脉冲。将超阈值电压施加到所述存储器晶体管的所述栅极端子,使得其被切换到具有小源极-漏极电阻的“导通”状态,以允许跨所述所选择的忆阻器元件施加所述编程脉冲。

12、至少一个单元的所述存储器晶体管的所述阈值电压被配置为在所述第二任务上训练所述人工神经网络期间防止所述至少一个单元的所述权重值的变化,以防止所述神经网络表现出灾难性遗忘。在一个实施例中,使用n沟道fefet(n-fefet)作为所述存储器晶体管。将其阈值电压向更正值移位将减小在相同源极-漏极和源极-栅极偏置条件下的源极-漏极电流。更高的突触重要性对应于更正的阈值电压,这使得fefet在第二任务中的训练期间不太可能转变为“导通”状态,从而保护串联连接的所述忆阻器元件的电导(突触权重)不被改变。

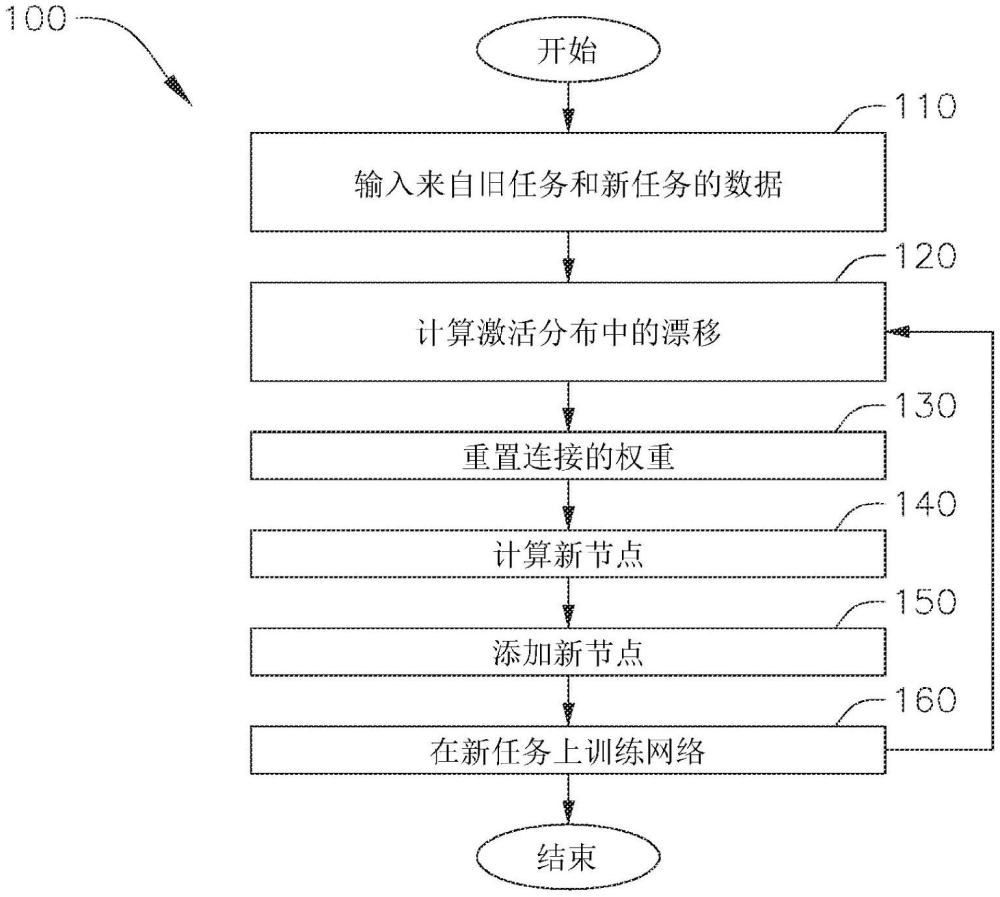

13、可以将交叉条存储器电路与cmos电路系统共同集成在同一cmos处理核心内或者异质集成到预制cmos处理核心上。

14、确定所述人工神经网络的重要突触可以包含:利用对比激励反向传播算法标识用于所述第一任务的所有层内的重要神经元;以及利用学习算法、基于所标识的重要神经元来标识用于所述第一任务的多个神经元之间的重要突触。

15、用于标识重要突触的所述学习算法可以是如下的hebbian学习算法:其中是突触重要性参数,xn是输入图像,是所述人工神经网络的第l层中的第j个神经元,是所述人工神经网络的第l+1层中的第i个神经元,并且p是概率。

16、用于标识重要突触的所述学习算法可以是如下的oja学习规则:其中i和j是神经元,l是所述人工神经网络的层,pc是概率,是第l-1层中的第j个神经元与第l层中的第i个神经元之间的突触对所述第一任务的重要性,∈是oja学习规则的速率,并且pc是概率。

17、本公开还涉及执行人工神经网络的神经发生的方法的各种实施例,所述人工神经网络包含多个(或一群)层和所述一群层中的每一层中的多个(或一群)神经元。在一个实施例中,所述方法包含:确定所述人工神经网络的一系列备用神经元;评估所述人工神经网络在新任务或上下文中的性能;响应于所述人工神经网络的所述性能停滞或下降而确定要添加到所述人工神经网络的所述一系列备用神经元中的附加神经元的数量和位置;用所述附加突触将所述附加神经元连接到所述人工神经网络;在所述新任务或上下文上训练具有所述附加神经元和所述附加突触的所述人工神经网络,以确定所述附加突触的权重和突触重要性值;以及将所述备用神经元的所述权重和所述突触重要性值存储在存储器电路中。

18、确定所述备用神经元可以包含:在第一任务或上下文上训练所述人工神经网络以确定连接多个神经元的突触的权重;确定所述突触的突触重要性值;以及确定连接到所述一系列神经元中的至少一个神经元的每个突触的所述突触重要性值低于突触重要性阈值。

19、所述突触重要性阈值可以根据以下等式来确定:γi<平均值(γi)-3标准偏差(γi),其中γi是连接到所述人工神经网络的层i中的多个神经元的突触的突触重要性。

20、确定所述备用神经元可以包含主动地将所述备用神经元设置为不活动的。

21、确定所述附加神经元的所述数量和所述位置可以利用在与所述存储器电路分离的商用现货(cots)芯片上执行的概率程序神经发生(ppn)算法。

22、提供此

技术实现要素:

而引入下文在具体实施方式中进一步描述的本公开的实施例的特征和概念的选择。此发明内容并不旨在标识所要求保护的主题的关键或基本特征,也不旨在用来限制所要求保护的主题的范围。所描述的特征中的一个或多个特征可以与所描述的一个或多个其它特征组合,以提供可行的装置或方法。

- 还没有人留言评论。精彩留言会获得点赞!