一种生成码流文件的方法、装置、计算机存储介质及终端与流程

本文涉及但不限于现场可编程门阵列技术,尤指一种生成码流文件的方法、装置、计算机存储介质及终端。

背景技术:

1、现场可编程门阵列(fpga,field programmable gate array)软件开发工具是专为fpga芯片而配套的集成电路设计与实现工具。一般地,fpga软件开发覆盖了从寄存器传输级(rtl,register transfer level)电路功能描述到生成fpga码流文件的完整流程,生成fpga码流文件的处理涉及逻辑综合、布局和布线等环节。

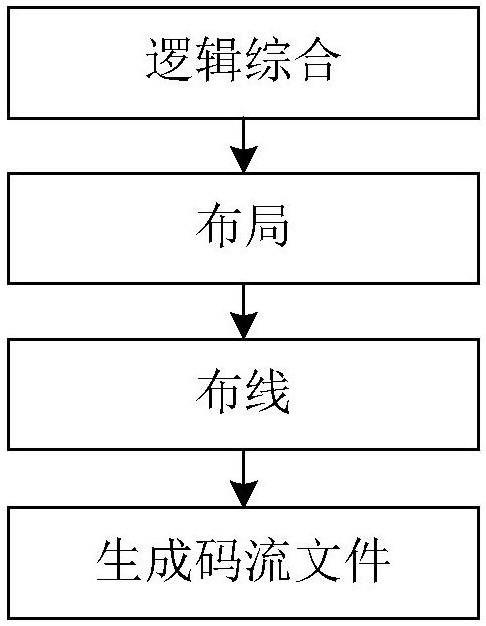

2、图1为相关技术中生成码流文件的处理流程示意图,如图1所示,包括:对整个用户设计整体进行逻辑综合,生成一个网表文件;对网表文件中所有使用到的逻辑资源进行布局;待网表文件中所有的逻辑资源布局完成后,对所有的含有布局信息的逻辑资源之间的连接关系进行布线。上述处理过程中,逻辑综合、布局和布线以用户设计中的所有模块的信息作为输入进行处理,针对的整个用户设计的整体,设计中的各个模块的逻辑综合、布局和布线的处理时资源分配未做限定,导致整体资源分配可能出现不合理的问题,无法满足用户设计需求。

技术实现思路

1、以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本发明实施例提供一种生成码流文件的方法、装置、计算机存储介质及终端,能够提高fpga中包含的模块的逻辑资源分配的合理性,提高芯片的设计质量和设计效率。

3、本发明实施例提供了一种生成码流文件的方法,包括:

4、对现场可编程门阵列fpga中的模块,根据数据在模块中的时序要求的数值确定模块的先后排序;

5、根据确定的模块的先后排序,逐个进行模块的逻辑综合、布局和布线处理;

6、所有模块的逻辑综合、布局和布线处理均完成后,执行生成码流文件的处理。

7、在一种示例性实例中,所述根据数据在模块中的时序要求的数值确定模块的先后排序,包括:

8、根据所述数据在模块中的时序要求的数值确定所述模块的时序权重值,其中,所述时序权重值的大小与所述时序要求的数值大小成反比;

9、按照确定的所述时序权重值由大到小的顺序,确定所述模块的所述先后排序。

10、在一种示例性实例中,所述模块的所述时序权重值等于所述数据在模块中的时序要求的数值的倒数。

11、在一种示例性实例中,所述逐个进行模块的逻辑综合、布局和布线处理包括,对未进行所述逻辑综合、布局和布线处理的排序在最先前的模块,执行以下处理:

12、生成所述模块的网表文件;

13、对生成所述网表文件的模块,根据生成的所述网表文件和可用的布局资源对所述模块进行布局处理;

14、对完成布局处理的所述模块,根据可用的布线资源进行布线处理;

15、其中,所述可用的布局资源包括:未被其他模块使用的布局资源;所述可用的布线资源包括:未被其他模块使用的布线资源。

16、另一方面,本发明实施例还提供一种计算机存储介质,所述计算机存储介质中存储有计算机程序,所述计算机程序被处理器执行时实现上述生成码流文件的方法。

17、再一方面,本发明实施例还提供一种终端,包括:存储器和处理器,所述存储器中保存有计算机程序;其中,

18、处理器被配置为执行存储器中的计算机程序;

19、所述计算机程序被所述处理器执行时实现如上述生成码流文件的方法。

20、还一方面,本发明实施例还提供一种生成码流文件的装置,包括:排序模块、处理模块和码流生成模块;其中,

21、排序模块设置为:对现场可编程门阵列fpga中的模块,根据数据在模块中的时序要求的数值大小确定模块的先后排序;

22、处理模块设置为:根据确定的模块的先后排序,逐个进行模块的逻辑综合、布局和布线处理;

23、码流生成模块设置为:所有模块的逻辑综合、布局和布线处理均完成后,执行生成码流文件的处理。

24、在一种示例性实例中,所述排序模块是设置为:

25、根据所述数据在模块中的时序要求的数值确定所述模块的时序权重值,其中,所述时序权重值的大小与所述时序要求的数值大小成反比;

26、按照确定的所述时序权重值由大到小的顺序,确定所述模块的所述先后排序。

27、在一种示例性实例中,所述模块的所述时序权重值等于所述数据在模块中的时序要求的数值的倒数。

28、在一种示例性实例中,所述处理模块是设置为,对未进行所述逻辑综合、布局和布线处理的排序在最先前的模块,执行以下处理:

29、生成所述模块的网表文件;

30、对生成所述网表文件的模块,根据生成的所述网表文件和可用的布局资源对所述模块进行布局处理;

31、对完成布局处理的所述模块,根据可用的布线资源进行布线处理;

32、其中,所述可用的布局资源包括:未被其他模块使用的布局资源;所述可用的布线资源包括:未被其他模块使用的布线资源。

33、本申请技术方案包括:对现场可编程门阵列(fpga)中的模块,根据数据在模块中的时序要求的数值确定模块的先后排序;根据确定的模块的先后排序,逐个进行模块的逻辑综合、布局和布线处理;所有模块的逻辑综合、布局和布线处理均完成后,执行生成码流文件的处理。本发明实施例根据时序要求的数值大小分析模块的时序权重值,以模块为处理单元,依据各模块时序权重值确定fpga中包含的模块的先后顺序,基于确定的先后顺序对各个模块分别进行逻辑综合、布局和布线处理;提高了逻辑资源分配的合理性,保证了关键的时序模块对逻辑资源使用的优先级,提高了芯片的设计质量和设计效率。

34、本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

技术特征:

1.一种生成码流文件的方法,包括:

2.根据权利要求1所述的方法,其特征在于,所述根据数据在模块中的时序要求的数值确定模块的先后排序,包括:

3.根据权利要求2所述的方法,其特征在于,所述模块的所述时序权重值等于所述数据在模块中的时序要求的数值的倒数。

4.根据权利要求1-3任一项所述的方法,其特征在于,所述逐个进行模块的逻辑综合、布局和布线处理包括,对未进行所述逻辑综合、布局和布线处理的排序在最先前的模块,执行以下处理:

5.一种计算机存储介质,所述计算机存储介质中存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求1-4中任一项所述的生成码流文件的方法。

6.一种终端,包括:存储器和处理器,所述存储器中保存有计算机程序;其中,

7.一种生成码流文件的装置,包括:排序模块、处理模块和码流生成模块;其中,

8.根据权利要求7所述的装置,其特征在于,所述排序模块是设置为:

9.根据权利要求8所述的装置,其特征在于,所述模块的所述时序权重值等于所述数据在模块中的时序要求的数值的倒数。

10.根据权利要求7-9任一项所述的装置,其特征在于,所述处理模块是设置为,对未进行所述逻辑综合、布局和布线处理的排序在最先前的模块,执行以下处理:

技术总结

本文公开一种生成码流文件的方法、装置、计算机存储介质及终端,包括:对现场可编程门阵列(FPGA)中的模块,根据数据在模块中的时序要求的数值确定模块的先后排序;根据确定的模块的先后排序,逐个进行模块的逻辑综合、布局和布线处理;所有模块的逻辑综合、布局和布线处理均完成后,执行生成码流文件的处理。本发明实施例根据时序要求的数值分析模块的时序权重值,以模块为处理单元,依据各模块时序权重值确定FPGA中包含的模块的先后顺序,基于确定的先后顺序对各个模块分别进行逻辑综合、布局和布线处理;提高了逻辑资源分配的合理性,保证了关键的时序模块对逻辑资源使用的优先级,提高了芯片的设计质量和设计效率。

技术研发人员:魏山菊,王兴刚,闵祥伟,李海波,王铜铜,范召,宋国民

受保护的技术使用者:山东高云半导体科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!