图像统计特征提取的FPGA处理架构、方法及装置

本发明涉计算机视觉领域,更为具体的,涉及一种图像统计特征提取的fpga处理架构、方法及装置。

背景技术:

1、随着社会发展和科学进步,计算机视觉在社会发展中发挥越来越重要的作用,已广泛应用于交通监控、工业生产、航空航天、车辆导航、视频处理以及人机交互等领域。随着目前探测器需求越来越高,制作工艺以及分辨率也随之提升,大量复杂的视觉信息数据,为计算机进行信息处理和分析提供充足的样本,同时,也给计算机实时处理带来了严峻的挑战。

2、行人检测的任务是通过计算机视觉技术判断视频或图像中是否存在行人并对行人的位置进行标注,是计算机视觉领域中一个既具有研究价值同时又极具挑战性的热门课题。

3、从1990年代中期开始就有许多学者对人体检测技术进行了研究。到2002年,有研究人员借鉴和引进了图像处理和模式识别方面的一些成熟方法,重点是行人的现有特征和简单的分类算法。自2005年以来,行人检测技术的训练库趋于大规模化,检测精度趋于实用化,检测速度趋于实时化。随着大学、研究机构和汽车制造商的研究不断深入,行人检测技术也得到了快速发展。

4、在实际应用中,行人检测方法已广泛应用于机器人、汽车系统、安全系统、移动设备和可穿戴电子设备等平台。然而,由于各种条件的限制,例如平台的计算能力、电池容量以及片上存储资源等限制,在许多情况下,用于便携式电子设备或机器人平台的典型低功耗处理器没有足够的计算能力来实现复杂的机器学习应用程序,以满足实时要求。由于行人兼具刚性和柔性物体的特性,外观易受穿着、尺度、遮挡、姿态和视角等影响,在资源以及算力等条件限制下,行人检测方法可以实时高精度运行已成为实际应用中最具挑战性的问题。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种图像统计特征提取的fpga处理架构、方法及装置,减少了运算量,降低了存储资源消耗,实现了硬件加速,且实时性好。

2、本发明的目的是通过以下方案实现的:

3、一种图像统计特征提取的fpga处理架构,包括:

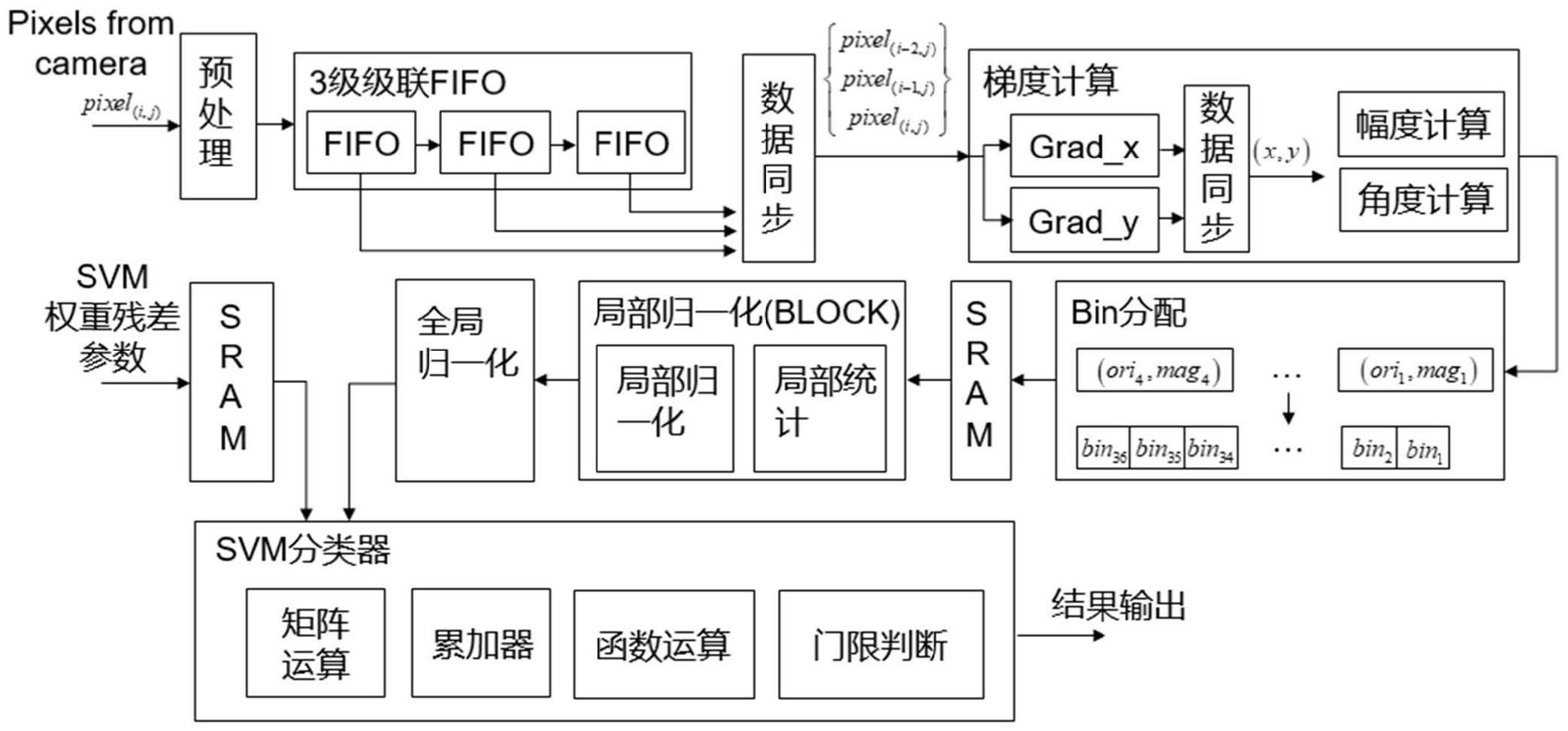

4、预处理模块、级联fifo模块、数据同步模块、梯度计算模块、仓位分配模块、sram模块、局部归一化模块、全局归一化模块和svm分类器模块;

5、对输入的数据通过预处理模块进行预处理,经预处理后的图像数据进入级联fifo模块的缓存空间,再并行输入梯度计算模块,利用梯度计算模块计算图像横坐标和纵坐标方向的梯度,并据此计算每个像素位置的梯度的幅值大小以及方向;将得到的梯度计算结果,利用仓位分配模块分配至对应的仓位中,然后利用局部归一化模块进行局部归一化并缓存;待整个窗口中的数据计算完成后利用全局归一化模块进行全局归一化;最终得到的特征向量输入svm分类器模块。

6、进一步地,所述svm分类器模块中的权重参数以及残差参数均由上位机提前训练完成后,通过离线的方式存储在片上的rom资源中。

7、进一步地,还包括仓位缓冲单元,仓位分配单元输出为串行的仓位结果,仓位缓冲单元将输出的串行的仓位结果进行串转并,再将数据拼接,同时缓冲多行向量数据,实现多通道并行输出;在单个单元的时钟周期内完成包含该单元的所有运算,设计多通道并行的向量输出,经过输入多行单元向量的延迟后,每处理完一行数据,输出以该行数据为最末行的整个窗口数据。

8、进一步地,所述局部归一化模块为块统计归一化单元,所述块统计归一化单元输入为多通道单元统计特征和有效信号,输出为归一化后的窗口hog特征向量及有效信号;当块统计归一化单元开始进入处理状态时,每当计算出一个单元特征向量时,在块统计归一化单元输入为该单元所处窗口的列方向上的多通道的有效单元特征向量,每两个通道单元构成单个块中列方向上的两个单元子集,多通道输入单元即实现同时输出窗口列方向上的多个块特征向量数据。

9、一种基于图像统计特征提取的fpga处理架构的运行方法,该方法基于如上任一项所述的图像统计特征提取的fpga处理架构,运行以下步骤:

10、s1,对图像使用查找表的方式来进行gamma校正;

11、s2,在梯度计算单元计算图像的梯度;

12、s3,通过拆分将像素方向计算和仓位分配合并,从而在不需要计算反三角函数的情况下得到像素仓位;具体包括如下步骤:仓位分配设计为9个仓位,共180°,每个仓位的范围是20°,当y方向梯度和x方向梯度计算得到的像素角度处在第i个仓位的范围内时,将该像素分入仓位i中;当输入x和y方向上的梯度时,将x方向上的梯度与各tan(θ)相乘,θ为每个仓位间的边界值;此处乘法调用dsp资源进行加速处理,然后将输入的y方向上的梯度与乘法器输出的结果进行比较,输出对应结果,以3bit数据0至8分别代表9个仓位,得到梯度方向及大小后同样做数据同步对齐操作,将结果传入仓位分配单元;仓位分配单元输入为像素方向即梯度,有效信号和帧有效信号,输出为统计后的单元特征向量和有效信号;在上一单元梯度计算中,像素的方向计算得到的结果即为该像素的对应仓位号,在本单元中对像素所处的单元进行统计,将一个单元的梯度和方向进行统计,生成直方图;仓位分配单元输入为像素的梯度以及方向,输出为一个单元的特征统计向量;将梯度和方向数据拼接,梯度位宽为8位,方向位宽位4位,拼接组成12位的向量,通过级联fifo模块缓冲进行存储,其中向量缓存控制机制采用状态机控制,一共有10个状态;系统上电时处于idle状态待机,当数据进入仓位分配单元后,开始数据缓存,第二至第八个状态都为缓存状态,其分别控制七个fifo模块进行读写操作,当输入数据的第九行开始,状态机收到更新指令,进行单元直方图统计,之后每八行输出一次统计结果并进行寄存器清零操作,反复至处理完整幅图像,状态机回到idle状态等待下一次数据输入;

13、s4,采用基于单元的滑动窗口机并行处理单元格中所有相关重叠滑动窗口的分类;

14、s5,计算滑动窗口的乘法-累积运算,并将其存储在内存中,以便处理下一个单元,继续进行部分分类计算;

15、s6,svm分类单元输入为hog特征向量,输出为分类结果及置信度。

16、进一步地,在步骤s1中,所述对图像使用查找表的方式来进行gamma校正,包括子步骤:对各灰度像素值进行gamma校正,将所有校正后的值以离线的方式存入fpga的分布式rom资源中,将校正前的像素值作为地址一一对应校正后的值;当灰度数据输入时,从rom中读出对应校正后的值。

17、一种基于图像统计特征提取的fpga处理架构的运行方法,该方法基于如上任一项所述的图像统计特征提取的fpga处理架构,所述svm分类器模块运行如下步骤:

18、首先,确认输入的特征向量数,初始化标签,初始化分类个数以及权重参数;将特征向量与具体的支持向量进行点乘;得到的结果存入kvalue寄存器,在两层循环中进行调用;

19、然后,根据设定分类个数判断循环次数,调用线性核,此处为单层循环,将支持向量的系数根据每一类支持向量的个数分组,分别与kvalue寄存器对应位相乘,并进行累加,累加后的结果减去偏置量rho得到两个分别属于两个分类的置信度,然后通过sigmoid函数进行两两类别,得到属于这两两类别的概率值;

20、最后,通过比较函数确定概率最大的分类进行输出。

21、进一步地,所述svm分类器模块还运行矩阵运算以及向量运算步骤:

22、首先,对于矩阵运算以及向量运算部分,在上位机计算模型参数时,对参数进行后处理,将支持向量以及支持向量的系数取绝对值,并单独存储符号位信息,将支持向量的稀疏矩阵与支持向量的系数进行点成,生成新的稀疏矩阵fcoef,将矩阵在行方向上进行累加最终得到参数向量,将该参数向量生成coe文件,离线存入fpga的rom中,以供运算时调用svm权重参数;

23、然后,在运算优化后,先将输入的特征信息暂存在寄存器中,采用状态机控制数据读写计算,共包含五个状态:待机状态idle、等待状态wait、数据读取状态data-get、数据等待状态data-wait以及数据计算状态data-cac;上电时进入待机状态,对全局寄存器及各单元进行初始化操作,然后进入等待状态;当外部缓冲完成一行块信息缓冲后,输出完成标识信号,状态机跳转至数据读取状态,读入一组数据后进入数据等待状态;10个时钟周期后开始计算,根据标识符每个时钟周期每个通道取出4个特征信息进行计算,9个时钟周期后完成单个块信息的分类计算,将结果输入累加器单元,状态机跳回等待状态,按此循环计算;

24、最后,基于八通道并行解算,经过四次循环累加后,处理完整个窗口,累加器输出结果并清零;当下一块特征向量输入时,窗口滑动一个块的步长,进行新一轮预测。

25、一种基于图像统计特征提取的fpga处理架构的运行方法,该方法基于如上任一项所述的图像统计特征提取的fpga处理架构,运行如下步骤:

26、图像统计特征在进入svm分类单元前进行行缓存操作,当缓存完一行块信息时,输出完成标识信号进行分类计算;当完成标识信号拉高时,从外部缓存中读出特征时进行降采样处理,并行输入svm分类单元进行解算,从而实现对大目标进行目标检测。

27、一种基于图像统计特征提取的fpga处理架构的装置,包括如上任一项所述的图像统计特征提取的fpga处理架构。

28、本发明的有益效果包括:

29、本发明对hog特征提取方法提出了轻量化设计方案,在保持精度的条件下减少运算量;并在fpga硬件平台基于fpga平台高度并行以及流水线设计的特性,通过面向存储结构的优化设计来避免整幅图像存储等问题,降低了存储资源消耗;以及对复杂数学运算进行了优化设计,避免了重复运算,优化了复杂运算流程,实现了硬件加速;同时本发明提出的通用架构适用于大部分应用场景,实现实时性的高精度通用算法硬件架构设计。

- 还没有人留言评论。精彩留言会获得点赞!