PCIE链路信号测试方法、系统、终端及存储介质与流程

本发明属于服务器,具体涉及一种pcie链路信号测试方法、系统、终端及存储介质。

背景技术:

1、随着计算机技术的不断发展,在众多决定系统性能稳定的因素里,高速互联现象正起着主导作用,常常导致一些不可预见问题的出现,极大的增加了系统设计的复杂性。因此在高速链路设计验证中,要统筹考虑各个模块的相互影响,通过测试和评估手段评估高速信号链路稳定性,提高整系统设计成功率,减少故障发生。在服务器系统pcie链路测试过程中,发送端信号一致性测试是一项必测项,通过测试治具将主板pcie信号引出至示波器,示波器对抓取到的信号进行分析,并生成测试报告。如果测试项都能测试pass,则代表被测信号链路的完整性较好,可以进行产品的下一阶段,反之则主要优化。但是信号在测试过程中受到多种因素影响,比如各板卡的互连接触稳定性,测试环境等。因此,pcie信号测试的可信度极大影响评估结论,如果测试的可信度不高,甚至会导致产品设计失败,极大增加风险。

2、针对pcie链路的测试通常分为发送端信号一致性测试、接收端误码率测试,通常的测试会规定在适当环境下测试,比如环境温度、湿度,避免不同外界环境对测试结果的影响;同时,测试者需要使用业内标准治具板,标准的示波器线缆及互连方法,保证板卡的互连接触稳定性;此外,还需要使用业内标准测试项和分析软件,保证测试项的覆盖度以及分析过程一致性。

3、虽然上述要求能够基本保证主板设计的一致性,但当系统与pcie设备卡互联时,仍有可能由于各类设备的能力不同,导致整个链路通信异常。比如针对配置丰富的服务器系统,在信号测试时通常只会关注主板待测信号拓扑,而忽略主板与设备卡互联时的影响。如果在信号测试时不考虑设备卡的影响,就意味着没有找到这条链路的最完整情况,那么在整机运行过程中可能会出现各类问题。

技术实现思路

1、针对现有技术的上述不足,本发明提供一种pcie链路信号测试方法、系统、终端及存储介质,以解决上述技术问题。

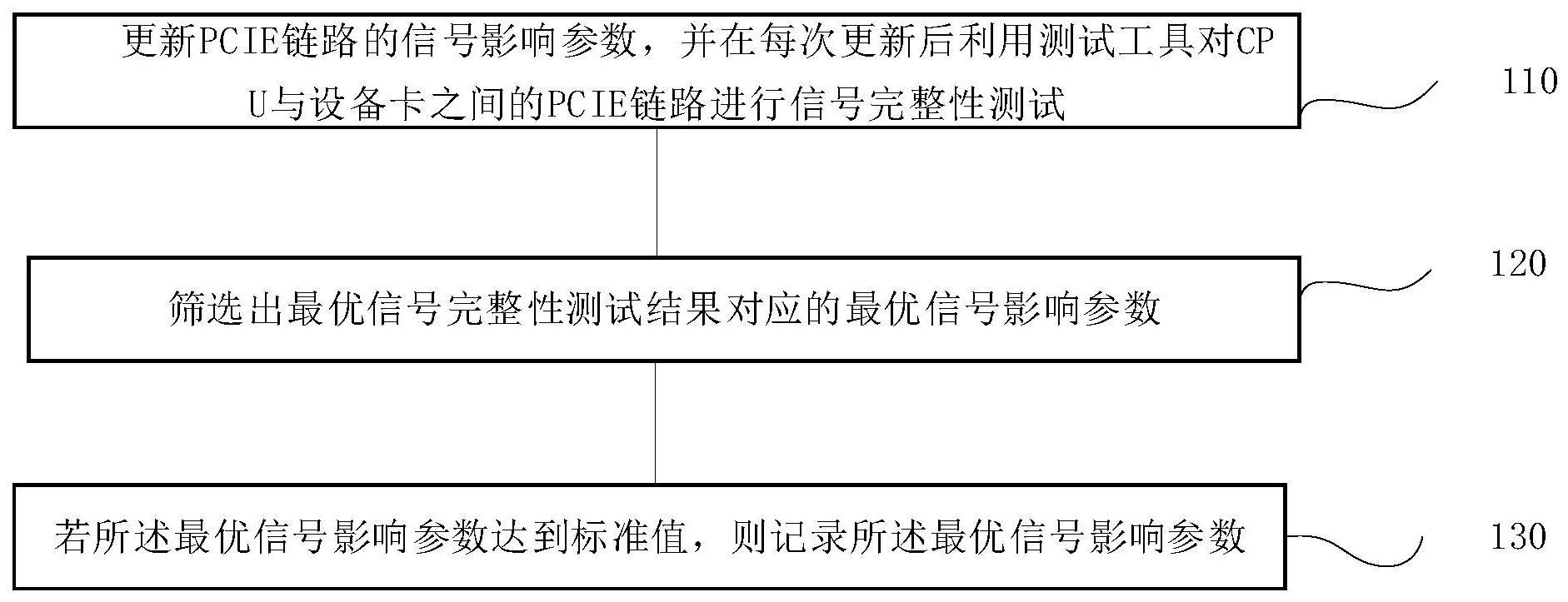

2、第一方面,本发明提供一种pcie链路信号测试方法,包括:

3、更新pcie链路的信号影响参数,并在每次更新后利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试;

4、筛选出最优信号完整性测试结果对应的最优信号影响参数;

5、若所述最优信号影响参数达到标准值,则记录所述最优信号影响参数。

6、在一个可选的实施方式中,在更新pcie链路的信号影响参数,并在每次更新后利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试之前,所述方法还包括:

7、在pcie链路的信号影响参数为默认值时,利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试;

8、基于pcie信号完整性测试的标准值设置风险裕量;

9、判断信号完整性测试的测试结果与标准值的差值是否达到风险裕量:

10、若是,则判定当前pcie链路通过信号完整性测试;

11、若否,则判定对所述pcie链路执行信号影响参数更新以及相应的信号完整性测试。

12、在一个可选的实施方式中,在pcie链路的信号影响参数为默认值时,利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试,包括:

13、pcie链路的发射端在链路训练阶段协商得到预设参数值的默认最优值,所述预设参数值为信号影响参数中的一项参数值;

14、基于cpu规格选取匹配的测试工具;

15、利用测试工具对链路训练完成后的pcie链路在多种测试场景下进行信号完整性测试。

16、在一个可选的实施方式中,更新pcie链路的信号影响参数,并在每次更新后利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试,包括:

17、解析信号影响参数的取值范围;

18、基于所述取值范围在更新pcie链路的信号影响参数时遍历所有信号影响参数值。

19、在一个可选的实施方式中,解析信号影响参数的取值范围,包括:

20、若信号影响参数的取值为连续变量,则设定调整步距,基于所述调整步距和取值范围生成每次更新所需的信号影响参数值;

21、若信号影响参数的取值为多个数值,则生成包含多个所述数值的集合,并从所述集合选取信号影响参数的更新取值。

22、在一个可选的实施方式中,筛选出最优信号完整性测试结果对应的最优信号影响参数,包括:

23、记录各组信号影响参数下得到的信号完整性测试结果;

24、筛选出达到标准值的信号完整性测试结果,并从中筛选出最优信号完整性测试结果,所述信号完整性测试结果包括信号眼宽;

25、若不存在达到标准值的信号完整性测试结果,则判定所述pcie链路的信号测试失败。

26、在一个可选的实施方式中,若所述最优信号影响参数达到标准值,则记录所述最优信号影响参数,包括:

27、将最优信号影响参数和pcie链路基本信息写入基本输入输出系统,以供基本输入输出系统在调整具有相同基本信息的pcie链路的信号影响参数值时调用所述最优信号影响参数,所述pcie链路基本信息包括pcie链路号和设备卡属性信息。

28、第二方面,本发明提供一种pcie链路信号测试系统,包括:

29、参数更新模块,用于更新pcie链路的信号影响参数,并在每次更新后利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试;

30、结果筛选模块,用于筛选出最优信号完整性测试结果对应的最优信号影响参数;

31、参数记录模块,用于若所述最优信号影响参数达到标准值,则记录所述最优信号影响参数。

32、在一个可选的实施方式中,所述系统还包括:

33、默认测试模块,用于在pcie链路的信号影响参数为默认值时,利用测试工具对cpu与设备卡之间的pcie链路进行信号完整性测试;

34、裕量设置模块,用于基于pcie信号完整性测试的标准值设置风险裕量;

35、风险判断模块,用于判断信号完整性测试的测试结果与标准值的差值是否达到风险裕量;

36、测试终止模块,用于若信号完整性测试的测试结果与标准值的差值达到风险裕量,则判定当前pcie链路通过信号完整性测试;

37、测试执行模块,用于若信号完整性测试的测试结果与标准值的差值未达到风险裕量,则判定对所述pcie链路执行信号影响参数更新以及相应的信号完整性测试。

38、在一个可选的实施方式中,所述默认测试模块包括:

39、参数协商单元,用于pcie链路的发射端在链路训练阶段协商得到预设参数值的默认最优值,所述预设参数值为信号影响参数中的一项参数值;

40、工件匹配单元,用于基于cpu规格选取匹配的测试工具;

41、场景执行单元,用于利用测试工具对链路训练完成后的pcie链路在多种测试场景下进行信号完整性测试。

42、在一个可选的实施方式中,参数更新模块包括:

43、参数解析单元,用于解析信号影响参数的取值范围;

44、参数遍历单元,用于基于所述取值范围在更新pcie链路的信号影响参数时遍历所有信号影响参数值。

45、在一个可选的实施方式中,参数解析单元包括:

46、第一解析子单元,用于若信号影响参数的取值为连续变量,则设定调整步距,基于所述调整步距和取值范围生成每次更新所需的信号影响参数值;

47、第二解析子单元,用于若信号影响参数的取值为多个数值,则生成包含多个所述数值的集合,并从所述集合选取信号影响参数的更新取值。

48、在一个可选的实施方式中,结果筛选模块包括:

49、测试记录单元,用于记录各组信号影响参数下得到的信号完整性测试结果;

50、结果筛选单元,用于筛选出达到标准值的信号完整性测试结果,并从中筛选出最优信号完整性测试结果,所述信号完整性测试结果包括信号眼宽;

51、失败判定单元,用于若不存在达到标准值的信号完整性测试结果,则判定所述pcie链路的信号测试失败。

52、在一个可选的实施方式中,参数记录模块包括:

53、参数记录单元,用于将最优信号影响参数和pcie链路基本信息写入基本输入输出系统,以供基本输入输出系统在调整具有相同基本信息的pcie链路的信号影响参数值时调用所述最优信号影响参数,所述pcie链路基本信息包括pcie链路号和设备卡属性信息。

54、第三方面,提供一种终端,包括:

55、处理器、存储器,其中,

56、该存储器用于存储计算机程序,

57、该处理器用于从存储器中调用并运行该计算机程序,使得终端执行上述的终端的方法。

58、第四方面,提供了一种计算机存储介质,所述计算机可读存储介质中存储有指令,当其在计算机上运行时,使得计算机执行上述各方面所述的方法。

59、本发明的有益效果在于,本发明提供的pcie链路信号测试方法、系统、终端及存储介质,通过对接入设备卡的pcie链路在不同信号影响参数取值下进行信号完整性测试,考虑到了对pcie信号测试时需要cpu与设备通信时的影响,并通过调整信号影响参数提高pcie链路测试结果的可信度,提升了产品验证质量,避免整机产品出厂后运行出现故障。

60、此外,本发明设计原理可靠,结构简单,具有非常广泛的应用前景。

- 还没有人留言评论。精彩留言会获得点赞!