一种用于进行双线性插值处理的运算装置的制作方法

本公开涉及数据处理领域,尤其涉及一种用于进行双线性插值处理的运算装置。

背景技术:

1、双线性插值是有两个变量的插值函数的线性插值扩展,其原理是在两个方向分别进行一次线性插值。双线性插值作为数值分析中的一种插值算法,广泛应用在信号处理,数字图像和视频处理等技术领域。

技术实现思路

1、有鉴于此,本公开提出了一种用于进行双线性插值处理的运算装置的技术方案。

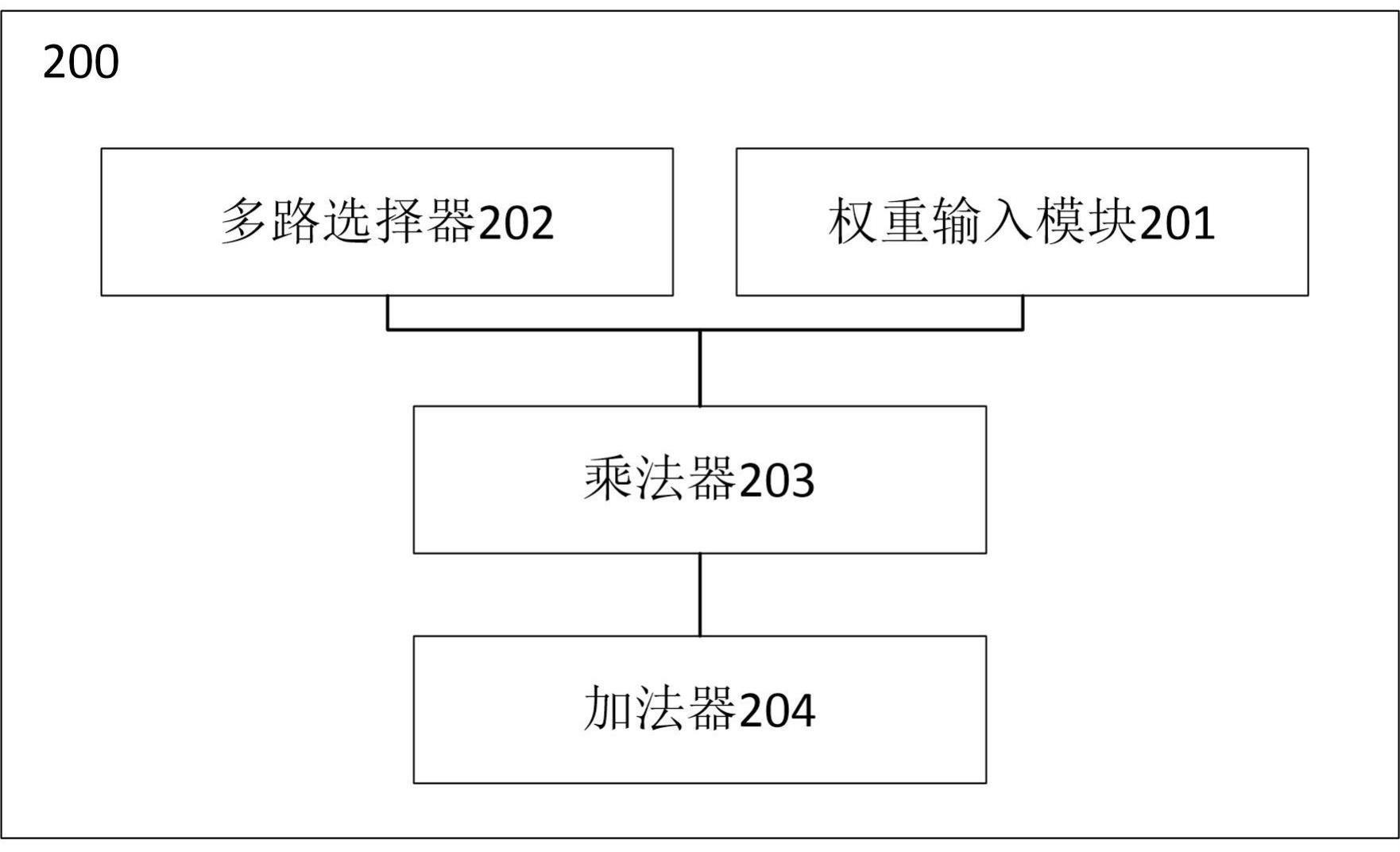

2、根据本公开的一方面,提供了一种用于进行双线性插值处理的运算装置,包括:权重输入模块、多路选择器、多个乘法器和加法器,其中,所述乘法器的输入位宽为m-1 bit;所述权重输入模块,用于利用第一低位数据u和第二低位数据v,确定各个所述乘法器分别对应的权重输入数据,并将所述权重输入数据输入对应的所述乘法器,其中,所述第一低位数据u为第一插值权重u的低位m-1 bit,所述第二低位数据v为第二插值权重v的低位m-1bit,所述第一插值权重u和所述第二插值权重v为m bit,并大于等于0且小于等于1, m为所述第一插值权重u与所述第二插值权重v对应的二进制数的位数;所述多路选择器,用于根据所述第一插值权重u和所述第二插值权重v,分别确定至少一个所述乘法器对应的待运算数据,并将所述待运算数据输入相应的所述乘法器,其中,每个所述乘法器对应的所述待运算数据为需要进行所述双线性插值处理的多个待插值数据中的一个;所述乘法器,用于根据所述待运算数据和所述权重输入数据,进行对应的乘法运算,确定乘法运算结果;所述加法器,用于对各个所述乘法器对应的所述乘法运算结果进行求和运算,确定所述多个待插值数据对应的双线性插值处理结果。

3、在一种可能的实现方式中,所述多个乘法器包括:第一乘法器、第二乘法器、第三乘法器和第四乘法器,所述权重输入数据包括:第一权重输入数据、第二权重输入数据、第三权重输入数据和第四权重输入数据;所述权重输入模块输入所述第一乘法器的所述第一权重输入数据为1-u和1-v;所述权重输入模块输入所述第二乘法器的所述第二权重输入数据为u和1-v;所述权重输入模块输入所述第三乘法器的所述第三权重输入数据为1-u和v;所述权重输入模块输入所述第四乘法器的所述第四权重输入数据为u和v。

4、在一种可能的实现方式中,所述多路选择器,用于根据所述第一插值权重u和所述第二插值权重v的最高位,确定所述第一低位数据u相对于所述第一插值权重u的取值变化,以及所述第二低位数据v相对于所述第二插值权重v的取值变化;所述多路选择器,用于根据所述第一低位数据u相对于所述第一插值权重u的取值变化、所述第二低位数据v相对于所述第二插值权重v的取值变化、以及所述多个待插值数据,确定至少一个所述乘法器对应的所述待运算数据,其中,所述多个待插值数据包括:第一待插值数据、第二待插值数据、第三待插值数据和第四待插值数据。

5、在一种可能的实现方式中,所述多路选择器,用于在所述第一插值权重u和所述第二插值权重v的最高位均为0时,确定所述第一低位数据u的取值相对于所述第一插值权重u的取值不变,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值不变。

6、在一种可能的实现方式中,所述多路选择器,用于在所述第一低位数据u的取值相对于所述第一插值权重u的取值不变,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值不变时,确定所述第一乘法器对应的所述待运算数据为所述第一待插值数据,所述第二乘法器对应的所述待运算数据为所述第二待插值数据,所述第三乘法器对应的所述待运算数据为所述第三待插值数据。

7、在一种可能的实现方式中,所述多路选择器,用于在所述第一插值权重u的最高位为1,所述第二插值权重v的最高位为0时,确定所述第一低位数据u的取值相对于所述第一插值权重u的取值发生变化,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值不变。

8、在一种可能的实现方式中,所述多路选择器,用于在所述第一低位数据u的取值相对于所述第一插值权重u的取值发生变化,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值不变时,确定所述第一乘法器对应的所述待运算数据为所述第二待插值数据,所述第三乘法器对应的所述待运算数据为所述第四待插值数据。

9、在一种可能的实现方式中,所述多路选择器,用于在所述第一插值权重u的最高位为0,所述第二插值权重v的最高位为1时,确定所述第一低位数据u的取值相对于所述第一插值权重u的取值不变,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值发生变化。

10、在一种可能的实现方式中,所述多路选择器,用于在所述第一低位数据u的取值相对于所述第一插值权重u的取值不变,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值发生变化时,确定所述第一乘法器对应的所述待运算数据为所述第三待插值数据,所述第二乘法器对应的所述待运算数据为所述第四待插值数据。

11、在一种可能的实现方式中,所述多路选择器,用于在所述第一插值权重u和所述第二插值权重v的最高位均为1时,确定所述第一低位数据u的取值相对于所述第一插值权重u的取值发生变化,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值发生变化。

12、在一种可能的实现方式中,所述多路选择器,用于在所述第一低位数据u的取值相对于所述第一插值权重u的取值发生变化,以及所述第二低位数据v的取值相对于所述第二插值权重v的取值发生变化时,确定所述第一乘法器对应的所述待运算数据为所述第四待插值数据。

13、在一种可能的实现方式中,所述多个待插值数据是目标图像中需要进行双线性插值处理的2×2结构的四个像素数据。

14、本公开实施例的用于进行双线性插值处理的运算装置,通过权重输入模块,利用第一低位数据u和第二低位数据v,确定各个乘法器分别对应的权重输入数据,并将权重输入数据输入对应的乘法器,其中,第一低位数据u为第一插值权重u的低位m-1 bit,第二低位数据v为第二插值权重v的低位m-1 bit,第一插值权重u和第二插值权重v为m bit,并大于等于0且小于等于1;根据m-1 bit的第一低位数据u和第二低位数据v确定的权重输入数据,其位数也为m-1 bit,从而可以将乘法器的输入位宽从m bit减小为m-1 bit。利用多路选择器,可以根据第一插值权重u和第二插值权重v的取值,分别确定至少一个乘法器对应的待运算数据,其中,每个乘法器对应的待运算数据为需要进行双线性插值处理的多个待插值数据中的一个,将待运算数据输入相应的乘法器,从而可以调整乘法器对应的乘法运算结果,进而保证双线性插值处理结果的准确性。通过乘法器,可以根据待运算数据和权重输入数据,进行对应的乘法运算,确定乘法运算结果,再通过加法器,可以对各个乘法器对应的乘法运算结果进行求和运算,确定双线性插值处理结果。通过减小乘法器的输入位宽,并通过多路选择器调整待插值数据输入乘法器的逻辑,可以减少装置整体的电路面积,节约进行双线性插值处理的硬件资源消耗。

15、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

- 还没有人留言评论。精彩留言会获得点赞!