降低芯片开关功耗的布局布线方法与流程

本发明涉及芯片低功耗设计,具体涉及降低芯片开关功耗的布局布线方法。

背景技术:

1、随现代化发展进程,节能已成为全球关注问题。同时人们对可移动产品的需求也日趋变高,市场对产品的续航能力有更大的要求。另外越大的功耗,意味着系统产生的热量越大,相应的散热元件成本也会增加,封装上也需要采用更加昂贵的材料或者冷却系统、面对以上问题,低功耗将是电子工业的发展趋势,已成为衡量芯片好坏的标准之一。

2、从设计的进程来看,当需要开发低功耗芯片时,先由设计前端进行芯片构架的优化,比如低电压、低频、多电源电压设计等,逻辑电路方面常采用的是clock gating的方法(关断部分时钟)。仅限于前端芯片构架的改进是不足够的,实际上往往不能达到理想的效果,因为在设计中后端物理实现的过程中也存在着很多影响功耗的因素。比如,连接逻辑器件的金属线的宽度和长度,以及该金属线所处的物理环境等等,都可能直接影响该逻辑器件的负载寄生进而影响器件功耗。

技术实现思路

1、本发明所要解决的技术问题是仅从芯片构架上进行低功耗设计存在局限性,而在芯片的中后端设计(物理实现)过程中存在着很多影响功耗的因素,比如连接逻辑器件的金属线的宽度和长度,以及该金属线所处物理环境等,会直接影响该逻辑器件的负载寄生进而影响器件功耗。

2、本发明目的在于提供降低芯片开关功耗的布局布线方法,在对芯片进行物理实现设计中期,对逻辑电路进行分析得出高功耗发生可能的金属互连线,在实际物理版图设计中对该部分金属互连线进行优化控制,降低信号线上的寄生,减小器件的负载从而达到降低开关功耗的目的,对整体功耗能达到5%到10%的降低,在一些超低功耗要求的产品中,仅使用常规芯片低功耗设计方法无法达到设计要求时,可采用本发明方法进行进一步的功耗改善。

3、本发明通过下述技术方案实现:

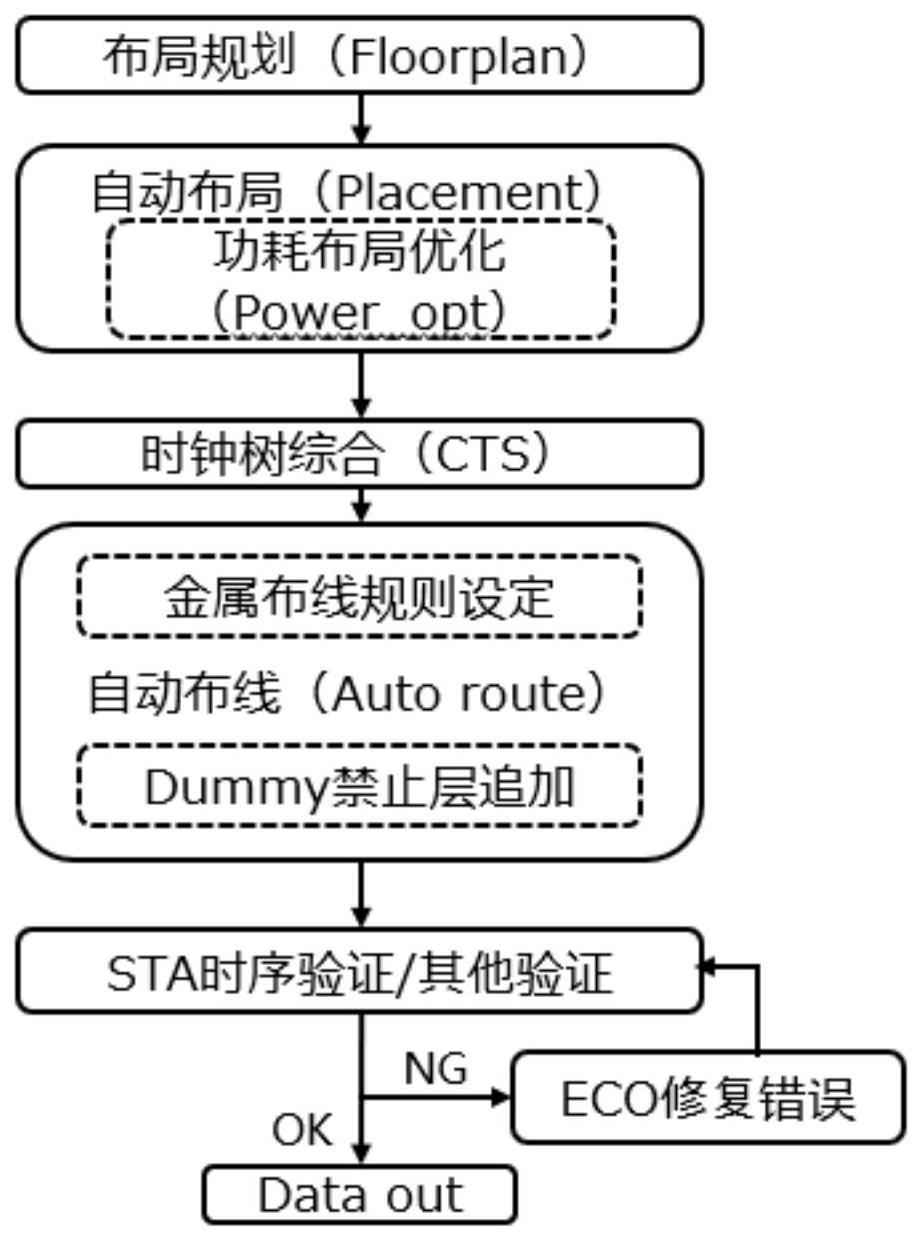

4、本发明提供了降低芯片开关功耗的布局布线方法,该方法包括:

5、获取芯片常规自动布局后的数据;

6、采用基于时序偏移量的功耗布局优化法,对芯片常规自动布局后的数据进行功耗布局优化,得到优化功耗后的布局数据;

7、根据优化功耗后的布局数据进行时钟树综合,得到时钟树综合后的数据;

8、根据时钟树综合后的数据,结合金属布线规则,使用金属线与金属通孔进行逻辑器件之间的物理连接,从而完成芯片设计中后端的自动布线。

9、进一步地,采用基于时序偏移量的功耗布局优化法,对芯片常规自动布局后的数据进行功耗布局优化,得到优化功耗后的布局数据,包括:

10、对芯片常规自动布局后的数据进行文件导出,得到当前寄生报告、当前电路和时序报告;

11、对当前电路进行逻辑仿真,查看逻辑仿真的波形,并确认当前电路的逻辑是否正确;同时导出当前电路中信号翻转情况作为第一电路翻转报告;

12、根据第一电路翻转报告和时序报告,进行相应报告解析,得到时序偏移量;

13、根据时序偏移量,采用时序路径约束法设置新约束条件;其中,时序路径约束法即path_margin的约束方式,是一种现有约束方法。

14、根据新约束条件进行二次自动布局,得到优化功耗后的布局数据。

15、进一步地,还包括:

16、从优化功耗后的布局数据中导出对应的时序报告和寄生报告,根据对应的时序报告和寄生报告进行判断获得判断结果;

17、当判断结果为高频信号寄生与最初的寄生相比较未减小(ng),则调整新约束条件,重新进行功耗布局优化;

18、当判断结果为时序违反,则调整新约束条件,重新进行功耗布局优化;

19、当判断结果为高频信号寄生减小,且满足时序要求的布局数据,则布局功耗优化结束。

20、进一步地,当前寄生报告用于记载每条逻辑连线当前寄生情况;

21、当前电路用于记载前逻辑网表;

22、时序报告用于记载当前每条逻辑连线时序情况。

23、进一步地,第一电路翻转报告包括仿真区间、逻辑状态为0的持续时间、逻辑状态为1的持续时间、信号翻转的总次数、不定态x的时间和竞争冒险次数;

24、其中,信号翻转的总次数包括信号从0翻转到1的次数和信号从1翻转到0的次数;

25、竞争冒险次数是不计入信号翻转的总次数中。

26、进一步地,根据第一电路翻转报告和时序报告,进行相应报告解析,得到时序偏移量,包括:

27、采用第一电路翻转报告给每条逻辑连线标记上翻转频率,通过翻转频率的不同进行第一次筛选,选出具备优化场景的逻辑电路及待进行功耗布局优化的对象器件;

28、判断对象器件中的低频信号的第一时序是否存在余量、判断对象器件中的高频信号的第二时序是否存在余量;

29、选取第一时序和第二时序中时最小的时序余量作为时序偏移量。

30、进一步地,第一时序是建立时间时序,当低频信号延迟增大太多会违反建立时间,判断公式为:t+skew-data>setup,t为时钟周期,skew为时钟偏移量,data为数据延迟,setup为建立时间;

31、第二时序是保持时间时序,当高频信号延迟降低太多将违反保持时间,判断公式为:data-skew>hold,data为数据延迟,skew为时钟偏移量,hold为保持时间。

32、进一步地,根据时钟树综合后的数据,结合金属布线规则,使用金属线与金属通孔进行逻辑器件之间的物理连接,从完成芯片设计中后端的自动布线,包括:

33、根据时钟树综合后的数据,导出时钟树综合后的当前电路;

34、对时钟树综合后的当前电路进行逻辑仿真,查看逻辑仿真的波形,并确认时钟树综合后的当前电路的逻辑是否正确;同时导出时钟树综合后的当前电路中信号翻转情况作为第二电路翻转报告;

35、根据第二电路翻转报告计算线宽;根据第二电路翻转报告记载的翻转频率,计算线与线之间的间距及使用金属层次;

36、根据线宽、线与线之间的间距及使用金属层次,设置布线规则;

37、根据布线规则,采用工具运行自动布线,得到布线完成后的数据;

38、并根据布线完成后的数据,对大间距金属线追加金属填充物禁止层,禁止金属填充物插入金属线两侧;防止因为dummy介质插入后增大寄生恶化开关功耗。

39、进一步地,根据第二电路翻转报告计算线宽,包括:

40、将第二电路翻转报告带入实际版图中,并采用eda工具仿真出每条信号线的功耗,根据功耗换算出每条信号线的电流;根据电流,再结合生产商提供的em对照表,计算出满足em对照表要求的最小的线宽;

41、根据第二电路翻转报告记载的翻转频率,计算线与线之间的间距,包括:

42、根据第二电路翻转报告记载的信号线的翻转频率,得出最高翻转频率的实际值,并将相同翻转频率的信号线全部提取出,该提取出的信号因为翻转快功耗大为降低其寄生负载往往需要设置两倍默认间距。

43、进一步地,该方法还包括:

44、对完成自动布线的数据进行sta时序验证和/或其他验证,如果没有通过各项验证,则通过eco进行修复直至各项验证通过。

45、本发明与现有技术相比,具有如下的优点和有益效果:

46、1、本发明降低芯片开关功耗的布局布线方法,在对芯片进行物理实现设计中期,对逻辑电路进行分析得出高功耗发生可能的金属互连线,在实际物理版图设计中对该部分金属互连线进行优化控制,降低信号线上的寄生,减小器件的负载从而达到降低开关功耗的目的;本发明通过上述方法可降低发生在信号布线金属上的开关功耗20%,对芯片的整体功耗能降低5%到10%。

47、2、本发明降低芯片开关功耗的布局布线方法,(1)自动布局阶段,结合第一电路翻转报告中信号翻转频率,对芯片常规设计得布局结果进行2次优化,将高翻转频率的金属布线长度进行减短,降低线上寄生电容改善开关功耗;(2)自动布线阶段,结合第二电路翻转报告更加精准仿真出每条信号的电流大小,根据电流大小对相应信号线进行高精准度的线宽设置,减小布线宽度设置过大的而增加负载带来的开关功耗;(3)对大间距金属连线追加dummy禁止层,禁止dummy插入信号两侧,防止因为dummy介质插入后增大寄生恶化开关功耗。

- 还没有人留言评论。精彩留言会获得点赞!