一种自适应时钟电路、乘法运算电路及乘法运算的方法

本发明涉及数据处理,尤其涉及的是一种自适应时钟电路、乘法运算电路及乘法运算的方法。

背景技术:

1、乘法运算是高性能处理器以及深度学习加速器中使用最频繁的运算之一,乘法器单元的设计很大程度决定了整个电路系统的性能以及面积与功耗开销。一般的浮点数乘法的思路可以概括为:两符号位异或,指数位相加,尾数位相乘。posit乘法的算法思路与浮点数乘法基本一致,但是需要增加额外的解码模块去表示指数部分,posit乘法系统通过增加额外的解码模块可以消耗更少的存储空间和更小的传输带宽去完成高精度算法。

2、为了权衡posit乘法器解码带来的额外硬件开销,目前关于posit乘法器硬件电路优化策略的研究主要有两项先进研究,一是利用posit非均匀精度的特性来支持实时多精度需求的运算,此技术通过只实现一个支持动态识别不同精度的硬件,来替代多精度运算应用中为每个精度单独设计的多套硬件,大大减少了同应用下的面积功耗开销,但是代价却是牺牲了并行计算的速度,只适用于对性能要求不高而对面积和功耗有严格约束的场景。

3、二是利用posit动态位宽的特性,实时根据动态位宽去禁用当前有效的数据通路,来达到减少功耗的目的(因为对于不同的posit数值,权重位和尾数位的位宽是在动态变化的,而在硬件电路设计中,必须为可能出现的最大位宽去设计硬件以满足任何场景下的需求,这导致在实际运行过程中并不是所有数据通路都是有效的。)此方法虽减小了功耗开销,但仍然没有突破posit乘法器运算速度慢的瓶颈。

4、因此,现有技术还有待于改进和发展。

技术实现思路

1、鉴于上述现有技术的不足,本发明的目的在于提供一种基于自适应时钟的乘法运算电路,以解决现有技术中乘法器不能同时解决面积以及功耗大且运算速度慢的问题。

2、本发明的技术方案如下:

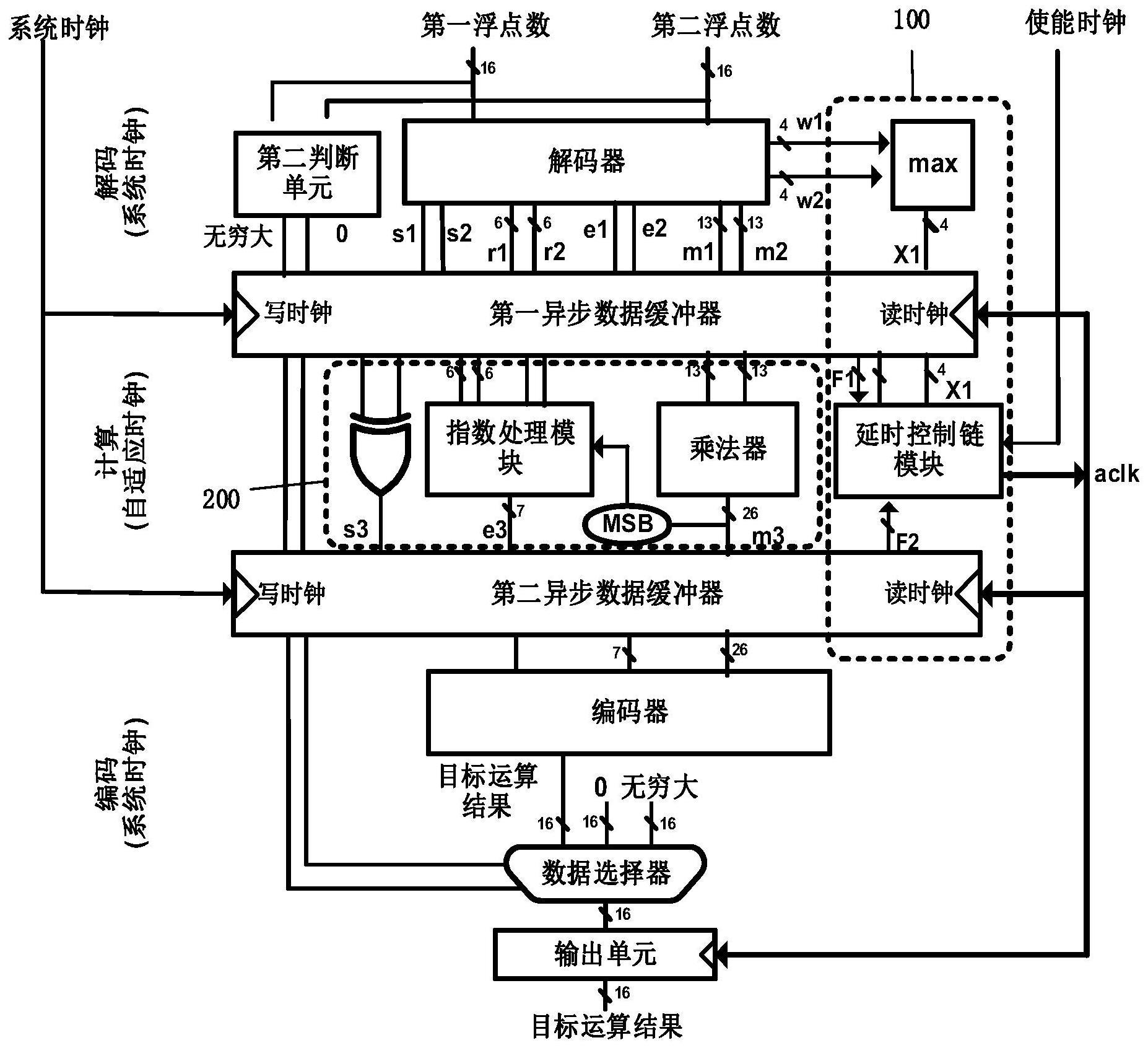

3、一种自适应时钟电路,包括:捕获单元、异步数据缓冲器以及延时控制链模块;

4、所述捕获单元用于比较第一尾数位以及第二尾数位的位宽,并获取两者之中的最大位宽,所述第一尾数位以及所述第二尾数位为浮点数经过解码后的小数;

5、所述延时控制链模块用于根据最大位宽匹配所述异步数据缓冲器的延时时钟;

6、所述异步数据缓冲器用于根据延时时钟传输数据。

7、本发明的进一步设置,所述延时控制链模块包括:

8、第一判断单元,用于根据最大位宽输出控制信号;

9、延时链,用于产生不同时钟频率;

10、第一数据选择器,用于根据控制信号确定延时时钟。

11、本发明的进一步设置,所述延时链包括若干个原语门,所述原语门包括与门以及若干个反相器;

12、首个所述原语门中所述与门的第一输入端连接所述第一数据选择器的输出端,首个所述原语门中所述与门的第二输入端接入使能时钟;

13、所述与门的输出端连接所述原语门中的首个所述反相器的输入端;

14、所述原语门中尾部的所述反相器的输出端连接次个所述原语门中所述与门的第一输入端;

15、次个所述原语门中所述与门的第二输入端连接所述第一判断单元的输出端。

16、一种乘法运算电路,包括:解码器、运算模块、编码器以及如上所述的自适应时钟电路;

17、所述解码器用于将两个浮点数进行解码,得到解码后的第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位以及第二尾数位;

18、所述运算模块根据第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位以及第二尾数位进行运算得到两个浮点数相乘后的目标符号位、目标指数数值以及目标尾数位;

19、所述编码器用于根据目标符号位、目标指数数值以及目标尾数位得到目标运算结果;

20、所述自适应时钟电路用于比较第一尾数位以及第二尾数位的位宽,并获取两者之中的最大位宽,同时根据最大位宽匹配对应的延时时钟,以改变获取流动数据的速度;其中,所述流动数据包括第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位、第二尾数位、目标符号位、目标指数数值以及目标尾数位。

21、本发明的进一步设置,所述乘法运算电路还包括:第二判断单元以及第二数据选择器;

22、所述第二判断单元用于判断两个浮点数中的任一浮点数是否为特殊值,如果两位浮点数中的任一浮点数为特殊值时,则将特殊值输入第二数据选择器;

23、所述第二数据选择器用于在接收到特殊值时,输出特殊值,否则,输出目标运算结果。

24、本发明的进一步设置,所述第二数据选择器为三选一多路选择器。

25、本发明的进一步设置,所述特殊值为无穷大或零。

26、本发明的进一步设置,所述运算模块包括:异或门,用于将第一符号位以及第二符号位进行异或得到目标符号位;

27、乘法器,用于将第一尾数位以及第二尾数位进行相乘得到目标尾数位;

28、最高有效位单元,用于确定所述目标尾数位的最高位,并将目标尾数位的最高位输出至指数处理模块;

29、指数处理模块,用于将第一权重位、第二权重位、第一指数偏置位、第二偏置位以及目标尾数位的最高位进行处理得到目标指数数值。

30、一种乘法运算的方法,所述方法包括:

31、将两个浮点数进行解码,得到解码后的第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位以及第二尾数位;

32、捕获第一尾数位以及第二尾数位的最大位宽,并根据第一尾数位以及第二尾数位的最大位宽匹配对应的延时时钟,以改变获取流动数据的速度;其中,所述流动数据包括第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位、第二尾数位、目标符号位、目标指数数值以及目标尾数位;

33、根据第一符号位、第二符号位、第一权重位、第二权重位、第一指数偏置位、第二指数偏置位、第一尾数位以及第二尾数位进行运算得到两个浮点数相乘后的目标符号位、目标指数数值以及目标尾数位;

34、根据目标符号位、目标指数数值以及目标尾数位得到目标运算结果。

35、本发明的进一步设置,所述目标尾数位的最高位通过以下方式确定:

36、将第一尾数位的值与第二尾数位的值相乘,如果存在进位,则确定最高位为1;如果不存在进位,则确定最高位为0

37、本发明所提供的一种自适应时钟电路、乘法运算电路及乘法运算的方法,所述自适应时钟电路包括:捕获单元、异步数据缓冲器以及延时控制链模块;所述捕获单元用于比较第一尾数位以及第二尾数位的位宽,并获取两者之中的最大位宽,所述第一尾数位以及所述第二尾数位为浮点数经过解码后的小数;所述延时控制链模块用于根据最大位宽匹配所述异步数据缓冲器的延时时钟;所述异步数据缓冲器用于根据延时时钟传输数据。本发明基于posit独特的数据特性,通过捕获单元获取最大位宽,并应用自适应时钟技术,根据最大位宽匹配所述异步数据缓冲器的延时时钟,以解决posit乘法器速度慢的问题,同时自适应时钟电路的控制逻辑精简而高效(仅需增加捕获单元以及延时控制链模块),相比于其他提速方案大大减小了面积以及功耗开销,性能显著提高。

- 还没有人留言评论。精彩留言会获得点赞!