用于卷积运算的改进的电路、芯片、设备及方法与流程

本公开涉及电子电路领域,并且更具体地,涉及用于卷积运算的改进的电路、芯片、设备及方法。

背景技术:

1、卷积运算是一种常见数学运算。卷积运算具有广泛的应用场景。例如,作为深度学习的代表算法之一,卷积神经网络(convolutional neural network,cnn)包含大量的卷积运算并且具有深度结构。随着技术的发展和需求的增长,在诸如卷积神经网络之类的应用场景中所执行的卷积运算显著增长。

技术实现思路

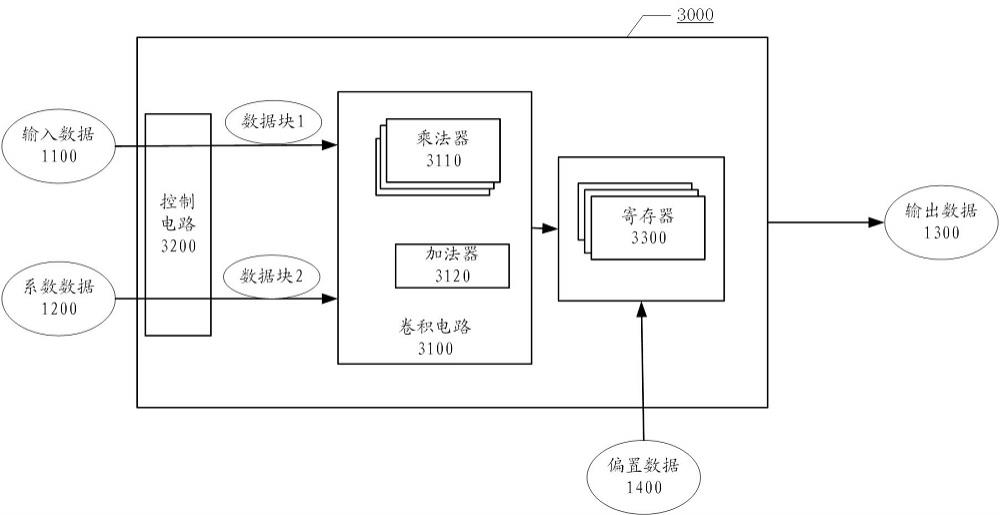

1、本公开的一方面提供了一种用于卷积运算的电路,该电路包括卷积电路,卷积电路被配置为在每个周期对以下两项执行卷积运算:(1)来自卷积网络的多个输入通道的输入数据的至少一部分,和(2)卷积网络的多个卷积核的系数数据的至少一部分,其中多个卷积核中的每个卷积核与卷积网络的多个输出通道中的相应输出通道相关联。该电路被配置为使得提供给卷积电路以执行卷积运算的以下一项跨多个连续的周期保持不变:(1)输入数据中被提供给卷积电路的第一数据块,或(2)系数数据中被提供给卷积电路的第二数据块。

2、本公开的另一方面提供了一种用于卷积运算的方法,包括:提供卷积电路,该卷积电路被配置为在每个周期对以下两项执行卷积运算:(1)来自卷积网络的多个输入通道的输入数据的至少一部分,和(2)卷积网络的多个卷积核的系数数据的至少一部分,多个卷积核中的每个卷积核与卷积网络的多个输出通道中的相应输出通道相关联;使得提供给卷积电路以执行卷积运算的以下一项跨多个连续的周期保持不变:(1)输入数据中被提供给卷积电路的第一数据块,或(2)系数数据中被提供给卷积电路的第二数据块。

3、本公开的还有一方面提供了一种计算芯片,包括如本公开所述的用于卷积运算的电路。

4、本公开的还有一方面提供了一种计算设备,包括如本公开所述的计算芯片。

5、本公开的还有一方面提供了一种计算装置,包括:一个或多个处理器;以及存储计算机可执行指令的存储器,所述计算机可执行指令在被所述一个或多个处理器执行时使得所述一个或多个处理器执行根据本公开所述的任何方法。

6、本公开的还有一方面提供了一种其上存储有计算机可执行指令的非瞬态存储介质,所述计算机可执行指令在被一个或多个处理器执行时使得所述一个或多个处理器执行根据本公开所述的任何方法。

7、通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其优点将会变得更为清楚。

技术特征:

1.一种用于卷积运算的电路,其中,所述电路包括:

2.如权利要求1所述的电路,其中,所述多个输入通道的数量为cin,所述多个输出通道的数量为cout,所述电路被配置为:

3.如权利要求2所述的电路,其中,所述电路被配置为:

4.如权利要求3所述的电路,其中,所述电路被配置为:

5.如权利要求4所述的电路,其中,所述电路还被配置为:

6.如权利要求5所述的电路,其中,所述电路还被配置为:

7.如权利要求1所述的电路,其中,所述多个输入通道的数量为cin,所述电路被配置为:

8.如权利要求7所述的电路,其中,所述电路被配置为:

9.如权利要求8所述的电路,其中,所述电路被配置为:

10.如权利要求9所述的电路,其中所述输入数据为图像数据。

11.如权利要求8所述的电路,其中,所述电路还被配置为:

12.如权利要求8所述的电路,其中,所述电路被配置为:

13.如权利要求12所述的电路,其中,所述电路被配置为:

14.如权利要求1所述的电路,其中,所述卷积电路包括乘法器和加法器,所述乘法器和所述加法器包括逻辑门元件,所述逻辑门元件被配置为通过乘累加运算来执行所述卷积运算。

15.如权利要求1所述的电路,所述输入数据与以下中的至少一项相关联:

16.如权利要求1所述的电路,其中,所述系数数据与所述卷积网络的一个或多个权重系数相关联。

17.一种计算芯片,包括如权利要求1-16中任一项所述的用于卷积运算的电路。

18.一种计算设备,包括如权利要求17所述的计算芯片。

19.一种用于卷积运算的方法,包括:

20.如权利要求19所述的方法,其中,所述多个输入通道的数量为cin,所述方法包括:

技术总结

本公开涉及用于卷积运算的改进的电路、芯片、设备及方法。一种用于卷积运算的电路包括:卷积电路,被配置为在每个周期对以下两项执行卷积运算:(1)来自卷积网络的多个输入通道的输入数据的至少一部分,和(2)卷积网络的多个卷积核的系数数据的至少一部分,其中多个卷积核中的每个卷积核与卷积网络的多个输出通道中的相应输出通道相关联。该电路被配置为:使得提供给卷积电路以执行卷积运算的以下一项跨多个连续的周期保持不变:(1)输入数据中被提供给卷积电路的第一数据块,或(2)系数数据中被提供给卷积电路的第二数据块。

技术研发人员:薛可,范志军,许超,刘建波,杨作兴

受保护的技术使用者:深圳比特微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!