微处理芯片及代码下载方法与流程

本技术涉及芯片测试,具体地涉及一种微处理芯片及代码下载方法。

背景技术:

1、随着近年来片上系统(system on chip,soc)的广泛应用,解决soc芯片的可测试性问题,已成为人们关注和研究的热点。芯片在生产过程中主要有两次测试:晶圆测试(chip probing,cp)和最终测试(final test,ft)。其中ft测试是对封装后的芯片进行测试,一般要求更加严格,要尽可能检测出有故障的芯片。相关技术中,一般通过联合测试工作组(joint test action group,jtag)向芯片内下载测试代码并进行测试,但此方式存在下载速度慢、影响芯片测试效率和测试成本的问题。

技术实现思路

1、有鉴于此,本技术提供一种微处理芯片及代码下载方法,有助于提高代码数据的下载速度,提高芯片的测试效率。

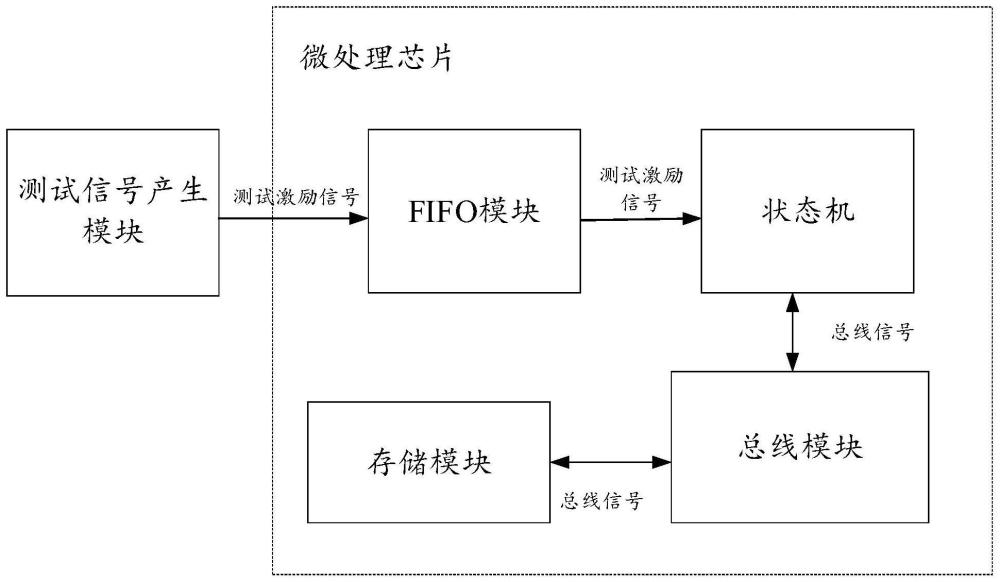

2、第一方面,本发明实施例提供了一种微处理芯片,所述微处理芯片设置有先进先出(first input first output,fifo)模块、状态机、总线模块和存储模块;其中,

3、所述fifo模块,用于接收基于外部时钟的测试激励信号,并对所述测试激励信号进行时域转换;

4、所述状态机,用于将时域转换后的测试激励信号编码为总线信号;

5、所述总线模块,用于将所述总线信号传输到所述存储模块,以实现对代码数据的下载存储和/或编程。

6、在一些实施例中,所述测试激励信号包括:复位信号、代码长度信息、传入启动地址、代码数据、数据有效信号、传输结束标志中的一项或多项的组合,其中:

7、所述复位信号,用于复位所述外部时钟和所述fifo模块;

8、所述代码长度信息,用于对传输的代码数据进行计数,和/或,用于代码数据传输结束后的数据校验;

9、所述传入启动地址,用于指示代码数据的存储起始地址;

10、所述代码数据,以指定地址为存储起始地址并按照地址递增方式存储;

11、所述数据有效信号,用于表示当前传入的所述代码数据为有效数据;

12、所述传输结束标志,用以表示代码数据的传输结束,以及用于指示对代码数据进行crc校验并向外部传输校验结果。

13、在一些实施例中,所述fifo模块为异步fifo,用以实现所述代码数据的暂存和时钟域转换;

14、所述fifo模块包括:多比特代码信号引脚;当所述测试激励信号包括所述代码数据和所述传入启动地址时,所述代码数据和所述传入启动地址分时复用所述多比特代码信号引脚。

15、在一些实施例中,所述微处理芯片还设置有校验模块;

16、所述校验模块包括发送端和接收端,所述发送端用于接收所述微处理芯片的io端口传输的数据,所述接收端与所述fifo模块的读数据端口连接;

17、所述校验模块,具体用于将接收端获取到的代码数据与crc初始值做crc校验计算,得到crc校验结果并暂存在数据寄存器中;当接收端获取到下一个有效的代码数据时,将当前获取的代码数据与所述数据寄存器存储的crc校验结果做crc校验计算,得到新的crc校验结果;当代码数据传输结束时,将最终计算得到的crc校验结果与从外部获取的crc参考值进行对比,若比对一致,则警报信号保持低电平;若比对不一致,则警报信号拉高。

18、在一些实施例中,所述状态机,包括:

19、空闲状态,当总线模块复位且空闲时所述状态机为空闲状态,当所述fifo模块接收到有效的数据时从所述空闲状态切换至总线请求状态;

20、总线请求状态,用于向总线模块发起总线接收请求,并在总线模块响应所述总线接收请求后切换至开始状态,并从开始状态无条件跳转至地址和命令传输状态;

21、地址和命令传输状态,用于向总线模块发送测试激励信号包含的地址和命令,并在总线模块空闲时跳转至数据传输状态;

22、数据传输状态,用于向总线模块传输测试激励信号包含的代码数据,当所述总线模块空闲且代码数据的传输没有结束时,跳转回所述地址和命令传输状态;

23、校验状态,用于当代码数据传输结束时进入对代码数据进行crc校验的状态,当对代码数据的校验结束后无条件跳转至所述空闲状态。

24、第二方面,本发明实施例提供了一种微处理芯片的代码下载方法,所述方法包括:

25、接收基于外部时钟的测试激励信号,并对所述测试激励信号进行时域转换;

26、将时域转换后的测试激励信号编码为总线信号;

27、对所述总线信号进行存储,以实现代码数据的下载存储和/或编程。

28、在一些实施例中,所述测试激励信号包括:复位信号、代码长度信息、传入启动地址、代码数据、数据有效信号、传输结束标志中的一项或多项的组合,其中:

29、所述复位信号,用于复位所述外部时钟和所述fifo模块,有益效果在于复位外部的时钟和驱动激励信号和相关逻辑,复位信号用于在每次下载启动时复位相关逻辑,防止不确定状态出现;

30、所述代码长度信息,用于对传输的代码数据进行计数,和/或,用于代码数据传输结束后的数据校验;

31、所述传入启动地址,用于指示代码数据的存储起始地址;

32、所述代码数据,以指定地址为存储起始地址并按照地址递增方式存储,可以满足对存储设备中进行编程和下载到预设的分配区域,提高存储设备的利用和编程灵活性;

33、所述数据有效信号,用于表示当前传入的所述代码数据为有效数据;

34、所述传输结束标志,用以表示代码数据的传输结束,以及用于指示对代码数据进行crc校验并向外部传输校验结果;

35、代码长度信息和代码数据组合的有益效果:代码下载实现发送端和芯片内部跨时钟域后的数据实现校验,通过crc硬件实现算法对起始地址和数据信息校验,防止有效信号经过芯片io和跨时钟域后出现异常。

36、在一些实施例中,所述方法还包括:

37、当获取到有效的代码数据时,将所述代码数据与crc初始值做crc校验计算,得到crc校验结果并暂存在数据寄存器中;

38、当接收端获取到下一个有效的代码数据时,将当前获取的代码数据与所述数据寄存器存储的crc校验结果做crc校验计算,得到新的crc校验结果;

39、当代码数据传输结束时,将最终计算得到的crc校验结果与从外部获取的crc参考值进行对比,若比对一致,则警报信号保持低电平;若比对不一致,则警报信号拉高。

40、在一些实施例中,所述将时域转换后的测试激励信号编码为总线信号包括状态机的状态转换,其中包括:

41、空闲状态,当总线模块复位且空闲时所述状态机为空闲状态,当所述fifo模块接收到有效的数据时从所述空闲状态切换至总线请求状态;

42、总线请求状态,用于向总线模块发起总线接收请求,并在总线模块响应所述总线接收请求后切换至开始状态,并从开始状态无条件跳转至地址和命令传输状态;

43、地址和命令传输状态,用于向总线模块发送测试激励信号包含的地址和命令,并在总线模块空闲时跳转至数据传输状态;

44、数据传输状态,用于向总线模块传输测试激励信号包含的代码数据,当所述总线模块空闲且代码数据的传输没有结束时,跳转回所述地址和命令传输状态;

45、校验状态,用于当代码数据传输结束时进入对代码数据进行crc校验的状态,当对代码数据的校验结束后无条件跳转至所述空闲状态。

46、在一些实施例中,可以将包含代码数据的测试激励信号编码为总线信号并传输到存储模块中进行存储,此方式不存在对存储模块中代码数据进行修改的情形,实现代码数据在存储模块的下载存储。

47、在一些实施例中,可以将包含代码数据的测试激励信号编码为总线信号并传输到存储模块中以对存储模块中的部分代码数据进行替代存储,此方式存在对存储模块中的代码数据的修改的情形,可以实现对存储模块中代码数据的编程。

48、本发明实施例中,通过fifo模块对外部输入的测试激励信号进行时域转换,有利于测试激励信号在微处理芯片的各模块之间传输。并且,本发明实施例将测试激励信号转换为总线信号,通过微处理芯片内部的总线架构可以将代码数据以总线方式传输到微处理芯片的其它模块或者存储,实现代码数据的下载存储或者编程功能。相较于单线下载模式,本发明实施例采用总线方式下载代码数据有助于提高代码下载速度,提高芯片的测试效率。

- 还没有人留言评论。精彩留言会获得点赞!