一种统计眼图的仿真方法、装置、设备及存储介质与流程

本申请涉及眼图仿真,具体涉及一种统计眼图的仿真方法、装置、设备及存储介质。

背景技术:

1、传统的封装芯片眼图仿真通过时域仿真实现,具体地,对封装芯片的全链路网表进行数百个甚至上千个伪随机码周期(如prbs7)的时域仿真,即封装芯片眼图仿真的实际耗时高达几天乃至几个星期,具体地,时域仿真设置的仿真时间越长,得到的仿真结果越恶劣,眼图的眼高眼宽越小,眼图仿真结果与实际测试的结果也就越接近。

2、然而,随着封装芯片的网表结构越来越复杂,时域仿真所需的仿真时间也会越来越长。

技术实现思路

1、鉴于以上问题,本申请提供一种统计眼图的仿真方法、装置、设备及存储介质,以解决通过时域仿真实现封装芯片眼图仿真的时间久的技术问题。

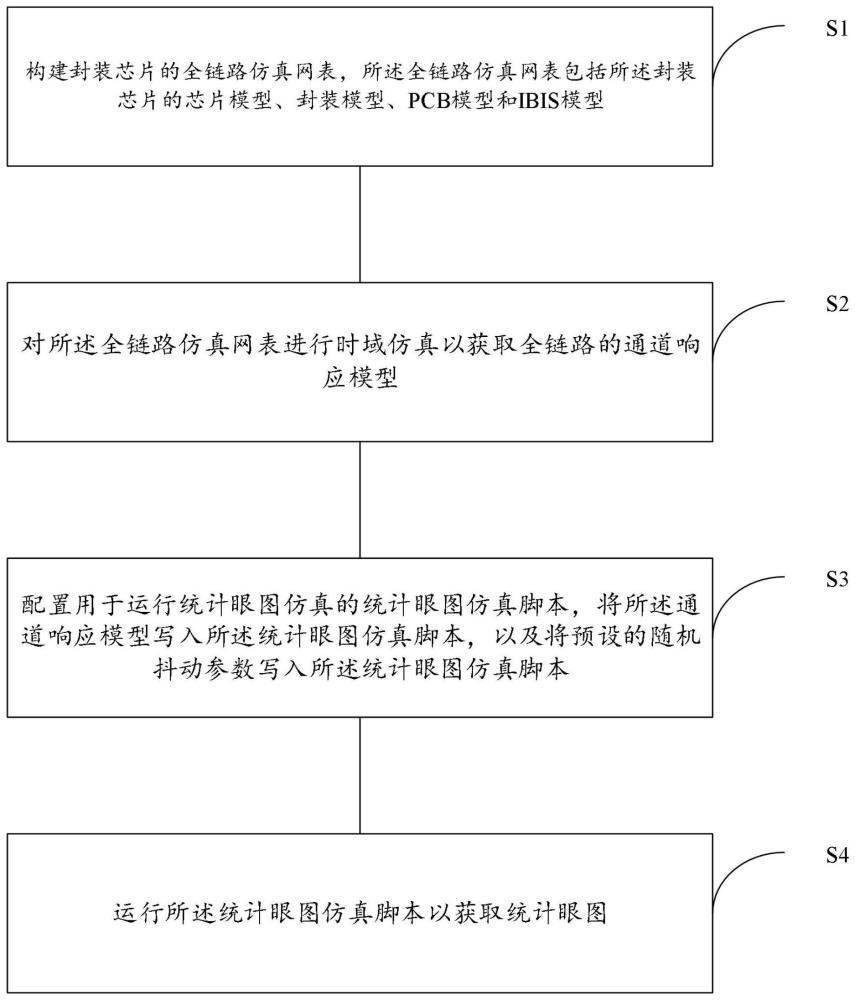

2、第一方面,本申请提供一种统计眼图的仿真方法,包括:

3、构建封装芯片的全链路仿真网表,所述全链路仿真网表包括所述封装芯片的芯片模型、封装模型、pcb模型和ibis模型;

4、对所述全链路仿真网表进行时域仿真以获取全链路的通道响应模型;

5、配置用于运行统计眼图仿真的统计眼图仿真脚本,将所述通道响应模型写入所述统计眼图仿真脚本,以及将预设的随机抖动参数写入所述统计眼图仿真脚本;

6、运行所述统计眼图仿真脚本以获取统计眼图。

7、在一些实施例中,本申请提供的统计眼图的仿真方法中,所述对所述全链路仿真网表进行时域仿真以获取全链路的通道响应模型的步骤,包括:

8、设置所述时域仿真的仿真时间为n个伪随机码周期,1≤n≤128;

9、对所述全链路仿真网表进行时域仿真,存储所述时域仿真的仿真结果。

10、在一些实施例中,本申请提供的统计眼图的仿真方法中,所述对所述全链路仿真网表进行时域仿真以获取全链路的通道响应模型的步骤,还包括:

11、将所述通道响应模型存储为第一文件,以及将所述第一文件置于第一目录下。

12、在一些实施例中,本申请提供的统计眼图的仿真方法中,所述将所述通道响应模型写入所述统计眼图仿真脚本的步骤,包括:

13、向所述统计眼图仿真脚本写入第一调用函数,所述第一调用函数用于调用所述第一目录下的第一文件。

14、在一些实施例中,本申请提供的统计眼图的仿真方法中,所述将预设的随机抖动参数写入所述统计眼图仿真脚本的步骤,包括:

15、将存储所述随机抖动参数的第二文件置于第二目录下;

16、向所述统计眼图仿真脚本写入第二调用函数,所述第二调用函数用于调用所述第二目录下的第二文件。

17、在一些实施例中,本申请提供的统计眼图的仿真方法中,所述全链路仿真网表和所述统计眼图仿真脚本的仿真语言为spice语言。

18、第二方面,本申请提供一种统计眼图的仿真装置,包括:

19、全链路仿真网表构建模块,用于构建封装芯片的全链路仿真网表,所述全链路仿真网表包括所述封装芯片的芯片模型、封装模型、pcb模型和ibis模型;

20、时域仿真模块,用于对所述全链路仿真网表进行时域仿真以获取全链路的通道响应模型;

21、统计眼图仿真脚本配置模块,用于配置用于运行统计眼图仿真的统计眼图仿真脚本,将所述通道响应模型写入所述统计眼图仿真脚本,以及将预设的随机抖动参数写入所述统计眼图仿真脚本;

22、眼图仿真模块,用于运行所述统计眼图仿真脚本以获取统计眼图。

23、第三方面,本申请提供一种电子设备,包括存储器和处理器,其中:

24、所述存储器用于存储计算机程序;

25、所述处理器用于读取所述存储器中的程序并执行如上述第一方面提供的统计眼图的仿真方法的步骤。

26、第四方面,本申请提供一种计算机可读存储介质,其上存储有可读的计算机程序,该程序被处理器执行时实现如上述第一方面提供的统计眼图的仿真方法的步骤。

27、本申请提供的一种统计眼图的仿真方法、装置、设备及存储介质,统计眼图的仿真方法包括:构建封装芯片的全链路仿真网表,全链路仿真网表包括封装芯片的芯片模型、封装模型、pcb模型和ibis模型;对全链路仿真网表进行时域仿真以获取封装芯片全链路的通道响应模型;配置用于运行统计眼图仿真的统计眼图仿真脚本,将通道响应模型写入统计眼图仿真脚本,以及将预设的随机抖动参数写入统计眼图仿真脚本;运行统计眼图仿真以获取统计眼图。本申请提供的统计眼图的仿真方法,基于全链路仿真网表的通道响应模型和预设的随机抖动参数来获取统计眼图,只需要通过时域仿真获取较短周期内的通道响应模型即可,大幅度减少了时域仿真时间。此外,本申请提供的统计眼图的仿真方法还加入随机抖动参数,进一步提高了统计眼图的仿真精度。

技术特征:

1.一种统计眼图的仿真方法,其特征在于,包括:

2.如权利要求1所述的统计眼图的仿真方法,其特征在于,所述对所述全链路仿真网表进行时域仿真以获取所述全链路仿真网表的通道响应模型的步骤,包括:

3.如权利要求1所述的统计眼图的仿真方法,其特征在于,所述对所述全链路仿真网表进行时域仿真以获取所述全链路的通道响应模型的步骤,还包括:

4.如权利要求3所述的统计眼图的仿真方法,其特征在于,所述将所述通道响应模型写入所述统计眼图仿真脚本的步骤,包括:

5.如权利要求1所述的统计眼图的仿真方法,其特征在于,所述将预设的随机抖动参数写入所述统计眼图仿真脚本的步骤,包括:

6.如权利要求1所述的统计眼图的仿真方法,其特征在于,描述所述全链路仿真网表和所述统计眼图仿真脚本的仿真语言为spice语言。

7.一种统计眼图的仿真装置,其特征在于,包括:

8.一种电子设备,其特征在于,包括存储器和处理器,其中:

9.一种计算机可读存储介质,其特征在于,其上存储有可读的计算机程序,该程序被处理器执行时实现如权利要求1~6所述的任一统计眼图的仿真方法的步骤。

技术总结

本申请属于眼图仿真技术领域,公开了一种统计眼图的仿真方法、装置、设备及存储介质,统计眼图的仿真方法包括:构建封装芯片的全链路仿真网表;对全链路仿真网表进行时域仿真以获取全链路的通道响应模型;配置用于运行统计眼图仿真的统计眼图仿真脚本,将通道响应模型写入统计眼图仿真脚本,以及将预设的随机抖动参数写入统计眼图仿真脚本;运行统计眼图仿真脚本以获取统计眼图。本申请提供的统计眼图的仿真方法,只需要获取时域仿真较短周期内的通道响应模型即可,大幅度减少了时域仿真时间。此外,本申请提供的统计眼图的仿真方法还加入了随机抖动参数,进一步提高了统计眼图的仿真精度。

技术研发人员:刘新功,刘蒲霞

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!