一种考虑封装效应的射频功放芯片热电联合仿真方法及系统

本发明属于射频功放芯片热电仿真,尤其涉及一种考虑封装效应的射频功放芯片热电联合仿真方法及系统。

背景技术:

1、在射频微系统应用中,通常需要将射频芯片放置于特定的封装结构中以便于与其它功能模块进行集成。然而,封装结构的引入会影响芯片的散热能力,进而降低芯片的输出性能。因此,亟需研究面向射频芯片尤其是功率放大器芯片的动态电-热耦合仿真方法,从而为射频芯片及其封装结构的热-电联合优化设计提供指导。

2、目前,针对芯片热-电耦合仿真的方法主要有两种。一种是有限元仿真方法,另一种是基于晶体管紧凑模型的热-电仿真方法。其中,有限元仿真方法通常需要已知晶体管特定偏置工作点下的静态功耗,结合芯片及其封装结构进行三维有限元仿真,得到在特定电学特性对应的芯片热分布。2015年浙江大学的r.zhang等人开发混合td-fem算法并将其应用于带有金刚石散热器的多指algan/gan hemt的热响应仿真(zhang r,zhao w s,yin wy,et al.impacts of dia-mond heat spreader on the thermomechanicalcharacteristics of high-power algan/gan hemts[j].diamond&relatedmaterials,2015,52:25-31.)。其仿真中大多数本构参数,如电导率、热导率、热膨胀系数和杨氏模量均被设置为温度相关参数,经验证该方法具有很高的仿真精度。2017年南京电子器件研究所郭怀新等人基于gan功率芯片,利用有限元分析方法开展了芯片近结区热特性模拟方法的研究(郭怀新,韩平,陈堂胜.基于gan功率器件的热仿真技术研究[j].固体电子学研究与进展,2017,37(03):176-181.)。建立了芯片近结区散热能力仿真评估的三维理论模型,系统地研究了不同的初始条件、边界条件、晶格热效应及结构理论假设等因素对仿真精度的影响,经验证该方法与测试结果误差在10%以内。以上方法虽然能够反映芯片封装带来的影响,但需要提前输入晶体管在特定偏置点的静态功率耗散,即只能计算晶体管在单个电学特性状态下的热分布,不具备当电学特性动态变化(如射频激励)时的热分析能力。不同于有限元仿真方法,基于晶体管紧凑模型的热-电仿真方法主要依托晶体管模型内的热阻模型,结合实际射频激励下晶体管动态电流和电压特性进行计算。2017年,电子科技大学徐跃杭等人提出了一种gan hemt非线性热阻建模方法(xu y,wang c,sun h,et al.a scalablelarge-signal multiharmonic model of algan/gan hemts and its application in c-band high power amplifier mmic[j].ieee transactions on microwave theory andtechniques,2017,65(8):2836-2846.),并成功应用于晶体管非线性大信号建模。基于该模型准确预测了高功率放大器芯片的基波和谐波特性,实现了考虑热-电耦合效应的精确设计。2021年,巴塞罗那微电子研究所miquel vellvehi等人采用热成像方法,基于mmic芯片热测试,进行了热阻提取,将建立的热电网络嵌入晶体管紧凑模型后,实现了芯片热-电耦合特性的准确预测(m.vellvehi,x.et al.local thermal resistanceextraction in monolithic microwave integrated circuits[j].ieee transactionson industrial electronics,2021,68(12):12840-12849.)。该类方法虽然能够在晶体管热电网络的热阻提取中考虑封装效应的影响,但热电网络通常只针对固定的晶体管结构,且需要结合复杂的电学或热学特性测试进行模型参数提取。由于集总元件的限制,该网络对热阻的非线性特性表征也存在局限性。此外,热电子网络仅具备表征单个器件结构自热效应的能力,无法表征不同晶体管间的互热效应。因此,采用晶体管热电子网络来分析芯片的热特性存在很大的局限性。

3、由上述现有技术分析可知,两类方法在应用于考虑封装效应的射频功放芯片热仿真时均存在一定的局限性,很难同时满足射频激励下功耗动态变化的热分布计算以及芯片封装效应的精细化表征。因此,如何实现芯片级热效应的动态仿真,获取考虑外围封装影响的射频功放芯片热分布,仍需要进一步研究。

4、通过上述分析,现有技术存在的问题及缺陷为:目前主流仿真方法不能在芯片级的电热耦合动态仿真的基础上表征封装结构和晶体管间互热效应的影响,因此,开发一种考虑外围封装影响的射频功放芯片热电效应的动态仿真方法,对功率放大器等射频电路及其封装结构的热管理具有很重要的意义。

技术实现思路

1、针对现有技术存在的问题,本发明提供了一种考虑封装效应的射频功放芯片热电联合仿真方法及系统。

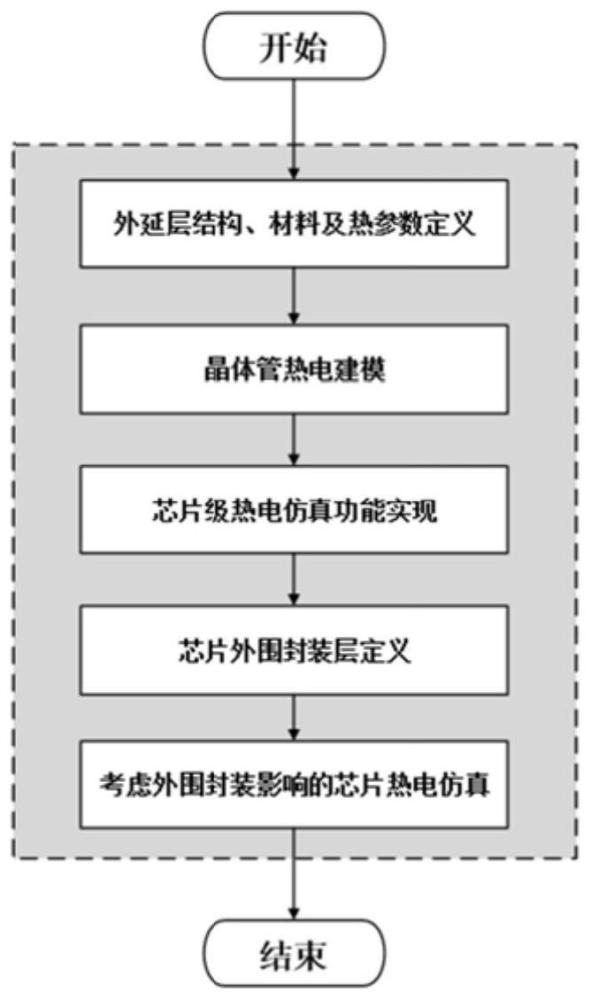

2、本发明是这样实现的,首先定义热层与材料热参数,建立晶体管的热电模型,在此基础上,结合芯片及其外围封装结构的版图,最终实现考虑封装效应的射频功放芯片热电联合仿真方法,所述考虑封装效应的射频功放芯片热电联合仿真方法包括以下步骤:

3、步骤一,对外延层结构、材料及热参数进行定义;

4、步骤二,建立晶体管热电模型;

5、步骤三,进行芯片级热电仿真;

6、步骤四,对芯片外围封装层进行定义;

7、步骤五,进行考虑外围封装影响的芯片热电仿真。

8、进一步,步骤一中对晶体管模型pdk中的层定义信息包含钝化层、金属层、本征层、热源层、热传感器层、层间互联通孔、背孔和衬底层等外延层。

9、进一步,步骤一中设置金属层、互联通孔以及背孔材料为铜,晶体管表面保护层材料为sin,自由空间材料为空气,同时设置热导率与热容。

10、进一步,考虑本征层gan材料和sic材料热导率的温度相关性,定义不同温度散点下的两种材料的热导率,温度相关性分别采用下式进行描述:

11、

12、

13、式中,t为开尔文温度,热导率单位均为w/m·k。

14、进一步,步骤二具体包括根据步骤一的层定义,进行晶体管版图结构绘制,并在晶体管版图结构下方绘制热源层和热传感器层,各热源层的大小要覆盖栅指,热传感器层的大小略大于热源层;完成晶体管版图文件定义后,建立该晶体管对应的原理图。

15、进一步,晶体管沟道温度采集端口外接沟道温度计算网络,该网络包含与晶体管栅指数相同的电阻子网络,每个子网络与晶体管版图中每个栅指对应。

16、进一步,步骤三的芯片级热电仿真具体包括以下步骤:

17、步骤31,根据步骤一中的层定义,进行芯片整体版图结构绘制,芯片内晶体管位置处则直接采用步骤二中的版图定义;

18、步骤32,进行芯片版图文件定义后,新建该芯片对应的原理图,原理图可采用晶体管模型和包含无源s参数信息的版图symbol相结合的模式进行构建;

19、步骤33,在此基础上,新建芯片原理图symbol,并基于该symbol搭建热电仿真平台顶层原理图;

20、步骤34,完成上述芯片原理图和版图定义后,结合原有的仿真计算控件开启热电仿真。

21、进一步,步骤四采用层嵌套的方式,将步骤一中芯片的层定义打包作为子集合,下方再进行封装层的定义;在完成各层材料设置后,设置热导率和热容。

22、进一步,步骤五的考虑外围封装影响的芯片热电仿真具体包括以下步骤:

23、步骤51,根据步骤四中的层定义,进行芯片版图和封装结构版图组合;

24、步骤52,进行芯片封装版图文件定义后,新建该版图对应的原理图,添加步骤三中芯片原理图对应symbol,并搭建仿真平台顶层原理图;

25、步骤53,完成上述步骤后,加载步骤四形成的最终热层文件,结合原有的仿真计算控件开启热电仿真。

26、本发明的另一目的在于提供一种考虑封装效应的射频功放芯片热电联合仿真方法的考虑封装效应的射频功放芯片热电联合仿真系统,该系统包括:

27、外延层定义模块,用于对外延层结构、材料及热参数进行定义;

28、热电模型建立模块,用于建立晶体管热电模型;

29、第一热电仿真模块,用于进行芯片级热电仿真;

30、外围封装层定义模块,用于对芯片外围封装层进行定义;

31、第二热电仿真模块,用于进行考虑外围封装影响的芯片热电仿真。

32、结合上述的技术方案和解决的技术问题,本发明所要保护的技术方案所具备的优点及积极效果为:

33、第一,本发明基于芯片级的有限元热仿真及晶体管模型,建立了考虑外围封装影响的射频功放芯片热电效应的动态仿真方法,该方法实现了射频时变信号激励下,带封装结构功放芯片热分布的动态仿真计算。对比目前主流热电耦合仿真技术,该方法可以仿真动态热电效应,同时可以考虑晶体管间互热效应和芯片封装结构的影响。

34、该技术方案为带有封装结构的功率芯片的动态热仿真提供了可行的实现路径,尤其是可以对射频功放芯片以及封装结构优化与热管理提供重要指导。

35、第二,本发明的技术方案填补了国内外业内技术空白:填补了包含外围封装影响的射频功放芯片热电效应的动态仿真的技术空白。

36、本发明的技术方案是否解决了人们一直渴望解决、但始终未能获得成功的技术难题:解决了目前主流热电耦合仿真技术无法实现射频时变信号激励下,带封装结构功放芯片热分布动态仿真计算的技术难题。

37、第三,本发明提供的考虑封装效应的射频功放芯片热电联合仿真方法取得的显著技术进步包括:

38、1)全面的热电特性分析:

39、通过结合外延层结构、材料及热参数的详细定义,该方法能全面分析射频功放芯片的热电特性。这种全面性的分析比传统的仿真方法更为精确,能够预测和解决实际应用中遇到的问题。

40、2)晶体管热电模型的准确建立:

41、步骤二中晶体管版图结构的绘制和热源层及热传感器层的配置,使得对晶体管的热电行为模拟更为准确。这对于理解芯片的热行为和电性能的交互作用至关重要。

42、3)封装效应的考虑:

43、通过在仿真中考虑芯片外围的封装层,这种方法能够更准确地模拟实际运行环境中的热电特性。封装层的考虑使得仿真结果更贴近实际应用,提高了设计的可靠性和实用性。

44、4)温度相关性的准确描述:

45、考虑gan材料和sic材料热导率的温度相关性,使得对芯片热特性的模拟更加精确。这种考虑温度效应的方法能更好地预测芯片在不同操作条件下的性能。

46、5)芯片级热电仿真的高效实施:

47、通过对芯片整体版图结构的绘制和原理图的构建,步骤三实现了对整个芯片热电特性的高效仿真。这种方法使得设计者能够在初期设计阶段即评估芯片的整体性能,减少返工和优化设计。

48、6)热导率和热容的详细设置:

49、在步骤四中对各层材料的热导率和热容进行详细设置,进一步提升了仿真结果的准确度和可靠性。

50、综上所述,本发明提供的仿真方法在射频功放芯片设计中提供了更准确的热电特性分析,考虑封装效应和温度相关性,提高了设计的准确性和可靠性,对于高性能射频功放芯片的研发具有重要的实用价值。

- 还没有人留言评论。精彩留言会获得点赞!