电路仿真验证方法及装置、电子设备、存储介质与流程

本申请涉及电路仿真验证,具体涉及一种电路仿真验证方法及装置、电子设备、存储介质。

背景技术:

1、近年来,随着无线通信技术发展迅速,对涉及的集成电路也提出了更高的要求,要求具有更优的信号处理能力和更短的产品开发周期。以射频集成电路为例,电路主要由晶体管有源器件和电感电容等无源器件构成,按照传统的设计方法,设计者首先根据系统需求制定集成电路的性能参数,确定电路结构画原理图,用电路仿真确定原理图的参数设计正确,再根据电路原理图画版图,完成版图之后需要进行版图和原理图的对照验证,以确定版图的正确性,接着提取版图的寄生参数并做后仿真,如果后仿真的结果不理想,则返回原理图优化设计参数,同时修改相应的版图,然后继续提取版图的寄生参数并做后仿真,如果后仿真的结果达到设计的预期效果就送代工厂制作芯片。

2、在进行仿真验证的过程中,计时器(timer)会周期性产生仿真点,在该仿真点所在的时刻,仿真工具插入触发事件以执行相应的仿真事件。也就是说,在每一仿真点所在的时刻,仿真工具都需要进行详细求解,例如通过建立电路方程进行牛顿迭代等方式求解出电路各个部分的节点电压和支路电流。由于每一个仿真点都需要进行大量的数学计算,因此仿真点的个数越多,仿真工具计算所花费的总时间也越多。当计时器的频率较高或者需要较高的仿真精度时,仿真模型会产生大量的仿真点,从而对仿真速度造成严重影响。

技术实现思路

1、鉴于此,本申请提供了一种电路仿真验证方法及装置、电子设备、存储介质,可以改善仿真点的个数越多以及由此导致的影响仿真速度的问题。

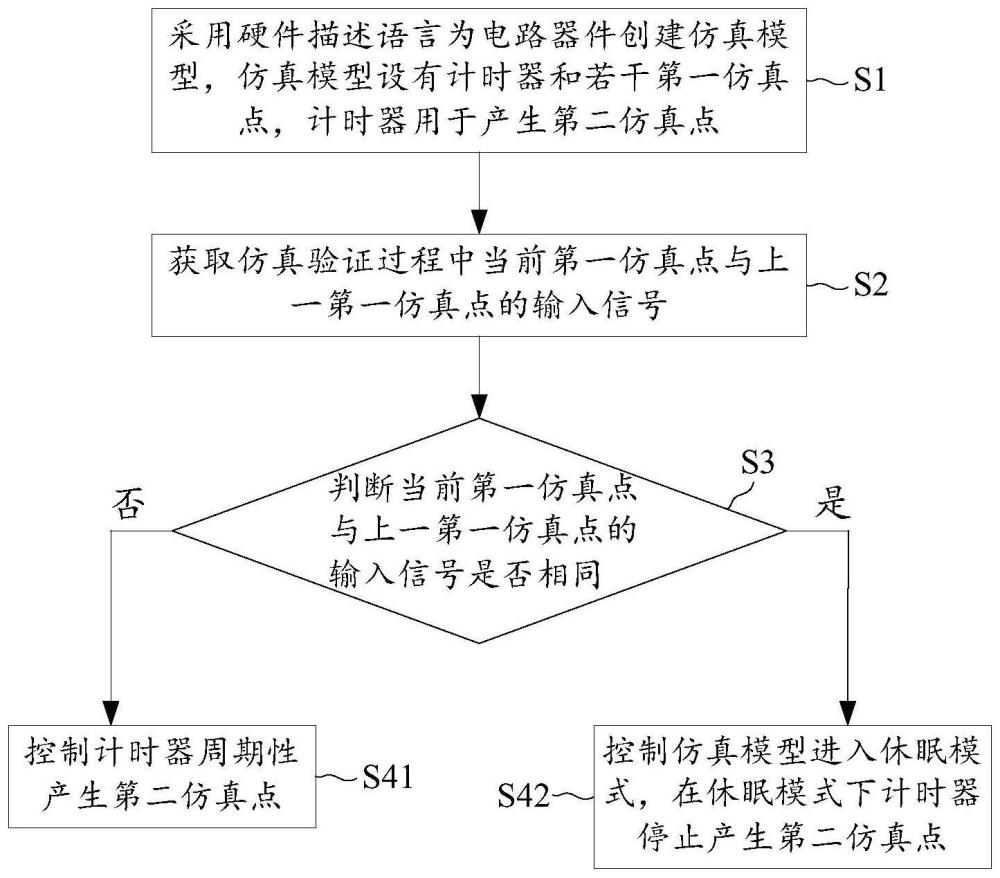

2、本申请提供的一种电路仿真验证方法,包括:

3、采用硬件描述语言为电路器件创建仿真模型,所述仿真模型设有计时器和若干第一仿真点,所述计时器用于产生第二仿真点;

4、获取仿真验证过程中当前第一仿真点与上一第一仿真点的输入信号;

5、判断当前第一仿真点与上一第一仿真点的输入信号是否相同;

6、若否,则控制所述计时器周期性产生所述第二仿真点;

7、若是,则控制所述仿真模型进入休眠模式,在所述休眠模式下所述计时器停止产生所述第二仿真点。

8、可选的,所述输入信号包括电压、电流、频率及功率中的至少一种。

9、可选的,所述电路器件未设有激励源,在仿真验证过程中,所述仿真模型的输入信号保持不变时输出信号保持不变。

10、可选的,判断所述电路器件是否设有激励源的方式,包括:

11、获取所述仿真模型中的所有赋值语句;

12、在所述仿真模型的输入信号保持不变时,根据所述赋值语句判断相邻两个第一仿真点的对应变量值是否具有关联关系;

13、若是,则确定所述电路器件设有激励源;

14、若否,则确定所述电路器件未设有激励源。

15、可选的,在所述休眠模式之后,若确定当前第一仿真点与上一第一仿真点的输入信号不相同,则所述控制所述计时器周期性产生所述第二仿真点,包括:

16、控制所述计时器根据关系式t2=n*t+t1得到产生所述第二仿真点的时间点;其中,t2为产生所述第二仿真点的时间点,n≥1且为正整数,t为所述计时器自身设定的产生所述第二仿真点的周期,t1为在所述休眠模式之前所述计时器产生的最后一个所述第二仿真点的时间点。

17、可选的,所述硬件描述语言包括verilog-ams建模语言。

18、可选的,在各个所述第一仿真点所插入的触发事件的类型不同或者部分相同,各个所述第二仿真点所插入的触发事件的类型相同。

19、本申请提供的一种电路仿真验证装置,包括:

20、创建模块,用于采用硬件描述语言为电路器件创建仿真模型,所述仿真模型设有计时器和若干第一仿真点,所述计时器用于产生第二仿真点;

21、获取模块,用于获取仿真验证过程中当前第一仿真点与上一第一仿真点的输入信号;

22、判断模块,用于判断当前第一仿真点与上一第一仿真点的输入信号是否相同;

23、控制模块,用于在当前第一仿真点与上一第一仿真点的输入信号不相同时控制所述计时器周期性产生所述第二仿真点;以及,在当前第一仿真点与上一第一仿真点的输入信号相同时控制所述仿真模型进入休眠模式,在所述休眠模式下控制所述计时器停止产生所述第二仿真点;

24、插入模块,用于在所述第二仿真点插入触发事件。

25、本申请提供的一种电子设备,包括:

26、处理器;

27、用于存储所述处理器可执行指令的存储器;

28、其中,所述处理器被配置为执行所述指令以实现如上任一项电路仿真验证方法对应的步骤。

29、本申请提供的一种存储介质,存储有计算机程序,所述计算机程序被处理器执行时实现如上任一项电路仿真验证方法对应的步骤。

30、如上所述,本申请在仿真模型进入休眠模式时,计时器停止产生第二仿真点,从而可以降低仿真点的个数,有利于保持提高仿真速度,能够缩短包括含有高频触发时钟事件(即timer事件)的集成电路的仿真验证周期,进而加快整个集成电路的设计迭代,有助于集成电路尽早开始流片生产。

31、另外,电路器件未设有激励源,在仿真验证过程中,仿真模型的输入信号保持不变,因此输出信号保持不变,因而仿真精度也可以得到保证。

技术特征:

1.一种电路仿真验证方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述输入信号包括电压、电流、频率及功率中的至少一种。

3.根据权利要求1所述的方法,其特征在于,所述电路器件未设有激励源,在仿真验证过程中,所述仿真模型的输入信号保持不变时输出信号保持不变。

4.根据权利要求3所述的方法,其特征在于,

5.根据权利要求1所述的方法,其特征在于,在所述休眠模式之后,若确定当前第一仿真点与上一第一仿真点的输入信号不相同,

6.根据权利要求1至5中任一项所述的方法,其特征在于,所述硬件描述语言包括verilog-ams建模语言。

7.根据权利要求1所述的方法,其特征在于,在各个所述第一仿真点所插入的触发事件的类型不同或者部分相同,各个所述第二仿真点所插入的触发事件的类型相同。

8.一种电路仿真验证装置,其特征在于,所述装置包括:

9.一种电子设备,其特征在于,所述电子设备包括:

10.一种存储介质,其特征在于,存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求1至7中任一项所述的电路仿真验证方法。

技术总结

本申请公开了一种电路仿真验证方法及装置、电子设备、存储介质。所述方法包括:采用硬件描述语言,例如Verilog‑AMS建模语言,为电路器件创建仿真模型,所述仿真模型设有计时器和若干第一仿真点,计时器用于产生第二仿真点;获取仿真验证过程中当前第一仿真点与上一第一仿真点的输入信号;判断当前第一仿真点与上一第一仿真点的输入信号是否相同;若否,则控制计时器周期性产生第二仿真点;若是,则控制仿真模型进入休眠模式,在休眠模式下计时器停止产生第二仿真点。本申请可以在保证仿真精度的同时,降低仿真点的个数,并具有较高的仿真速度。

技术研发人员:宋宇,贾海洋,方君

受保护的技术使用者:上海概伦电子股份有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!