电路超图确定方法、装置、计算机设备及存储介质与流程

本发明涉及fpga,具体涉及电路超图确定方法、装置、计算机设备及存储介质。

背景技术:

1、fpga(field programmable gate array,现场可编程门阵列)芯片是一种在制造后可以配置电路功能的芯片。配置fpga芯片的电路功能需要经过综合、布局、布线等一系列流程,其中布局是指将原始电路中的基本逻辑单元映射到fpga芯片上相应元器件上的过程。

2、在布局阶段,考虑到原始电路中的逻辑单元在布局时通常设置有对应的约束条件,例如,位置约束,连接关系约束等,在将原始电路映射到fpga芯片上时需要满足约束条件才可以使得电路功能正常运行。因此,在进行映射前,首先要将原始电路建模成超图(超图中的超边允许经过多个顶点,可以更好的描述原始电路中逻辑单元之间的连接关系),并通过布局算法对该超图进行求解,以得到符合该原始电路约束条件的解。然而,在相关的技术方案中,由于根据原始电路建模得到的超图往往较为复杂,约束条件较多,从而导致布局算法的求解难度显著增加,在降低求解效率的同时,降低了所求得的解的质量。

技术实现思路

1、有鉴于此,本发明提供了一种电路超图确定方法、装置、计算机设备及存储介质,以解决在相关的技术方案中,由于布局算法约束条件较多导致求解难度显著增加且求解效率降低的问题。

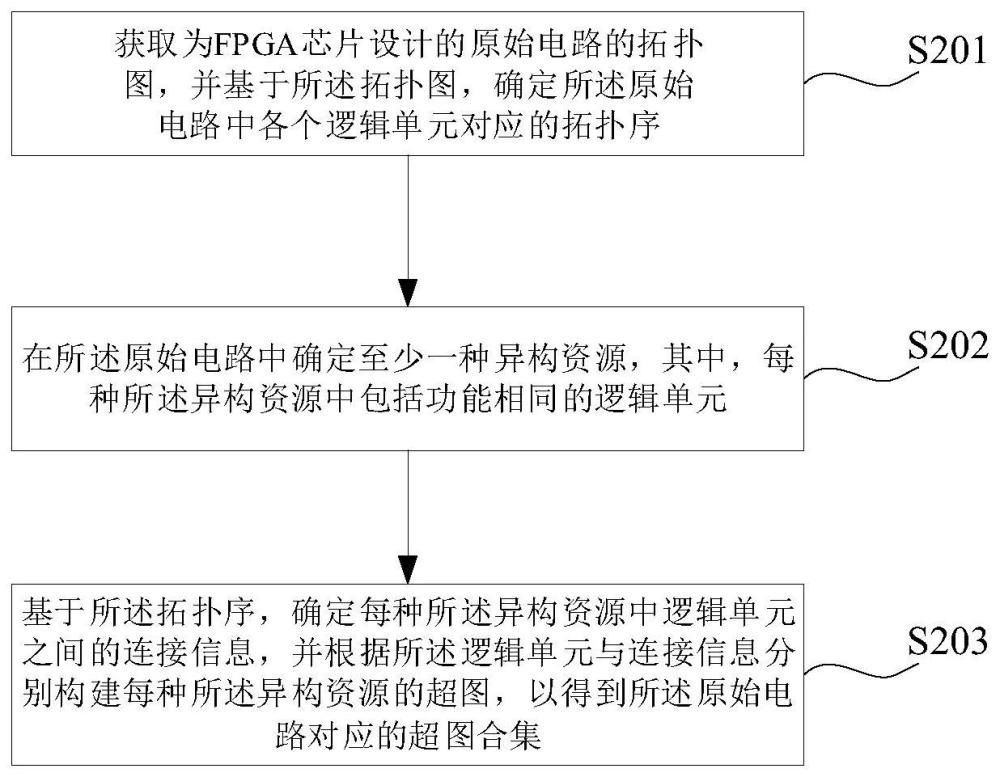

2、第一方面,本发明提供了一种电路超图确定方法,该方法包括:

3、获取为fpga芯片设计的原始电路的拓扑图,并基于该拓扑图,确定该原始电路中各个逻辑单元对应的拓扑序;

4、在该原始电路中确定至少一种异构资源,其中,每种该异构资源中包括功能相同的逻辑单元;

5、基于该拓扑序,确定每种该异构资源中逻辑单元之间的连接信息,并根据该逻辑单元与连接信息分别构建每种该异构资源的超图,以得到该原始电路对应的超图合集。

6、本实施例提供的电路超图确定方法,首先可以获取为fpga芯片设计的原始电路的拓扑图,并基于该拓扑图,确定原始电路中各个逻辑单元对应的拓扑序,然后,可以在原始电路中确定至少一种异构资源,并基于上述拓扑序,确定每种异构资源中逻辑单元之间的连接信息,并根据逻辑单元与连接信息分别构建每种异构资源的超图,以得到原始电路对应的超图合集,从而降低了每张超图的复杂度。同时,应理解的是,在布局算法在进行求解时,通常会为不同种类的异构资源分别求解,因此,在本实施例中可以分别构建每种异构资源的超图,从而在针对每张超图进行求解时减少了约束条件,降低了布局算法的求解难度。另外,由于不同种异构资源对应的超图之间不存在耦合关系,因此可以对超图合集进行并行运算,进一步提高了求解效率,同时提高了求解质量。

7、在一种可选的实施方式中,上述基于该拓扑序,确定每种该异构资源中逻辑单元之间的连接信息,包括:

8、在该每种异构资源中确定逻辑单元之间的超边,其中,该超边为连接该逻辑单元的边;

9、基于该超边对应的逻辑单元的拓扑序,确定该超边的权重;

10、根据该逻辑单元的超边与超边对应的权重确定该连接信息。

11、在本实施例中,可以基于超边对应的拓扑序确定该超边的权重,并根据该逻辑单元的超边与超边对应的权重确定连接信息,从而可以基于该权重获取逻辑单元之间的路径长度,便于后续通过布局算法进行求解。

12、在一种可选的实施方式中,上述基于该超边对应的逻辑单元的拓扑序,确定该超边的权重,包括:

13、确定该超边对应的逻辑单元在所述拓扑序对应的逻辑层数之间的第一差值,并将该第一差值确定为该超边的权重,其中,所述逻辑层数用于指示所述拓扑图中逻辑单元的深度值;

14、或者,在所述超边对应的逻辑单元之间在所述拓扑图中存在多条路径时,在所述多条路径中确定最短路径,并将所述最短路径的长度值确定为所述超边的权重。

15、在本实施例中,可以通过超边对应的逻辑单元的逻辑层数之间的第一差值确定该超边的权重,从而在根据超图进行布局算法的求解时,基于权重获取超边对应的路径的长度,以满足计算约束条件的需求。

16、在一种可选的实施方式中,上述方法还包括:

17、在确定该超边的权重后,在所述拓扑序对应的逻辑层数中确定最大层数值;

18、基于该最大层数值与该权重的第二差值,调整该超边的权重。

19、在本实施例中,考虑到在部分布局算法中,需要超边的权重和逻辑单元之间的距离成反比,因此,可以在确定出超边的权重之后对该权重进行调整,以满足布局算法的需求,从而提高本实施例的适用范围。

20、在一种可选的实施方式中,上述在该每种异构资源中确定逻辑单元之间的超边,包括:

21、基于该拓扑图,确定该异构资源中相邻逻辑单元对应的待确认超边;

22、对该待确认超边中经过预设逻辑单元的待确认超边进行去重操作,得到该相邻逻辑单元对应的超边。

23、在本实施例中,考虑到在实际使用场景中,拓扑图的结构往往较为复杂,因此在基于拓扑图确定超图时,顶点组的顶点之间可能存在多条重复的待确认超边,基于此,可以对待确认超边进行去重操作,以对超图的结构进行简化,降低后续基于超图进行布局算法求解的难度。

24、在一种可选的实施方式中,上述预设逻辑单元包括以下至少之一:与该相邻逻辑单元同类的逻辑单元、该原始电路中确定位置的逻辑单元。

25、在一种可选的实施方式中,上述基于该拓扑图,确定该原始电路中各个逻辑单元对应的拓扑序,包括:

26、在该拓扑图中确定满足入度条件的起始节点,并将该起始节点的逻辑层数设置为起始值,其中,所述逻辑层数用于指示所述拓扑图中逻辑单元的深度值;

27、基于所述原始电路中各个逻辑单元在所述拓扑图中对应节点的深度值与所述起始值的差值,设置各个所述逻辑节点对应的拓扑序。

28、在本实施例中,可以首先在拓扑图中确定起始节点,并为该起始节点设置起始值,然后,可以计算各个节点的深度值与该起始值的差值,以得到每个节点对应的拓扑序,从而为基于该拓扑序确定每种异构资源中逻辑单元之间的连接信息的实施例提供了基础。

29、第二方面,本发明提供了一种电路超图确定装置,该装置包括:

30、第一确定模块,用于获取为fpga芯片设计的原始电路的拓扑图,并基于该拓扑图,确定该原始电路中各个逻辑单元对应的拓扑序;

31、第二确定模块,用于在该原始电路中确定至少一种异构资源,其中,每种该异构资源中包括功能相同的逻辑单元;

32、超图构建模块,用于基于该拓扑序,确定每种该异构资源中逻辑单元之间的连接信息,并根据该逻辑单元与连接信息分别构建每种该异构资源的超图,以得到该原始电路对应的超图合集。

33、第三方面,本发明提供了一种计算机设备,包括:存储器和处理器,存储器和处理器之间互相通信连接,存储器中存储有计算机指令,处理器通过执行计算机指令,从而执行上述第一方面或其对应的任一实施方式的电路超图确定方法。

34、第四方面,本发明提供了一种计算机可读存储介质,该计算机可读存储介质上存储有计算机指令,计算机指令用于使计算机执行上述第一方面或其对应的任一实施方式的电路超图确定方法。

- 还没有人留言评论。精彩留言会获得点赞!