一种内存性能测试方法、装置、设备及存储介质与流程

本技术涉及计算机,特别涉及一种内存性能测试方法、装置、设备及存储介质。

背景技术:

1、随着数据中心规模的不断扩大,数据中心网络也在向更大带宽、更低时延的方向演进,并且各种网络应用和网络协议也层出不穷,使得满足高带宽、低时延和扩展性强的网络需求的智能网卡(smart nic,smart network interface card)得到了广泛的应用。目前,基于“soc+fpga”类型的智能网卡应用广泛,该类型网卡不仅可以直接部署到生产环境中,还可以用于网卡芯片开发的前期验证,并在满足高效处理网络数据的同时,还具备强大的可扩展性和灵活性,其中智能网卡内部的soc(system on chip,系统级芯片)主要用于网络控制平面的卸载,以及对智能网卡内各种硬件资源的管理,而内部的fpga(fieldprogrammable gate array,现场可编程逻辑门阵列)提供了接近专用asic(applicationspecific integrated circuit,专用集成电路)的报文处理能力,同时还具备软硬件可编程的能力。

2、为了提供更高效的网络i/o(输入/输出,input/output)处理能力以及满足大量数据处理的需求,智能网卡内部的fpga需要下挂多路ddr(即ddr sdram,double data ratesynchronous dynamic random-access memory,双倍速率同步动态随机存储器)从而进行大量数据的缓存和传输,并参与大规模网络数据的高速并行处理,进而提高智能网卡的数据处理和传输的效率。

3、然而,随着网络通信技术的快速发展,对数据传输的速度和稳定性的要求也越来越高,由于内存的读写效率会影响系统的处理速度,因此ddr的可用性及稳定性成为智能网卡可靠运行的重要因素;另外,智能网卡内部的ddr在实际使用中,由于存在因焊接不良、颗粒故障、布线不合理等现象,因此会导致内存性能下降,故在智能网卡的生产过程及用户业务现场,需要对fpga下挂的ddr进行功能及压力测试,用于验证ddr的可用性及可靠性。

4、然而,对于智能网卡内fpga下挂的ddr的可用性及可靠性的验证,目前fpga下没有开源的工具对ddr进行压测,并且在智能网卡的开发阶段,在对ddr相关的问题进行测试时,需要依赖高速示波器或者专用fpga调试器对ddr进行问题分析,问题分析效率低、定位周期长,并且需要人工参与,从而增加了人工成本;再者,由于受到检测设备及检测手段的限制,在网卡批量生产阶段,无法充分暴露ddr的异常问题,从而无法在产测阶段验证ddr长期运行的可靠性;另外,在用户业务现场,针对ddr异常的问题,缺乏简单易用的诊断工具做快速问题分析,使得设备故障排查和问题解决变得困难,从而影响了用户业务的部署。

5、综上,目前的ddr测试方法虽然能从多个环节测试智能网卡内ddr的可用性,但测试效率低,发起一次ddr全面测试的技术门槛较高,时间成本较大,且由于测试设备操作复杂、价格较高,故在智能网卡的开发、测试、生产、运维及故障诊断等环节,不能快速的对ddr相关的问题进行分析。因此在智能网卡的开发、生产阶段以及业务现场,均需要一种易执行的方法对fpga下挂的ddr进行性能测试,以对ddr进行实时监控和故障定位。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种内存性能测试方法、装置、设备及存储介质,能够减少对专用工具的依赖,简化内存性能测试的流程,进而提高性能测试效率以及问题定位效率,并节省了人力成本和时间成本。其具体方案如下:

2、第一方面,本技术公开了一种内存性能测试方法,应用于内部集成有现场可编程逻辑门阵列和系统级芯片的智能网卡,所述现场可编程逻辑门阵列预先挂载多路双倍速率同步动态随机存储器,并在内部预先集成双倍速率同步动态随机存储器的控制器,并且通过pcie总线与所述系统级芯片连接;其中,所述方法包括:

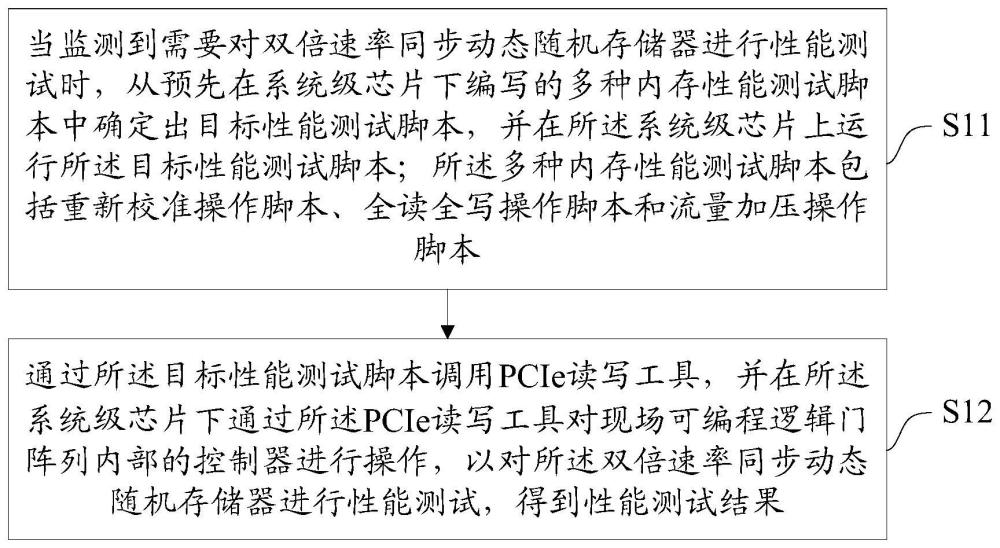

3、当监测到需要对所述双倍速率同步动态随机存储器进行性能测试时,从预先在所述系统级芯片下编写的多种内存性能测试脚本中确定出目标性能测试脚本,并在所述系统级芯片上运行所述目标性能测试脚本;所述多种内存性能测试脚本包括重新校准操作脚本、全读全写操作脚本和流量加压操作脚本;

4、通过所述目标性能测试脚本调用pcie读写工具,并在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,以对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果。

5、可选的,所述从预先在所述系统级芯片下编写的多种内存性能测试脚本中确定出目标性能测试脚本之前,还包括:

6、在所述现场可编程逻辑门阵列进行知识产权核例化的过程中,确定位于所述控制器内的各种控制寄存器;

7、将各种所述控制寄存器配置到所述pcie总线的访问内存地址空间上,并对所述系统级芯片进行上电重启,以获取所述控制器的操作权;

8、在所述系统级芯片下编写用于对所述双倍速率同步动态随机存储器进行重新校准操作、全读全写操作和流量加压操作的脚本,得到所述多种内存性能测试脚本。

9、可选的,所述的内存性能测试方法,还包括:

10、在所述系统级芯片上电初始化的过程中,将各种所述控制寄存器映射到所述系统级芯片的pcie的基地址寄存器空间上。

11、可选的,所述在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,以对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果,包括:

12、在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行重新校准操作,以对各路所述双倍速率同步动态随机存储器进行数据完整性测试,得到包含各种校准参数的性能测试结果;其中,所述重新校准操作包括所述控制器与所述双倍速率同步动态随机存储器内的时钟对齐操作、写数据级联延迟校准操作、读数据级联延迟校准操作、读写预加重系数调整操作;

13、相应的,所述对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果之后,还包括:

14、将所述性能测试结果中的所述各种校准参数保存至所述现场可编程逻辑门阵列的非易失性存储器中,以便在下次上电时直接对所述非易失性存储器中的所述各种校准参数进行加载。

15、可选的,所述在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,以对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果,包括:

16、在所述系统级芯片下通过所述pcie读写工具并以字节为单位对位于所述现场可编程逻辑门阵列内部的所述控制器的全地址空间的数据位进行多轮读写操作,以对各路所述双倍速率同步动态随机存储器的全地址空间的读写功能进行测试,得到性能测试结果。

17、可选的,所述在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,以对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果,包括:

18、在所述系统级芯片下通过所述pcie读写工具并利用位于所述现场可编程逻辑门阵列中的流量发生器,对所述现场可编程逻辑门阵列内部的所述控制器进行流量加压操作,以按照预设脚本运行时间对所述双倍速率同步动态随机存储器进行长时间随机地址的读写流量压力测试,得到性能测试结果。

19、可选的,所述的内存性能测试方法,还包括:

20、通过所述现场可编程逻辑门阵列中的所述控制器例化生成引脚接口,得到目标引脚接口;

21、通过所述目标引脚接口在所述现场可编程逻辑门阵列的外围连接所述多路双倍速率同步动态随机存储器。

22、第二方面,本技术公开了一种内存性能测试装置,应用于内部集成有现场可编程逻辑门阵列和系统级芯片的智能网卡,所述现场可编程逻辑门阵列预先挂载多路双倍速率同步动态随机存储器,并在内部预先集成双倍速率同步动态随机存储器的控制器,并且通过pcie总线与所述系统级芯片连接,包括:

23、脚本确定模块,用于当监测到需要对所述双倍速率同步动态随机存储器进行性能测试时,从预先在所述系统级芯片下编写的多种内存性能测试脚本中确定出目标性能测试脚本;所述多种内存性能测试脚本包括重新校准操作脚本、全读全写操作脚本和流量加压操作脚本;

24、脚本运行模块,用于在所述系统级芯片上运行所述目标性能测试脚本;

25、工具调用模块,用于通过所述目标性能测试脚本调用pcie读写工具;

26、性能测试模块,用于在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,以对所述双倍速率同步动态随机存储器进行性能测试,得到性能测试结果。

27、第三方面,本技术公开了一种电子设备,包括处理器和存储器;其中,所述处理器执行所述存储器中保存的计算机程序时实现前述的内存性能测试方法。

28、第四方面,本技术公开了一种计算机可读存储介质,用于存储计算机程序;其中,所述计算机程序被处理器执行时实现前述的内存性能测试方法。

29、可见,本技术应用于内部集成有现场可编程逻辑门阵列和系统级芯片的智能网卡,所述现场可编程逻辑门阵列预先挂载多路双倍速率同步动态随机存储器,并在内部预先集成双倍速率同步动态随机存储器的控制器,并且通过pcie总线与所述系统级芯片连接,当监测到需要对所述双倍速率同步动态随机存储器进行性能测试时,先从预先在所述系统级芯片下编写的多种内存性能测试脚本中确定出目标性能测试脚本,并在所述系统级芯片上运行所述目标性能测试脚本;所述多种内存性能测试脚本包括重新校准操作脚本、全读全写操作脚本和流量加压操作脚本;然后通过所述目标性能测试脚本调用pcie读写工具,并在所述系统级芯片下通过所述pcie读写工具对所述现场可编程逻辑门阵列内部的所述控制器进行操作,从而对所述双倍速率同步动态随机存储器进行性能测试得到性能测试结果。本技术预先在智能网卡的soc中编写了包含重新校准操作脚本、全读全写操作脚本和流量加压操作脚本的多种内存性能测试脚本,这样一来,在监测到需要对智能网卡中的ddr进行性能测试时,便可以直接从上述多种内存性能测试脚本中选择出相应的目标性能测试脚本,然后通过目标性能测试脚本调用pcie读写工具,并在soc下通过上述读写工具对现场可编程逻辑门阵列内的控制器进行相应的操作控制,从而实现了ddr性能测试,本技术通过在智能网卡内部的soc上运行测试脚本的方式实现对fpga挂载的ddr的性能测试,能够减少对专用工具的依赖,简化内存性能测试的流程,进而提高性能测试效率以及问题定位效率,并节省了人力成本和时间成本。

- 还没有人留言评论。精彩留言会获得点赞!