一种应用于可编程逻辑器件高速JTAG编程的电路和装置的制作方法

本发明涉及可编程逻辑器件的jtag编程电路设计领域,具体涉及灵活且高速的jtag编程电路设计方法,尤其涉及一种应用于可编程逻辑器件高速jtag编程的电路和装置。

背景技术:

1、传统的可编程逻辑器件在开发前期调试的时候采用jtag连接器进行编程,此时jtag连接器一般通过连接官方下载器后再连接到配置电脑上的集成开发软件来实现编程。大多数情况下官方下载器要考虑适用于大部分客户的板子,为了编程的可靠性对jtag的编程速率进行了限制,例如赛灵思的官方下载器platform cable usb ii(mode:dlc10)在配合集成开发软件vivado使用的时候,最高限速到12mbps。随着高资源率和高管脚数量的高端可编程器件的大规模采用,编程的.bit文件越来越大,可达百mbyte级别,编程所需的时间也越来越长。前期调试中如果设计需要经常修改,那么反复编程会非常耗时;有时,当设计中一个jtag连接器级联了多片大资源高端可编程器件后,编程时间往往要翻多倍,这个问题会越发突显严重,可编程逻辑器件需要按顺序级联,一条链要先后对器件进行烧写,12mbps的速率会非常费时;而且,当需要多片可编程逻辑器件上同时运行物理层测试程序,实时观察收发两端数据统计或者进一步地进行调试,一条速率受限的jtag链往往无法实现。因此需要一种更简单且实用的电路设计来实现更快的编程、更简洁的机框面板设计、更灵活的多片间物理层调测和两种编程方式的之间更简单的切换。

技术实现思路

1、本发明的目的在于针对现有技术的不足,提供一种应用于可编程逻辑器件高速jtag编程的电路和装置。

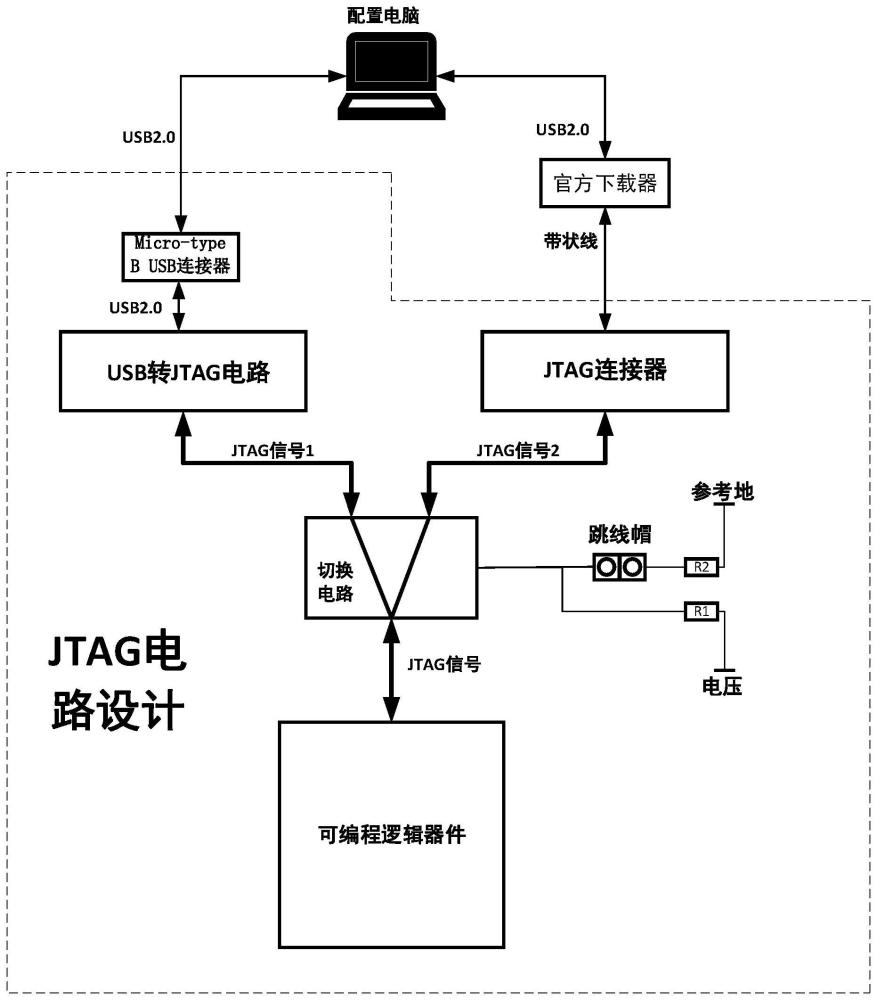

2、本发明的目的是通过以下技术方案来实现的:本发明实施例第一方面提供了一种应用于可编程逻辑器件高速jtag编程的电路,所述电路包括usb连接器、usb转jtag电路、jtag连接器、切换电路和可编程逻辑器件,其中,所述usb转jtag电路通过usb连接器直接连接外部配置电脑;所述jtag连接器通过官方下载器连接外部配置电脑;所述usb转jtag电路的输出端和所述jtag连接器的输出端连接在所述切换电路的输入端,所述切换电路的输出端连接可编程逻辑器件;

3、通过切换电路选择usb转jtag电路输出的第一jtag信号或jtag连接器输出的第二jtag信号,以实现可编程逻辑器件的两种jtag编程方式的选择;通过配置usb转jtag电路中的寄存器以使外部配置电脑上的集成开发软件识别且获取大于等于官方指定编程速率最大值的两倍的jtag编程频率。

4、进一步地,所述通过配置usb转jtag电路中的寄存器以使外部配置电脑上的集成开发软件识别且获取大于等于官方指定编程速率最大值的两倍的jtag编程频率,具体包括:

5、在进行可编程逻辑器件程序烧写前,首先通过外部配置电脑上的ft_prog软件对usb转jtag电路中的寄存器进行一次性编程,烧录客户指定的单板信息、串号、端口功能用途和电流驱动值,然后在外部配置电脑上的集成开发软件vivado中输入tcl命令,使得集成开发软件vivado的硬件管理员组件自动识别该usb转jtag电路且给予访问授权,并获取大于等于官方指定编程速率最大值的两倍的jtag编程频率。

6、进一步地,所述通过切换电路选择usb转jtag电路输出的第一jtag信号或jtag连接器输出的第二jtag信号,以实现可编程逻辑器件的两种jtag编程方式的选择,具体包括:

7、切换电路的选择信号通过电阻r1进行了上拉,通过电阻r2进行跳线可选择的下拉,其中电阻r1的一端与电源电压相连,电阻r1的另一端与切换电路的选择信号相连,且同时与跳线帽相连,电阻r2的一端与参考地相连,电阻r2的另一端与跳线帽相连;当插入跳线帽时,切换电路的选择信号被拉低,切换电路的选择信号选择jtag连接器输出的第二jtag信号,以选择可编程逻辑器件的传统jtag编程方式;当不插入跳线帽时,切换电路的选择信号被拉高,切换电路的选择信号选择usb转jtag电路输出的第一jtag信号,以选择可编程逻辑器件的集成开发软件jtag编程方式。

8、进一步地,所述usb连接器包括type-a usb连接器、type-b usb连接器、micro-type busb连接器、mini-a usb连接器和mini-b usb连接器。

9、进一步地,所述可编程逻辑器件包括数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚;

10、所述usb转jtag电路的输出端包括数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚;

11、所述jtag连接器的输出端包括数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚;

12、所述切换电路的输入端和输出端均包括数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚;

13、所述usb转jtag电路的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚分别与切换电路输入端的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚一一对应连接,所述jtag连接器的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚分别与切换电路输入端的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚一一对应连接,所述切换电路输出端的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚分别与可编程逻辑器件的数据输入引脚、时钟输入引脚、模式选择输入引脚和数据输出引脚一一对应连接。

14、进一步地,所述可编程逻辑器件包括fpga芯片和cpld芯片。

15、进一步地,所述可编程逻辑器件的数量为多个,所述jtag连接器的数量为多个,所述切换电路的数量为多个。

16、进一步地,所述jtag连接器的数量与所述可编程逻辑器件的数量相等,所述切换电路的数量与所述可编程逻辑器件的数量相等。

17、进一步地,所述电路还包括驱动电路,所述驱动电路用于复制tck引脚和tms引脚对应的tck信号和tms信号。

18、本发明实施例第二方面提供了一种应用于可编程逻辑器件高速jtag编程的装置,包括承载板以及位于所述承载板上或者通过接口与所述承载板连接的上述的应用于可编程逻辑器件高速jtag编程的电路。

19、本发明的有益效果是,本发明可以通过切换电路灵活切换,既可以单独对板上每片大资源高端可编程逻辑器件进行jtag编程,也可以对多片级联起来的可编程逻辑器件进行顺序高速jtag编程;把多片可编程逻辑器件级联起来编程只需要一个micro-type b usb接口,简洁了机框面板的设计;同时,可以规避一些官方下载器带来的编程速率的限制,获得官方指定最高编程速率两倍以上的速率,特别适用于板内有多片可编程逻辑器件的情况,节省了系统调试时间;而且可以在多片可编程逻辑器件上同时运行物理层测试程序,实时观察收发两端数据统计或者进一步地进行调试;当这种多片级联的高速jtag链不通或者存在烧写问题时,也可以立马切换为传统下载器加载程序的模式,单独对每一片可编程器件进行程序烧写,确保编程不受影响。

- 还没有人留言评论。精彩留言会获得点赞!